Since the end of 2012, it has been possible to use ARM 64-bit Fast models to run code compiled for the new ARMv8 architecture by emulating a 64-bit ARM processor inside an Intel / AMD processor. ARM fast models are not the only “free” option anymore, as Imperas has released OVPsim 20140430 with open source models for ARM Cortex A53 and Cortex A57 cores. OVPsim is a virtual platform that’s available free of charge for personal usage. The simulator itself (OVPsim) is closed source, but processor, peripheral and platform models are released under the Apache License version 2.0.

OVP models of the ARM Cortex-A53 and Cortex-A57 are fully instruction accurate models, and you can use them for personal with an additional free license key, but if you want to make use of advanced features such as TrustZone and hardware virtualization you’ll need to purchase a commercial version (Imperas Developer or Imperas Advanced Multicore Software Development Kit).

OVPsim is available both for Windows and Linux, and I’ve given it a try in Ubuntu 14.04. The whole process is not as enjoyable as it could be due to registration and licensing requirements. Here’s what I’ve managed to do so far:

- Register or login to ovpworld.org

- Go to the Download page to download OVPsim Fast Simulator, the ARM Cortex A models and OVPsim_demo_arm_ARMv8 (single and multi- core demos for Cortex A53 and Cortex A57). You can also find other models, demos, as well as documentation there. You may especially want to download Imperas_Installation_and_Getting_Started.pdf.

- Install OVPsim

12chmod +x OVPsim.20140430.0.Linux32.exe./OVPsim.20140430.0.Linux32.exe

You’ll need a accept the software license to complete the installation. I will create Imperas.20140430 directory by default. - Configure OVPsim

12345source Imperas.20140430/bin/setup.shsetupImperas -m32 <INSTALLATION_PATH>/Imperas.20140430export IMPERAS_RUNTIME=OVPsimexport PATH=${PATH}:$IMPERAS_HOME/bin/$IMPERAS_ARCHexport LD_LIBRARY_PATH=${LD_LIBRARY_PATH}:$IMPERAS_HOME/bin/$IMPERAS_ARCH:$IMPERAS_HOME/lib/$IMPERAS_ARCH/External/lib - Get a license key. The hostid & hostname correspond to your MAC address and hostname that you can retrieve with /sbin/ifconfig and hostname commands. Email to [email protected] to request a license key for ARMv8 models.

- Copy the license keys, you’ve received to $IMPERAS_HOME/OVPsim.lic

- Install the ARM models (Cortex A, R, and

12chmod +x arm.model.20140430.0.Linux32.exe./arm.model.20140430.0.Linux32.exe

Accept the license agreement to go ahead with the installation. - Install the Cortex A53 and A57 demos (binary and source code).

12chmod +x OVPsim_demo_arm_ARMv8.20140430.0.Linux32.exe./OVPsim_demo_arm_ARMv8.20140430.0.Linux32.exe

You’ll need to accept another license agreement… - You should now be able to go to Imperas.20140430/Demo, and go inside OVPsim_arm_Cortex-A53, OVPsim_manycore_arm_Cortex-A53, OVPsim_arm_Cortex-A57, and OVPsim_manycore_arm_Cortex-A57 to try various demos: linpack, dhrystone, peakSpeed2, fibonacci, and more.

At the time of writing, I’ve only received my standard OVPsim license key, and I’m still waiting for my ARMv8 license key, so I haven’t been able to try it successfully yet, and I get the following error:

Fatal (LIC) No such feature exists.

Feature: IMP_MODEL_ARMv8

License path: /home/jaufranc/edev/sandbox/Imperas.20140430/OVPsim.lic:

FLEXnet Licensing error:-5,357

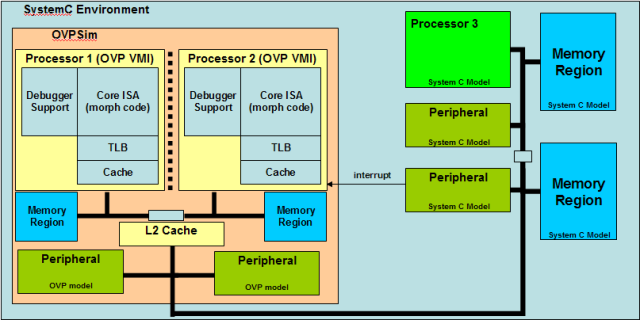

If you want to check out the source, it is located in Imperas.20140430/ImperasLib/source/arm.ovpworld.org/ for processors, peripherals, and platforms. It’s a bunch of hpp files written using SystemC TLM 2, a set of C+ classes or macros used for virtual platform modeling.

You can find more information about OVPSim and various models on ovpworld.org.

[Update: I’ve finally received the IMP_MODEL_ARMv8 license by email, and tried a few tests from a single core Cortex A53 to a 24-core Cortex A57 model. I’ve also been told the Linux kernel can’t boot on the model right now, but will for next release

Here’s the output for Dhrystone test on a single Cortex A53 core:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 |

Imperas.20140430/Demo/OVPsim_arm_Cortex-A53$ ./RUN_dhrystone.sh Warning (LIC_EXP) License feature 'IMP_OVPSIM_20140430' will expire in 29 days OVPsim (32-Bit) v20140430.0 Open Virtual Platform simulator from www.OVPworld.org. Copyright (c) 2005-2014 Imperas Software Ltd. Contains Imperas Proprietary Information. Licensed Software, All Rights Reserved. Visit www.IMPERAS.com for multicore debug, verification and analysis solutions. OVPsim started: Sun May 11 10:19:27 2014 Info (ICM_AL) Found attribute symbol 'modelAttrs' in file '/home/jaufranc/edev/sandbox/Imperas.20140430/lib/Linux32/ImperasLib/arm.ovpworld.org/semihosting/armAngel/1.0/model.so' Info (ICM_AL) Found attribute symbol 'modelAttrs' in file '/home/jaufranc/edev/sandbox/Imperas.20140430/lib/Linux32/ImperasLib/arm.ovpworld.org/processor/arm/1.0/model.so' Warning (LIC_EXP) License feature 'IMP_MODEL_ARMv8' will expire in 29 days Info (OR_OF) Target 'cpu0' has object file read from 'dhrystone.AARCH64.elf' Info (OR_PH) Program Header size load addr file offset Info (OR_PD) 000000000001887c 0000000080000000 0000000000010000 Info (OR_PD) 00000000000037a2 0000000080028880 0000000000028880 Info (OR_PD) 0000000000000024 0000000080000000 0000000000010000 Info (ARM_ANGEL_HEAP_INFO) ARM Angel heap_base=0xc0000000 heap_limit=0xdfffffffx stack_pointer=0xfffffffcx stack_limit0xe0000000x Dhrystone Benchmark, Version 2.1 (Language: C) Program compiled without 'register' attribute Please give the number of runs through the benchmark: Execution starts, 5000000 runs through Dhrystone Execution ends Final values of the variables used in the benchmark: Int_Glob: 5 should be: 5 Bool_Glob: 1 should be: 1 Ch_1_Glob: A should be: A Ch_2_Glob: B should be: B Arr_1_Glob[8]: 7 should be: 7 Arr_2_Glob[8][7]: 5000010 should be: Number_Of_Runs + 10 Ptr_Glob-> should be: (implementation-dependent) Discr: 0 should be: 0 Enum_Comp: 2 should be: 2 Int_Comp: 17 should be: 17 Str_Comp: DHRYSTONE PROGRAM, SOME STRING should be: DHRYSTONE PROGRAM, SOME STRING Next_Ptr_Glob-> should be: (implementation-dependent), same as above Discr: 0 should be: 0 Enum_Comp: 2 should be: 1 Int_Comp: 18 should be: 18 Str_Comp: DHRYSTONE PROGRAM, SOME STRING should be: DHRYSTONE PROGRAM, SOME STRING Int_1_Loc: 5 should be: 5 Int_2_Loc: 13 should be: 13 Int_3_Loc: 7 should be: 7 Enum_Loc: 1 should be: 1 Str_1_Loc: DHRYSTONE PROGRAM, 1'ST STRING should be: DHRYSTONE PROGRAM, 1'ST STRING Str_2_Loc: DHRYSTONE PROGRAM, 2'ND STRING should be: DHRYSTONE PROGRAM, 2'ND STRING Begin Time = 0 End Time = 0 Measured time too small to obtain meaningful results Please increase number of runs Info (ARM_ANGEL_REPORT_EXCEPTION) Process exception (unknown) *** simulation interrupted Info Info --------------------------------------------------- Info CPU 'cpu0_CPU0' STATISTICS Info Type : arm (Cortex-A53MPx1) Info Nominal MIPS : 100 Info Final program counter : 0x80015c5c Info Simulated instructions: 5,755,061,326 Info Simulated MIPS : 408.2 Info --------------------------------------------------- Info Info --------------------------------------------------- Info SIMULATION TIME STATISTICS Info Simulated time : 57.55 seconds Info User time : 13.94 seconds Info System time : 0.16 seconds Info Elapsed time : 14.12 seconds Info Real time ratio : 4.08x faster Info --------------------------------------------------- OVPsim finished: Sun May 11 10:19:41 2014 OVPsim (32-Bit) v20140430.0 Open Virtual Platform simulator from www.OVPworld.org. Visit www.IMPERAS.com for multicore debug, verification and analysis solutions. |

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

I’ve received the license key, and tried some tests and updated the post accordingly.

About Linux kernel boot in ARMv8 model:

“We are currently working through an initial Linux Kernel boot using the ARMv8 model and during this process we have fixed some issues that are found in the model that is currently released on the OVPWorld website. This means

that the model currently released should not be used for Kernel development.”