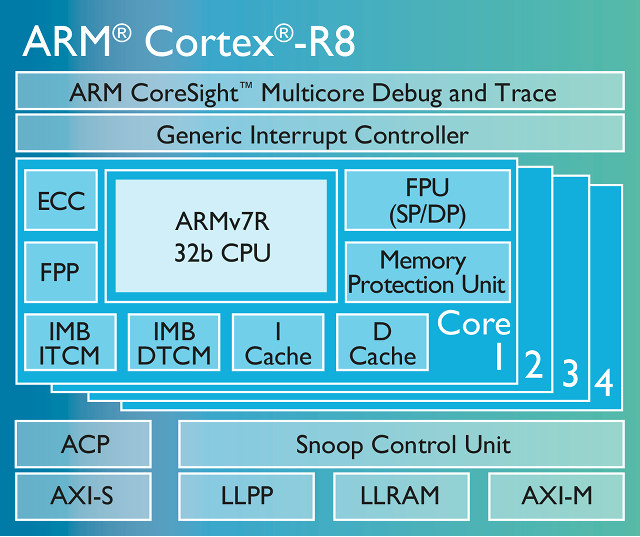

ARM Cortex-A processor may get all the media buzz as they are found in popular consumer devices such as smartphones, but ARM also provides Cortex-R processors with real-time capabilities that are found in cars, hard drives, and other embedded systems requiring high reliability, fault tolerance, and deterministic real-time responses. The company has just announced Cortex-R8 real-time core that should double the performance of Cortex-R7 core, and targeting mainly storage devices such as SSDs and HDDs, as well as next generation LTE and 5G modems.

- Microarchitecture – 11-stage pipeline with instruction pre-fetch, branch prediction, superscalar and out of order execution, register renaming, parallel execution paths for load-store, MAC, shift-ALU, divide and floating-point. Also features a hardware divider and is software compatible with the ARM9, ARM11, Cortex-R4, Cortex-R5 and Cortex-R7 embedded processors.

- Instruction Set – ARMv7-R architecture with Thumb-2 and Thumb. Support for DSP extensions, as well as an optional floating point unit, with either single or single/double precision.

- Cache controllers – Harvard memory architecture with optional integrated Instruction and Data cache controllers. Cache sizes configurable from 4 to 64KB. Cache lines are write-back.

- Tightly-Coupled Memories – Optional Tightly-Coupled Memory interfaces are for highly deterministic or low-latency applications that may not respond well to caching (e.g. instruction code for interrupt service routines and data that requires intense processing). Instruction and/or data TCMs. TCM size can be up to 1MB.

- Interrupt interface – Standard interrupt, IRQ, non-maskable fast interrupt, FIQ, inputs are provided together with a fully integrated Generic Interrupt Controller (GIC) supporting complex priority-based interrupt handling.

- Memory Protection Unit (MPU) – Optional MPU configures attributes for 12, 16, 20 or 24 regions, each with resolution down to 32 Bytes.

- Floating-Point Unit (FPU) – Optional FPU implements the ARM Vector Floating Point architecture VFPv3 with 16 double-precision registers, compliant with IEEE754. There is support for two FPU options.

- ECC – Optional single-bit error correction and two-bit error detection for cache and/or TCM memories and all interfaces with ECC bits.

- Master AMBA AXI bus – 64-bit AMBA AXI bus master for Level-2 memory access.

- Low latency memory port – A 64-bit AMBA AXI master port designed specifically to connect to local memory. This local memory provides many of the benefits of TCM and in addition can be slower and lower power and also easily shared between coherent peripherals and the Cortex-R8 processor cores.

- Low Latency Peripheral Port (LLPP) – A shared dedicated 32-bit AMBA AXI port to integrate latency-sensitive peripherals more tightly with the processor.

- Fast Path Port (FPP) – An optional per core dedicated 32-bit AMBA AXI port to integrate latency-sensitive peripherals more tightly with the processor.

- Accelerator Coherency Port (ACP) – A 64-bit AMBA AXI slave port to enable coherency between the processor(s) and external intelligent peripherals such as DMA controllers, Ethernet or Flexray interfaces.

- Slave AXI bus – Optional 64-bit AMBA AXI bus slave port allows DMA masters to access the TCMs for high speed streaming of data in and out of the processor.

- Debug – Debug Access Port is provided. Its functionality can be extended using CoreSight SoC-400.

- Trace – An interface suitable for connection to CoreSight Embedded Trace Module is present.

- Multi-core – Single, dual, triple or quad processor configurations for flexible performance in either Asymetric Multiprocessing Mode (AMP) or in Symetric Multiprocessing Mode (SMP). In addition it can be configured with a redundant Cortex-R8 CPU in lock-step for fault tolerant/fault detecting dependable systems.

- Performance

- 1.5GHz+ frequencies supported

- 2.50 DMIPS/MHz with Dhrystone “ground rules”, 2.90 / 3.77 DMIPS/MHz with optimizations

- 4.35 CoreMark/MHz

- Efficiency – As low as 46 DMIPS/mW

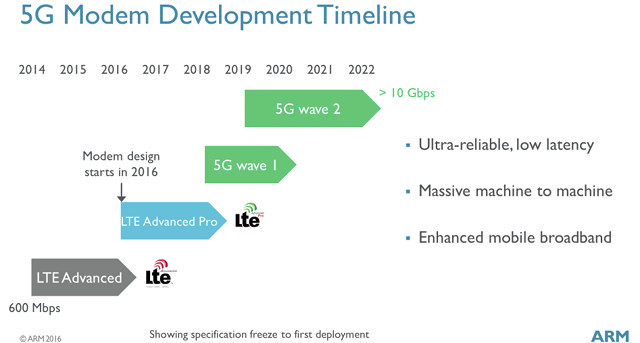

Several companies have already started working on SoC featuring Cortex-R8 processors, with mass storage devices based on the new solutions likely to become available later this year. Cortex-R8 based modem will be launched as LTE Advanced Pro and 5G standards roll-out starting respectively in 2017/2018 and 2019/2020. More details can be found in ARM Cortex-R8 product page, and ARM blog.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress