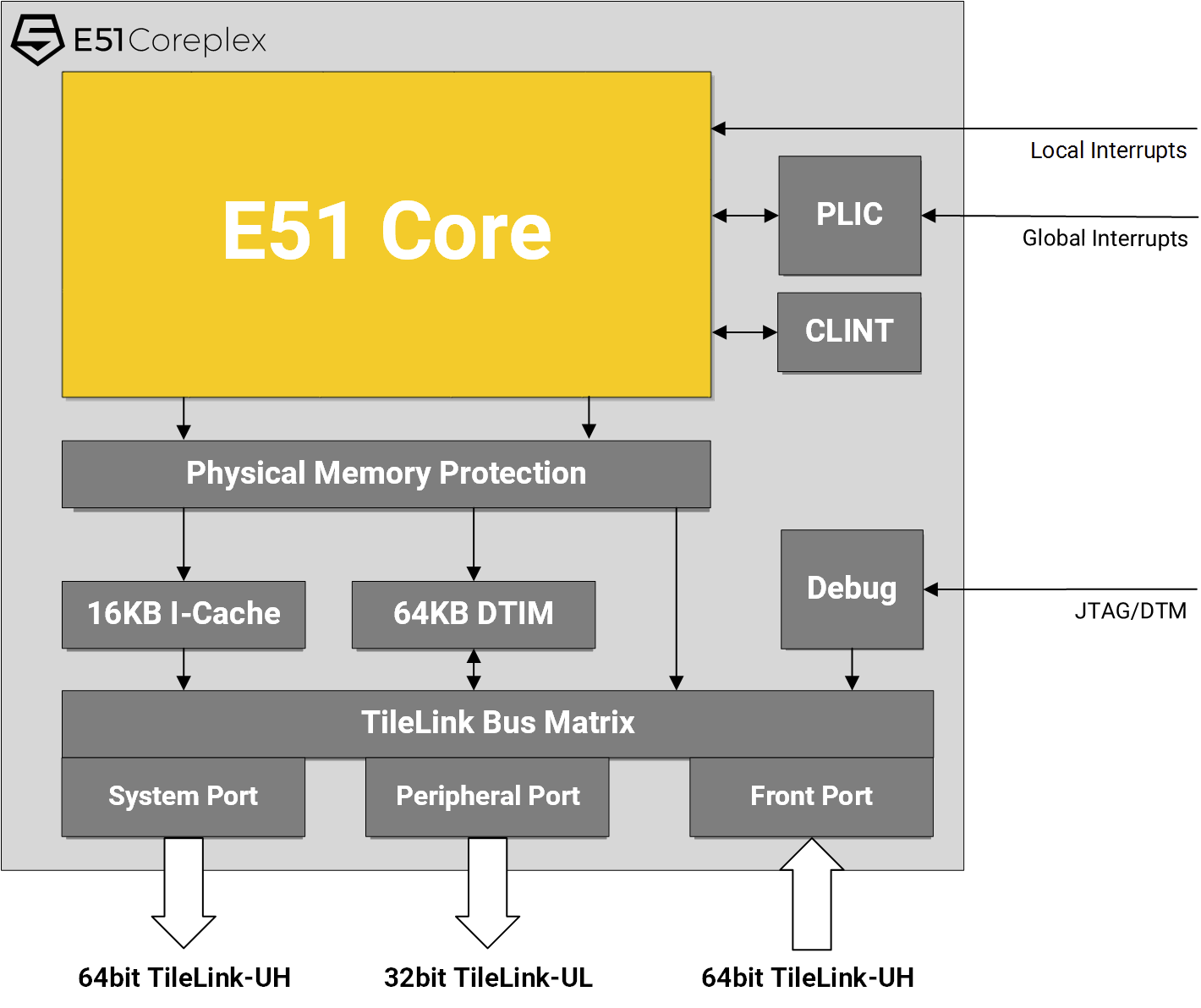

SiFive unveiled their Freedom U500 and E500 open source RISC-V SoCs last year, and a little layer launched HiFive1 Arduino compatible development board based on SiFive Freedom E310 processor. The company has now launched their non-open source Coreplex IP also based on RISC-V ISA with the 32-bit E31 Coreplex and 64-bit E51 Coreplex, and explained details about pricing. Some of the key features of the processors are listed below: E31 Coreplex 32-bit RV32IMAC core @ 900 to 1.5 GHz (with 28nm process) Advanced Memory Subsystem – 16KB, 2-way Instruction Cache, Instruction Tightly Integrated Memory (ITIM) option, up to 64KB Data Tightly Integrated Memory (DTIM) support Up to 16 local interrupts with vectored addresses Performance – 1.61 DMIPS/MHz ; 2.73 Coremark/MHz Power Consumption 28nm HPC process – Core only: 150 DMIPS/mW ; Coreplex: 41 DMIPS/mW 55nm LP process – Core only: 95 DMIPS/mW; Coreplex: 16 DMIPS/mW Applications: Edge Computing, Smart IoT […]

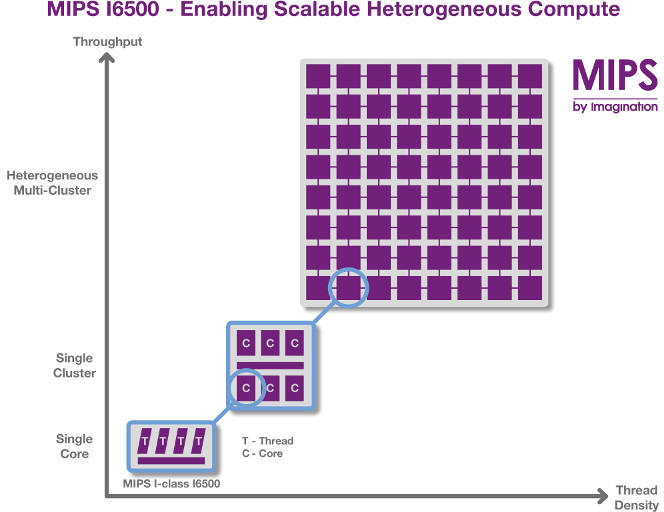

Imagination Technologies Announces MIPS Warrior I-class I6500 Heterogeneous CPU with up to 384 Cores

Imagination has just unveiled the successor of MIPS I6400 64-Bit Warrior Core with MIPS Warrior I-class I6500 heterogeneous CPU supporting up to 64 cluster, with up to 6 cores each (384 cores max), themselves up to 4 thread (1536 max), combining with IOCU (IO coherence units), and external IP such as PowerVR GPU or other hardware accelerators. The main features of MIPS I6400 processor are listed as follows: Heterogeneous Inside – In a single cluster, designers can optimize power consumption with the ability to configure each CPU with different combinations of threads, different cache sizes, different frequencies, and even different voltage levels. Heterogeneous Outside – The latest MIPS Coherence Manager with an AMBA ACE interface to popular ACE coherent fabric solutions such as those from Arteris and Netspeed lets designers mix on a chip configurations of processing clusters – including PowerVR GPUs or other accelerators – for high system […]

Amlogic S905L Processor Drops VP9 Codec, TS Inputs for Tuners, and the Camera Interface

[Update: I’ve received updated documentation for Amlogic S905X too, and the main differences are only the lack of VP9 codec, and HDMI 2.0b interface] Amlogic has apparently decided to launch yet another quad core Cortex A53 processor with Amlogic S905L, which appears to be based on Amlogic S905X with built-in stereo audio codec and 10/100M Ethernet PHY & MAC, HDR support, but without VP9 codec, camera interface, nor TS inputs, so it looks like a cost-down version purely designed for OTT/IP TV boxes. The document I have is dated June 2016, before the 1.5 GHz “limit” was discovered on Amlogic processors, and the maximum frequency is rated @ 2.0 GHz in the document. Amlogic S905L specifications (based on S905L Quick Referent Manual): CPU – Quad core ARM Cortex-A53 CPU up to 2GHz (DVFS) with Neon and Crypto extensions, unified L2 cache 3D GPU – Penta-core ARM Mali-450 GPU up to […]

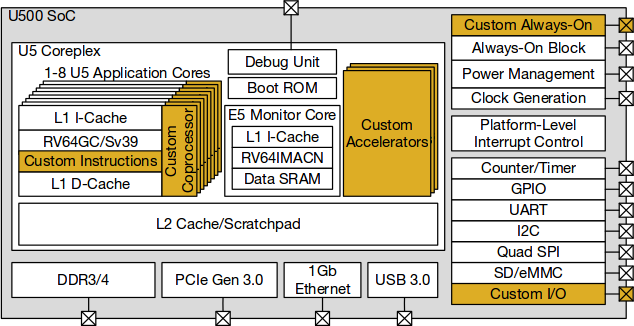

SiFive Introduces Freedom U500 and E500 Open Source RISC-V SoCs

Open source used to be a software thing, with the hardware design being kept secret for fear of being copied, but companies such as Texas Instruments realized that from a silicon vendor perspective it would make perfect sense to release open source hardware designs with full schematics, Gerber files and SoM, to allow smaller companies and hobbyists, as well as the education market, normally not having the options to go through standard sales channels and the FAE (Field Application Engineer) support, to experiment with the platform and potentially come up with commercial products. That’s exactly what they did with the Beagleboard community, but there’s still an element that’s closed source, albeit documented: the processor itself. But this could change soon, as SiFive, a startup founded by the creators of the free and open RISC-V architecture, has announced two open source SoCs with Freedom U500 processor and Freedom E300 micro-controller. Freedom […]

FOSDEM 2015 Schedule – January 31 – February 1 2015

FOSDEM (Free and Open Source Software Developers’ European Meeting) takes place every year during the first week-end of February. This year the developer-oriented event expects to bring over 5000 geeks to share ideas and collaborate on open source projects. Contrary to most other events, it’s free to attend, and you don’t even need to register, just show up. FOSDEM 2015 will take place on January 31- February 1 in Brussels. There will be 551 sessions divided into 5 keynotes, 40 lightning talks, 6 certification exams, and with the bulk being developer rooms and main tracks, divided into 7 main tracks this year: Languages, Performance, Time, Typesetting, Hardware, Security and Miscellaneous. I’m not going to attend, but it’s still interested to see what will be talked about, and I’ve concocted my own little virtual program out of the main tracks and developers’ rooms. There’s a few minutes overlap between some talks […]

LG NUCLUN Octa-core ARM SoC Powers G3 Screen Smartphone

LG has been making mobile devices since 1997, has entered the smartphone market in 2010, and they’ve now decided to foray into mobile SoC, with their very first SoC being an octa-core Cortex A15/A7 processor called NUCLUN, and found in their latest G3 Screen smartphone running Android 4.4.4. Details about NUCLUN processor are sparse, but the company did provide some specifications for LG G3 Screen smartphone: SoC – LG NUCLUN (LG7111) Octa-Core big.LITTLE processor with four ARM Cortex A15 cores @ 1.5GHz, four ARM Cortex A7 cores @ 1.2GHz. System Memory – 2GB RAM Storage – 32GB eMMC + MicroSD slot Display – 5.9″ Full HD IPS touchscreen Camera – 13MP OIS+ rear camera, 2.1MP front-facing camera Network – LTE-A Cat.6 for up to 225Mbps download speed. Battery – 3,000mAh Dimensions – 157.8x 81.8x 9.5mm Weight – 182g The phone, also codenamed as LG Liger F490L, F490K or F490S (depending […]

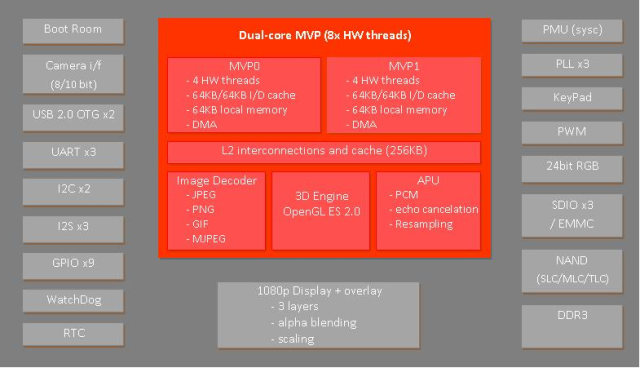

ICube MVP SoCs Combine CPU and GPU into a Single Unified Processing Unit (UPU)

ICube is a fabless semiconductor company developing SoCs featuring a Unified Processing Unit (UPU) that takes care of the tasks usually handle by separate CPU and GPU on typical SoCs. The UPUs are based on MVP (Multi-thread Virtual Pipeline) instruction set architecture, and are themselves called MVP cores. The company has now two SoCs based on UPU MVP cores: IC3128 and IC3228. IC3128 is a single core / 4 thread SoC, and IC3228 is a dual MVP core / 8 threads SoC. Let’s have a look at IC3228 technical specifications: CPU function 4-way simultaneous multi-threading (SMT) in each core Symmetric-multi-processing (SMP), dual MVP cores 64KB I-cache, 64KB D-cache and 64KB local memory in each core, 256KB shared L2 cache Homogeneous parallel programs Support Pthread, OpenMP GPU function Data parallel, Task parallel, and/or Function parallel computing Multi-standard media processor Programmable unified shader Support OpenGL ES 2.0 70 million triangles / sec, […]

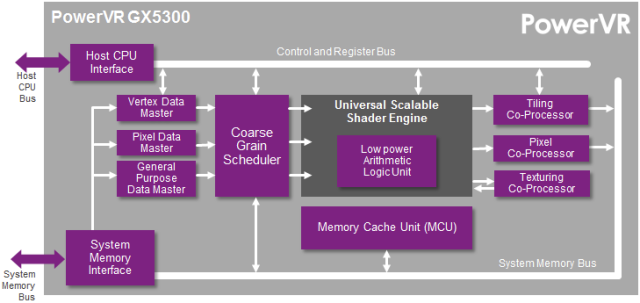

Imagination Technologies Unveils Low Power Low Footprint PowerVR GX5300 GPU for Wearables

Up to now most wearables are based on MCU solutions or derived from mobile platforms, which may either not provide the advanced features required by users, or consume too much power and take more space than needed. With Ineda Dhanush and Mediatek Aster, we’ve already seen silicon vendors design wearables SoCs, and now Imagination Technologies has just announced PowerVR GX5300 GPU targeting wearables with support for OpenGL ES 2.0, 480p to 720p resolution, and using 0.55mm2 silicon area based on 28nm process. PowerVR GX5300 GPU will be support Android, Android Wear, and Linux based operation systems, and according to the company has the following key features: Unified shaders – The TBDR graphics architecture offers unified shaders where vertex, pixel and GPU compute resources are scaled simultaneously. Low power and high precision graphics – All PowerVR GPUs offer a mix of low (FP16) and high precision (FP32) rendering and implement the […]