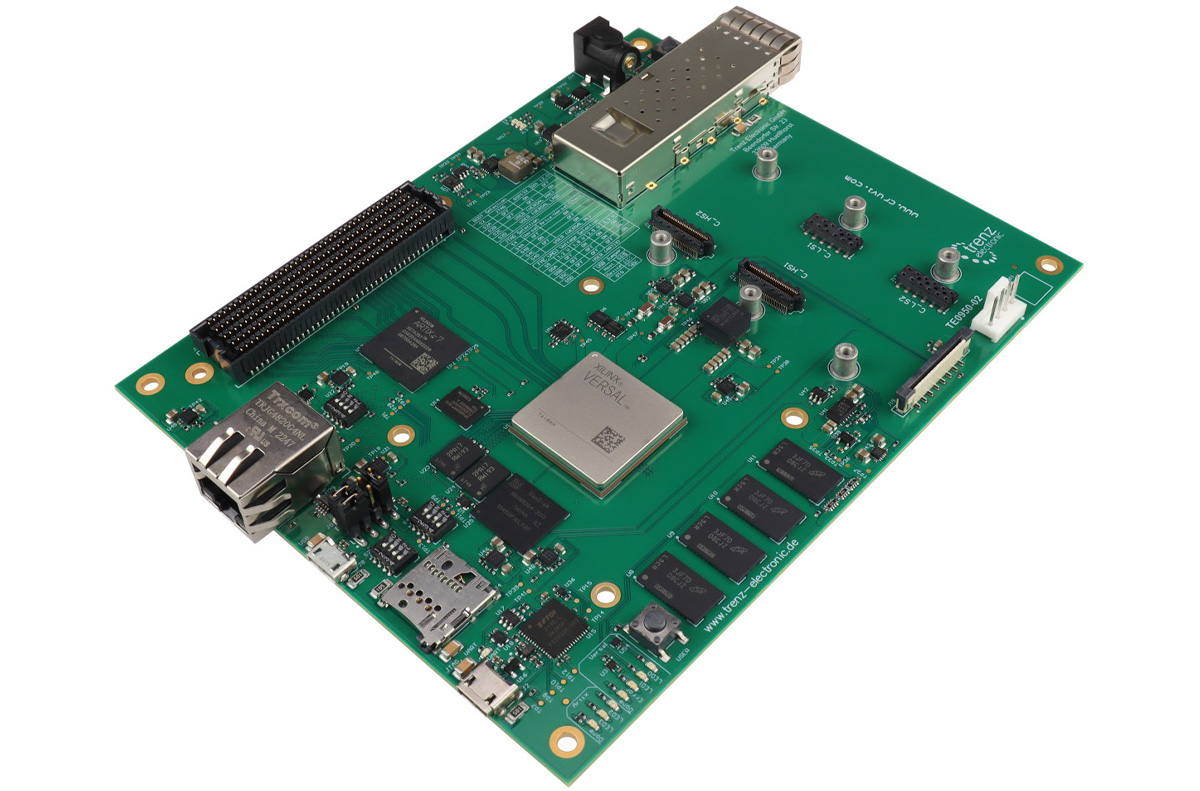

Trenz Electronic recently announced the TE0950-03-EGBE21A an evaluation board with AMD Versal AI Edge XCVE2302-1LSESFVA784 SoC FPGA. This board features 8 GB of DDR4 SDRAM and 128 MB of SPI Flash (as the primary boot option), a microSD card slot, a 32 GB eMMC flash (secondary boot), and an EEPROM with a MAC address. Additionally, the board supports a range of VE-series devices, such as VE2002, VE2102, VE2202, VE2302, and VM1102, enhancing its application versatility. The AMD Versal is a family of adaptive compute acceleration platforms (ACAPs) designed by AMD. Following its acquisition of Xilinx, it integrates CPU, GPU, and FPGA technologies along with dedicated software support to create a highly flexible development environment. Trenz Electronic VE2302 Evaluation Board Specifications: SoC – AMD Versal AI Edge XCVE2302-1LSESFVA784, A784 package, compatible with multiple VE-series devices RAM – 8 GB DDR4 SDRAM Storage 128 MB SPI Flash (primary boot option) MicroSD card […]

$349 AMD Kria KR260 Robotics Starter Kit takes on NVIDIA Jetson AGX Xavier devkit

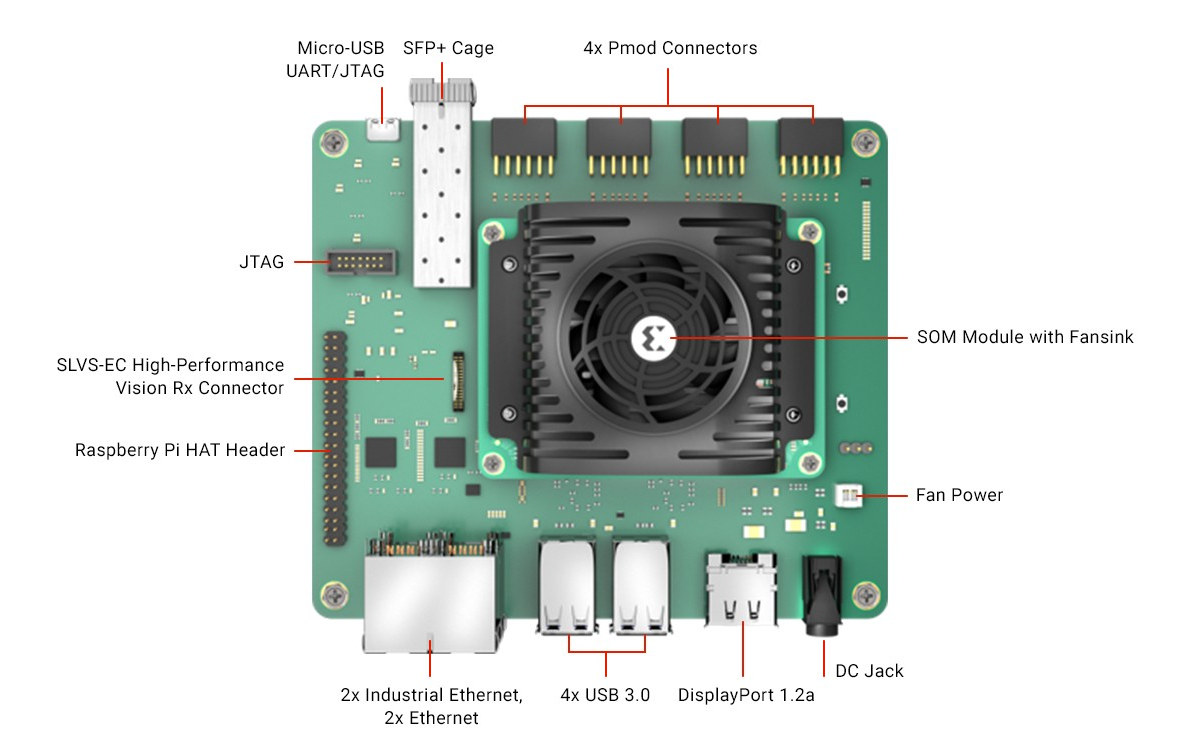

AMD Xilinx Kria KR260 Robotics Starter Kit features the Kria K26 Zynq UltraScale+ XCK26 FPGA MPSoC system-on-module (SoM) introduced last year together with the Kria KV260 Vision AI Starter Kit. Designed as a development platform for robotics and industrial applications, the KR260 is said to deliver nearly 5x productivity gain, up to 8x better performance per watt and 3.5x lower latency compared to Nvidia Jetson AGX Xavier or Jetson Nano kits. We’ll have a better look at the details below. Kria KR260 Robotics Starter Kit specifications: SoM – Kria K26 module with: MPSoC – Xilinx Zynq Ultrascale+ custom-built XCK26 with quad-core Arm Cortex-A53 processor up to 1.5GHz, dual-core Arm Cortex-R5F real-time processor up to 600MHz, Mali-400 MP2 GPU up to 667MHz, 4Kp60 VPU, 26.6Mb On-Chip SRAM, 256K logic cells, 1,248 DSP slices, 144 Block RAM blocks, 64 UltraRAM blocks System Memory – 4GB 64-bit DDR4 (non-ECC) Storage – 512 Mbit […]

Xilinx announces Versal AI Edge Series with Cortex-A72 & R5 cores, FPGA fabric

Edge AI solves the latency and security issues through on-device AI acceleration for optimal computations at a low power supply. Xilinx announces its Versal AI Edge Series which is 4th member of the Adaptive Compute Acceleration Platform (ACAP) family. The versal series consists of seven models ranging from VE2002 to VE2802 with the processor fabrication on 7 nm silicon technology. Talking more about ACAP, it is a platform that provides a combined essence of a processor and FPGA. The processing features efficient memory and I/Os, whereas programmable arrays allow logical control over the hardware. Also, as Xilinx specializes in FPGA products, the additional support of computational features makes the ACAP hardware even more flexible and dynamic. The Versal AI Edge series features different types of engines for specific functionalities in terms of adaptable, scalar, and intelligent engines. The seven processor models vary with respect to engine and platform specifications. However, […]

Xilinx Introduces Kria K26 SoM and vision AI devkit based on Zynq Ultrascale+ XCK26 FPGA MPSoC

Silicon vendors will usually focus on chip design, and provide an expensive evaluation kit to early customers, leaving the design of cost-optimized boards and system-on-modules to embedded systems companies. But Xilinx has decided to enter the latter market with the Kria portfolio of adaptive system-on-modules (SOMs) and production-ready small form factor embedded boards starting with Kria K26 SoM powered by Zynq UltraScale+ XCK26 FPGA MPSoC with a quad-core Arm Cortex-A53 processor, up to 250 thousand logic cells, and a H.264/265 video codec designed for Edge AI applications, as well as computer vision development kit. Kria K26 System-on-Module Kria K26 module specifications: MPSoC – Xilinx Zynq Ultrascale+ custom-built XCK26 with quad-core Arm Cortex-A53 processor up to 1.5GHz, dual-core Arm Cortex-R5F real-time processor up to 600MHz, Mali-400 MP2 GPU up to 667MHz, 4Kp60 VPU, 26.6Mb On-Chip SRAM, 256K logic cells, 1,248 DSP slices System Memory – 4GB 64-bit DDR4 (non-ECC) Storage – […]

Xilinx open sources Vitis HLS FPGA tool (Front-end only)

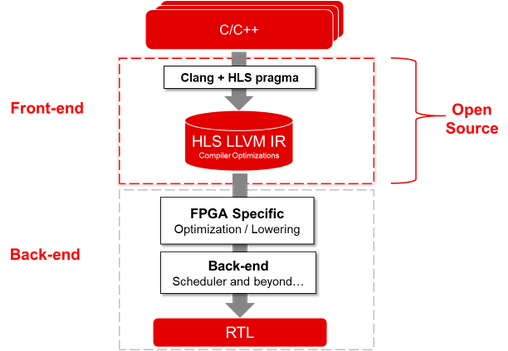

While there are some open-source programs for FPGA development such as Symbiflow or Yosys, FPGA vendors usually only provide closed-source programs for developers wanting to work on their chips. But Xilinx has recently made a move to fulfill its “commitment to supporting open-source initiatives for developers and researchers” with the release of the source code of Vitis HLS Front-End. What is Vitis HLS exactly? Before we look at the source code release, we may want to know what Vitis HLS does exactly. The company describes it as a high-level synthesis (HLS) tool that allows C, C++, and OpenCL functions to become hardwired onto the device logic fabric and RAM/DSP blocks. It implements hardware kernels in the Vitis application acceleration development flow, and to use C/C++ code for developing RTL IP for FPGA designs in the company’s Vivado Design Suite. Vitis HLS design flow goes as follows: Compile, simulate, and debug […]

MYIR launches FZ5 EdgeBoard AI Box for AI on the Edge

Back in July of this year (2020), MYRI technology announced the MYIR’s FZ3 deep learning accelerator card powered by the Xilinx Zynq UltraScale+ ZU3EG Arm FPGA MPSoC and it is capable of delivering up to 1.2TOPS computing power. With only a few months since that launch, MYRI technology is now announcing another two related sets of products – FZ5 EdgeBoard AI Box and the FZ5 Card. The FZ5 EdgeBoard AI Box is an AI-focused computing platform that is based on the FZ5 AI Accelerator card which is an upgrade of the FZ3 card. The FZ5 looks more like a single board computer than an actual computing card. The FZ5 accelerator is powered by the Xilinx Zynq UltraScale+ ZU5EV MPSoC which features a 1.5 GHz quad-core Arm Cortex-A53 64-bit application processor, a 600MHz dual-core real-time Arm Cortex-R5 processor, a Mali400 embedded GPU and is capable of delivering up to 2.4 TFLOPS as compared […]

Linaro Connect SF 2017 Welcome Keynote – New Members, Achievements, the Future of Open Source, and More…

Linaro Connect San Francisco 2017 is now taking place until September 29, and it all started yesterday with the Welcome Keynote by George Grey, Linaro CEO discussing the various achievements since the last Linaro Connect in Budapest, and providing an insight to the future work to be done by the organization. The video is available on YouTube (embedded below), and since I watched it, I’ll provide a summary of what was discussed: Welcoming New Members – Kylin (China developed FreeBSD operating systems) joined LEG (Enterprise Group), NXP added LHG (Home Group) membership, and Xilinx joined LITE (IoT and Embedded). Achievements OPTEE open portable trusted environment execution more commonly integrated into products. Details at optee.org. LEG 17.08 ERP release based on Linux 4.12, Debian 8.9 with UEFI, ACPI, DPDK, Bigtop, Hadoop, etc… LITE group has been involved in Zephyr 1.9 release, notably contributing to LwM2M stack More projects to be found […]

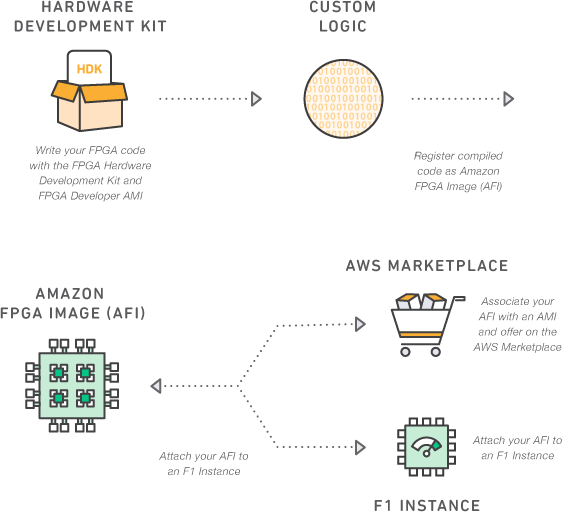

Amazon EC2 F1 Instances Put Xilinx Virtex Ultrascale+ FPGA Boards into the Cloud

We’ve covered several board and modules based on Xilinx Zynq Ultrascale+ MPSoC such as the AXIOM Board and Trenz TE0808 SoM, both featuring ZU9EG MPSoC, with systems selling for several thousands dollars. But I’ve been informed you may not need to purchase a board to use Virtex UltraScale+ FPGAs, which are different from Zynq UltraScale+ since they lack the ARM CPU & GPU and normally feature a more capable FPGA, as last November, Amazon launched a developer preview of F1 instances giving access to this type of hardware from their cloud. That’s the FPGA hardware you’ll be able to access from one F1 instance: Xilinx UltraScale+ VU9P manufactured using a 16 nm process. 64 GB of ECC-protected memory on a 288-bit wide bus (four DDR4 channels). Dedicated PCIe x16 interface to the CPU. Approximately 2.5 million logic elements. Approximately 6,800 Digital Signal Processing (DSP) engines. Virtual JTAG interface for debugging. […]