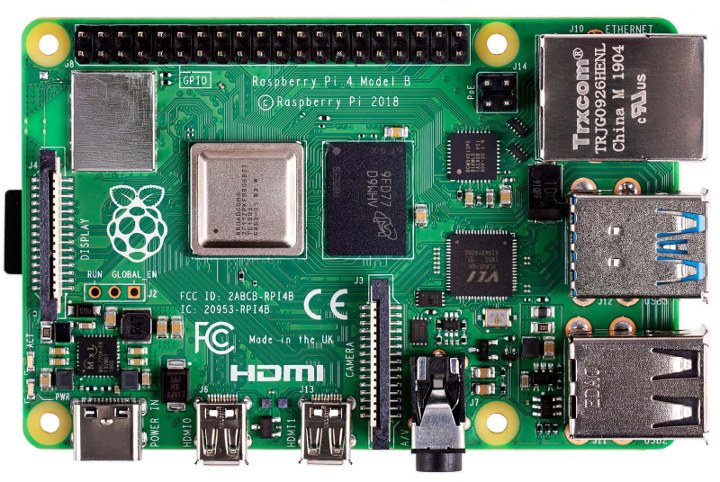

Long expected, the Raspberry Pi 4 model B has finally launched, and it should not disappoint with a much more powerful Broadcom BCM2711 quad-core Cortex-A72 processor clocked at up to 1.5 GHz, 1 to 4GB LPDDR4, 4K H.265 video decoding and output support, a proper Gigabit Ethernet port, as well as USB 3.0 and 2.0 ports.

Raspberry Pi 4 comes with all those extra features, but the form factor remains the same, and importantly the price is still $35 for the version with 1GB RAM, making Raspberry Pi alternatives suddenly much less interesting.

Raspberry Pi 4 specifications:

-

- SoC – Broadcom BCM2711 quad-core Cortex-A72 (ARMv8) @ 1.5GHz with VideoCore VI GPU supporting OpenGL ES 3.0 graphics

- System Memory – 1GB, 2GB or 4GB LPDDR4

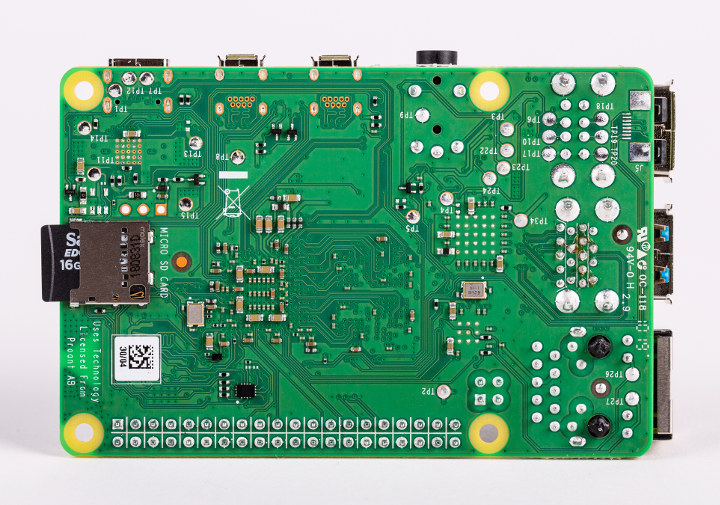

- Storage – microSD card slot

- Video Output & Display I/F

- 2x micro HDMI ports up to 4Kp60 (Currently 1080p60 max. in dual-display configuration, although 2x 4Kp30 is being worked on)

- 3.5mm AV port with composite video (and stereo audio)

- 2-lane MIPI DSI display port

- 2x micro HDMI ports up to 4Kp60 (Currently 1080p60 max. in dual-display configuration, although 2x 4Kp30 is being worked on)

- Video

- Decode – H.265 up to 4Kp60, H.264 up to 1080p60

- Encode – H.264 up to 1080p30

- Camera – 2-lane MIPI CSI camera port

- Audio – Stereo audio via AV port, digital audio via HDMI ports

- Connectivity

- True Gigabit Ethernet (RJ45)

- Dual band (2.4 GHz/5.0 GHz) 802.11b/g/n/ac WiFi 5

- Bluetooth 5.0 BLE

- USB – 2x USB 3.0 ports, 2x USB 2.0 ports.

- Expansion – Standard 40-pin GPIO header fully backward-compatible with previous Raspberry Pi boards

- Power Supply

- 5V DC via USB-C connector (minimum 3A )

- 5V DC via GPIO header (minimum 3A )

- Power over Ethernet (PoE) via optional PoE HAT

- Dimensions – 85 x 56 mm (same as other model B boards)

- Temperature Range – 0 – 50°C

Beside the “true” Gigabit Ethernet port, the good news for people interested in network storage applications is that the shared USB + Ethernet bandwidth is gone, as there’s a separate Gigabit Ethernet transceiver (BCM54213PE), and USB goes through a VIA VL805 PCIe to 4-port USB 3.0 host controller. The latter means BCM2711 comes with a PCIe interface giving the Raspberry Pi foundation some flexibility for future Raspberry Pi SBC’s.

There have been at least two hardware changes that have made the new board incompatible with existing Raspberry Pi cases:

- They swapped two USB ports and the Ethernet port to place the latter closer to the PoE header.

- They replaced the HDMI port with two micro HDMI ports

So a new case is needed, and here’s the official Raspberry Pi 4 enclosure.

The USB-C port should mean issues related to powering the board should mostly be a thing of the past, and the main downside I see from the announcement is that we’ll need to get micro HDMI cables or HDMI to micro HDMI adapters to connect Raspberry Pi 4 to HDMI TVs or monitors. Not a big issue.

The USB-C port should mean issues related to powering the board should mostly be a thing of the past, and the main downside I see from the announcement is that we’ll need to get micro HDMI cables or HDMI to micro HDMI adapters to connect Raspberry Pi 4 to HDMI TVs or monitors. Not a big issue.

Raspberry Pi 4 model B with 1GB RAM sells for the same $35 as the previous model, with the 2GB and 4GB RAM models are coming soon for respectively $45 and $55 with local variations due to taxes, shipping cost, and currency exchange. The board and accessories can be purchased online from Cytron, Element14, RS Components, or other online as well as local distributors.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

>The USB-C port should mean powering the board should mostly be a thing of the past,

USB-C == free dark space energy?

I think he was referring to the issues with many micro USB power supplies not delivering enough power to previous generation boards, as well as some power instability regardless if the power supply was up to scratch, depending on what you connected to the RPi boards.

LoL. Yes, that’s exactly what I meant. I’ve added a few missing words to the sentence.

@TLS

https://www.merriam-webster.com/dictionary/joke

Impressive spec for the money.

I’m curious how hot the new chip runs though, as I’ve heard down the grape vine that the SoC is still made at 28nm. This suggests that it might run quite hot. Not RK3399 hot, but maybe not too far off…

I just wish they’d come up with a better form factor…

It’s a shame they didn’t add eMMC support, even via a header like many other boards these days, but according to this, there’s SPI flash for the boot ROM – https://www.raspberrypi.org/documentation/hardware/raspberrypi/booteeprom.md

> https://www.raspberrypi.org/documentation/hardware/raspberrypi/booteeprom.md

Yeah, this confirms that the SoCs are simply incompatible. The stuff on the FAT partition is for the older RPi that will boot with ThreadX as primary OS, the new RPi seems to be a design where the ARM cores are now first class citizens and boot directly off the SPI flash. I want to get my hands on the new Raspbian Buster release to understand all the details…

Hmm… if I’ll ever redo an OMV image for RPi then it will be only compatible with 4 and above.

BTW . The mentioned SPI flash is for the second boot phase – afaik not for the initial boot.

Having an SPI flash seems like a huge departure from the old idea of having an unbrickable device that has all its writable storage on removable SD cards, which always seemed like both the biggest advantage (completely newbiew-proof) and disadvantage (most SD cards don’t survive being used as a writable rootfs for a long time), compared to the usual eMMC or raw NAND based boards.

They seem to implement a recovery mode where you need to put new EEPROM contents as file

recovery.binon the first FAT formatted partition on an SD card and then boot with this SD card inserted. Maybe the SoC can overwrite the EEPROM even in situations where the contents are corrupted?@tkaiser

It’s likely the boot rom (in the SoC itself, not the SPI one) can load binaries from SD just fine but it’s limited to whatever internal SRAM there is. If someone works out the DRAM init then it should be possible to have a u-boot SPL on the sdcard that loads u-boot proper.

It actually seems weird that they’ve added extra cost to their BOM instead of doing what every other ARM board does.

Yes, it has’t much changed with RP4, the old VC VPU is still there, it is booting first (independed form the eeprom) and (if there is a need) can write/rewrite the bootloader (bootcode.bin) to the external eeprom.

@michael

They say they are doing the dram init in whatever is loaded from the spi flash… Does that mean the contents of the spi flash are running on the VC or that the VC doesn’t have access to dram until it’s brought up?

The VPU does have access to the first 1 GB RAM. All (caching, Bus controller …) does work as before. Beside this the new bus master controllers (ARM,PCIe) are now 35-bit.

> the old VC VPU is still there, it is booting first (independed form the eeprom)

Seriously? This is still a ThreadX platform?

ThreadX was juts bought by Microsoft 🙂 : “ThreadX, developed and marketed by Express Logic of San Diego, California, United States, is a highly deterministic, embedded real-time operating system (RTOS) written mostly in the C (programming language). Express Logic was purchased for an undisclosed sum by Microsoft on April 18, 2019.[1]” https://en.wikipedia.org/wiki/ThreadX

Plus ThreadX is actually responsible to govern the CPU: “We cannot know everything the GPU is doing, but we do know some things that it is in charge of. The most relevant one for this discussion is that ThreadX monitors for undervoltage, which is a widespread issue as we will see next, and will underclock the CPU to prevent instructions failing and the CPU to hang, which results in people’s devices running at 600MHz instead of 1400MHz in the best case. This throttling starts happening at 4.65V and can also be triggered by temperature. Linux and its frequency governor still thinks that is happily running at full speed.” https://ownyourbits.com/2019/02/02/whats-wrong-with-the-raspberry-pi/

Around 80 degrees at full Load to be throttled. I read at tomshardware. So er nerd at least heatsink for this to be useful for many of us:)

80 C?

Yes 80ºC

Impressive, curios whether it’s software compatible (ThreadX). No new Raspbian available at the moment…

In this context, it means that it’s available now, not that it’s being discounted.

Yes, I came to the same conclusion and edited my comment. And found also out that a new Raspbian release is needed. Still curious what’s about ThreadX and whether the new BCM2711 needs the stuff on the FAT partition or simply ignores it and boots directly the main OS.

As pointed out above, there seems to be an SPI flash on the board where the boot loader resides now. Maybe that’s their work around?

https://blog.mythic-beasts.com/2019/06/22/raspberry-pi-on-raspberry-pi/ tells about the RPi 4 ‘yet’ not able to netboot which might be an indication that ThreadX as main OS has gone here. So most probably it’s more or less incompatible ‘at the heart’ which doesn’t matter that much for average users since the OS images available will still run on the older RPi and the new one.

Really curious how they deal with video on the new SoC (VC is mentioned as ‘VideoCore 3D’ solely focusing on this and not the VC’s video engine on the older RPi).

No link to the new Raspbian yet, but I’ve been told Raspbian will still be 32-bit.

> Raspbian will still be 32-bit

Sure and compiled for ARMv6 as in the past. But that’s neither important nor an issue (64-bit code comes with a larger memory footprint and provides better performance only in rare cases).

If they supply aarch64 ld out of the box then sure — let their userspace be whatever they like. More often than not, though, running arm64 binaries on an armhf userspace is a much greater hurdle than running armhf binaries on a arm64 userspace, exactly because of the way the armhf/aarch64 loaders are made asymmetrical to set up.

They bring up the cores in ARMv7/32-bit state (I linked to a German review but Jean-Luc deleted my comment, most probably in preparation of an own test). In the meantime the new Raspbian release is available: https://www.raspberrypi.org/downloads/raspbian/

Yes. Just received my board now, and booted it.

sbc-bench please.

I saw a 7-ZIP MIPS score of 5658 which would mean that the RPi 4 is ~50% faster than a RPi 3 but still slower than RK3399 boards, ODROID XU4 or S922X/A311D boards with multi-threaded loads. But looking at final scores without monitoring what’s happening (throttling?) is somewhat useless.

I’ll do sbc-bench, but I’m also running Phoronix. Throttling will happen for sure, as there’s no heatsink. Just downloading and installing the benchmark, so not running yet, and the CPU temp as measured with IR thermometer is 65C.

Phoronix takes ages while sbc-bench should finish in less than 15 minutes 🙂

And just in case you don’t know it: with

sbc-bench -myou switch to monitor mode though no idea whether monitoring clockspeeds/thermals works already with RPi 4. Quite useful to monitor execution of other benchmarks like Phoronix to spot throttling or similar behavior (frequency capping due to undervoltage is one of the unique RPi ‘features’)The result of A311D board is based on 2GB RAM, will update 4GB version soon.

We will also try to overclock the A73 freq over 2.2 GHz if available.

BTW, will the sbc-bench support the NPU performance test in the future?

An optimized build with -mtune=cortex-a72 in ARMv8 aarch32 mode would likely run noticeably faster in user space. idiv, neon, and pipeline specific optimizations each may be small, but they do add up, thumb2 mode might help or hurt depending on use case and the memory subsystem.

Also at 4GB of RAM, you really want to run a 64-bit kernel at least, otherwise over 80% of the RAM is highmem.

The easiest way would certainly be to just run a whole 64-bit distro and skip Raspbian, but then we need to wait for either the kernel support to get mainlined first (I have yet to look at their code), or some distro picking up their driver patches.

It’s possible to run a 64-bit kernel, but once you scale out the software stack the world expects to run on an RPi4 you start to find gaps and thus 32-bit was the sensible way forwards for the launch. The intention is to upstream a lot more support than has been acheived in the past so there’s less downstream technical debt on the Pi Foundation maintainers – and during development the ‘bring up’ team has included several regular kernel contributors to assist/guide (and in some cases force) development to follow a path that’s less “make it work” and more “make it upstreamable” .. although we’ll have to see how it goes. Our (LibreELEC) goal is to move forwards from 4.19 to 5.2/5.3 as quickly as possible as it will facilitate easier work on GBM/V4L2 (needed for Kodi v19) and to align with HDR development that’s already underway with Intel and other SoC platforms like Amlogic/Allwinner/Rockchip.

Board datasheet here https://www.raspberrypi.org/documentation/hardware/raspberrypi/bcm2711/rpi_DATA_2711_1p0_preliminary.pdf

5.6 Temperature Range and Thermals

The recommended ambient operating temperature range is 0 to 50 degrees Celcius.

To reduce thermal output when idling or under light load, the Pi4B reduces the CPU clock speed and

voltage. During heavier load the speed and voltage (and hence thermal output) are increased. The

internal governor will throttle back both the CPU speed and voltage to make sure the CPU temperature

never exceeds 85 degrees C.

The Pi4B will operate perfectly well without any extra cooling and is designed for sprint performance –

expecting a light use case on average and ramping up the CPU speed when needed (e.g. when loading

a webpage). If a user wishes to load the system continually or operate it at a high termperature at full

performance, further cooling may be needed.

Active cooling options for RPI 4 – Piromoni Fan SHIM @ https://shop.pimoroni.com/products/fan-shim

That improvised fan would’ve been way more efficient had the Foundation put something resembling a heatsink..

Or “Make Rpi Noisy Again”

Most RPi resellers offer a stick-on heatsink pack for £1/$1 which is enough to keep temps a bit lower.

That’s not reassuring. At the very least, there should be a list of Foundation-endorsed thermal solutions that can sustain the levels of advertised performance.

Expected similar or less than Odroid XU4 performance. Minus is, they use BCM2711 with 28nm (same with ~4yo XU4), it will be much better if they move to 14nm. But for that price, it’s kind of OK. 4 Cortex-A72 is much welcomed.

If I can get $49 XU4 vs $45 rpi4 with same postal fee (which won’t happen. rpi4 will be readily available later at my country), I rather get XU4 still. +4 little core, included heatsink, and mature OS is a plus.

*edited

If the GPIO header is still 3.3v safe that is one major advantage over the XU4.

@TLS up there posted the board datasheet. Looks like 3.3v safe. Oh, and one more minus: RTC. XU4 RTC is better.

RTC isn’t too much of a problem. You probably only really need the correct time for TLS. If you can do TLS you can do NTP to get the right time.

I’m using it for web server and sometimes for desktop computer. In my city, internet connection is not always available, or client that don’t want to connect to internet (beside electricity problem). XU4 RTC is so simple that I can just go to the electronic shop and buy one, compared to RPI ‘RTC Hat’

Don’t get me wrong, I think the hardkernel stuff is much better engineered, but the hassle of getting the always on power stuff worked out for the RTC probably wasn’t worth the effort for the rpi. Not many people want to use something that performs like a $20 junk shop laptop as their main computer so having accurate time without internet connectivity isn’t that much of a concern.

Agreed about hardkernel. For rpi4, I think they should think abut RTC cause as of now, it’s quite good for desktop replacement, IMHO.

I’d root for the pi 4 regardless just because of broader range of community/third party support.

Let’s see how compatible the old VideoCore thingies are compared to the first ‘true ARM’ RPi 😉

Fabnode and thermals?

See above. Die shrink from 40nm to 28nm somewhat helps and they promise no sustained full performance without additional cooling as expected.

But I see no provisioning for additional cooling, no?

The Fan SHIM linked above is connected to the GPIO header, and one of the mounting holes.

I was just marveling at the mechanical engineering involved : )

Are you joking ? A fan blowing on a naked cpu will be wildly inefficient, you need big surface in contact with flowing air to dissipate heat (the prurpose of the fins of a heatsink).

And what worry me more is “the fixation”… only two point (the hole is in line with the gpio connector ) and a vibrating mass (the fan) which is centimeters away… this thing must jiggle like and shit and could even weaken the solders of the gpio port.

At min I would add a heatsink and use an opposite mounting hole to create a 3 point fixation (way more stable)

For the record, I was kidding.

Micro HDMI is a terrible choice. Hardkernel had to make this experience with Odroid C1, which was the reason why they switched back to fullsize HDMI on the C2.

Yes – historically the Pi Foundation spoke negatively about Micro HDMI connectors when they explained their use of Mini HDMI on the Pi Zero. They aren’t the greatest mechanically. However I can see why the Pi Foundation took the decision to use them in order to provide dual display functionality in the same form factor.

Mini DP or USB-C would’ve been a far superior choice imho.

Just wondering if two HDMI Flag Connectors would be better then Micro HDMI 🙂

https://www.te.com/usa-en/product-2007435-2.html?q=hdmi&type=products&p=2&samples=N&inStoreWithoutPL=false&instock=N

Hi Jean:

May I know that where you got the information that Rpi4 encode with H.264 up to 1080p30?

Thanks!

From Cytron, one of the resellers.

Anybody know if the USB-C port of Rpi4 with USB OTG feature?

Yes, https://www.raspberrypi.org/blog/raspberry-pi-4-on-sale-now-from-35/ mentions ‘USB OTG to boot’

The RPi 4 is something entirely different than the old crippled VideoCore thingies (3B+ included). This is a real ARM device just using an embedded VideoCore implementation for 3D acceleration.

Gigabit, true USB3 and quad A72 ? Now this could become the first respectable device emitted by RPi foundation. Let’s see how it goes over time. No mention of crypto extensions though, and it might still be that default builds will remain unoptimized 32-bit. Let’s see how it goes.

It is a very respectable design. A72 has crypto extensions. Hopefully they ditch that Raspbian nonsense.

They bring the cores up in ARMv7 mode and as such Crypto Extensions not being usable is to be expected. Fiddling around in

config.txtmost probably won’t work (this is a VideoCore thing but maybe the RPi 4 bootloader in the SPI flash learns to parse config.txt as well to keep ‘compatibility’) so curios how to bring up the cores in 64-bit/ARMv8.tomshardware did some overclocking tests and confirmed that config.txt is still in place. So the new bootloader still looks for stuff on the 1st partition that needs to be FAT formatted and you can add there stuff below a ‘[pi4]’ label.

There is no ARMv7 mode on ARMv8. Instead there is aarch32 mode, which is a superset of ARMv7VE. The Crypto Extensions in Cortex-A53 and Cortex-A72 are an optional feature, but if they are present, they would be there in both aarch32 and aarch64 mode.

Later instruction set extensions like SHA3 are only available in aarch64 mode, but Cortex-A72 predates them.

The raspbian image contains loadable modules for crypto extensions in /lib/modules/4.19.50-v7l+/kernel/arch/arm/crypto, but I don’t know if the CPU has the support enabled in hardware.

The problem I see here is more in line of ‘they bring up the CPU in aarch32 mode, and then they throw armv6 modules at it’. But that’s only part of the big problem.

Basically, the Foundation is the sole entity out there who does 32-bit kernels on aarch64 hw, and it’s beyond stupid at this point. Even vendors who are (or used to be) hard-sworn armhf userspacers don’t do (or never did) this, and for a good reason: aarch64 kerenels run aarch32 tasks just fine, so you allow your aarch64 users to still make proper use of the hw, whereas you can keep factory userspace as armhf.

Ironically, apple ditched aarch32 even from their watches, and currently build aarch64 + 32-bit pointers on watchOS — once you have short pointers aarch32 provides no benefits whatsoever in the non-MCU world, and is just a waste of transistors (outside of BC).

This is how /proc/cpuinfo looks like with RPi 4 and their Raspbian Buster:

At least with RPi 3B/3B+ you can set

arm_64bit=1in config.txt and then the ‘Architecture’ switches fromarmv7ltoarmv8though still no ‘aes’ amongst flags since they didn’t license the stuff.This is all I was talking about when mentioning ARMv7 vs. ARMv8 on the RPi.

That’s lscpu, still thanks for providing it.

I wanted to add kernel support for armv7ve and armv8 to arch/arm/ years ago but somehow never got around to that, so a 32-bit kernel never reports anything higher than plain armv7-a. Running a 64-bit kernel will show “ARMv8 Processor” in /proc/cpuinfo (not ARMv8.1-A or higher, that never got added either), and it’s possible that some distros patched their kernels to also do that on 32-bit, but those patches were never submitted.

The USB chip (VIA VL805) is, as noted, a four (4) port hub. However, there are only two (2) USB3.x ports. Since I doubt they ‘wasted’ two ports, I bet the GB network (and possibly wifi) are attached to the hub internally. I could not find any technical documents (the ‘schematics’ are useless) to confirm or deny this. This would mean that network and (USB) storage are still sharing bandwidth (likely single lane PCIe2.0 5GTs).

> The USB chip (VIA VL805) is, as noted, a four (4) port hub

What? It’s not a hub but a PCIe attached USB3 host controller: https://www.via-labs.com/product_show.php?id=48

According to DT (quick decompiled variant at ix.io/1MEO) the network (brcm,genet-v5) is RGMII attached.

Anybody would have read the actual post, would know there’s a VIA PCIe to USB 3.0 hub, and a separate Gigabit Ethernet transceiver. So Ethernet does not go through USB at all.

> Anybody would have read the actual post, would know there’s a VIA PCIe to USB 3.0 hub

We apparently all going to call it a hub despite it being a HCI. 😉

I did find Eben’s post where its explicitly stated the ethernet is embedded in the SoC. Which still begs the questions: why ‘waste’ two USB3 ports?

I do appreciate them opting for a real HCI instead of the embedded Designware IP. I wish other manufacturers would follow suit on this.

> Which still begs the questions: why ‘waste’ two USB3 ports?

The SoC’s own USB2 port is available as OTG on the USB-C connector. So all 4 USB-A receptacles are provided by the VL805. Maybe they plan for future upgrades then routing SuperSpeed to all 4 receptacles so the RPi 4B+ next year can show an improvement over the 4B now?

In one of the interviews I read / watched they mentioned that they could only route 2 of the 4 USB 3.0 ports out as USB 3.0, with the others routed out as USB 2.0 only – it was literally a lack of board routing space?

I think they had to iterate a lot to get the board size back down to the standard form factor whilst still staying at 6 layers.

This is a odd ball, past comments from Upton said the old design with arm 53 core outside the old SoC, so as to fit them on the design was at the limit. So maybe it is 28nm. Yet it has a heat spreader, so thermal issues ?

Also can it run Android yet?

Was also claimed not to arrive till next year. Is it rushed out due to sales issues ?

No fan word processing

” Our Pi 4 Model B, sat on a desk without a case, hit 69 degrees just writing this piece in LibreOffice. Those keen to hammer their Pis, in terms of workload, would therefore be wise to look at options for keeping things cool. ”

So real cost is Pi 4+ case + fan + USB c power supply and a SDcard

As Upton stated as it heats, it clocks down cores.

will it use the new graphics stack (mostly by Eric Anholt) by default?

It has to. But this only deals with GPU (3D acceleration). I’m more curious how they deal with video acceleration now…

I’m taking bets on how many times tkaiser mentions threadx if anyone’s interested.

question remains, does it play HDR content?

HW supports it, but SW is not there yet:

https://forum.libreelec.tv/thread/17698-libreelec-leia-9-2-alpha1-with-raspberry-pi-4b-support/?postID=121518#post121518

My deleted post pointed to LibreElec who have a alpha for this Rpi4. HDR etc will need kernel updates. Software has been worked on for around 6 months but needs polishing and tweaking.

Its almost everything i wanted. ( dual display, usb3, larger ram, Gbe)

But its still Videocore IV. o(〒﹏〒)o

no biggie, since only one of my projects is Retropie.

any details info on the gpu?

That’s VideoCore VI though that’s why they can handle 4K & H.265, as well as OpenGL ES 3.0.

They don’t seem to have officially passed GLES conformance on VC VI just yet (https://www.khronos.org/conformance/adopters/conformant-products/opengles ^f broadcom)

Great news regarding the gigabit ethernet. I can’t seem to find any information on WoL though. Will that be supported?

Storage IO does not seem to be improved much.

How do I attach external storage (sata3 or nvme ssd/hdd) to the Pi4 reliably and with good performance?

Does it still have to go through one of the USB ports or a custom storage hat?

How will this compare performance-wise to the RK3399 boards that have NVMe support?

I guess Odroid HC1 and HC2 will still have their market.

Using a proper USB3.0 instead of a half-broken USB2.0 will make a huge difference, it’s certainly fast enough for hard drives, and the throughput should be sufficient for SATA SSDs as well, though it adds noticeable latency. I suspect there will be an NVMe version at some point, because it is the obviously right thing to do.

Note that VL805 is PCIe 2.0 1x, so has a theoretical 5Gbps bandwidth shared by the 4 USB ports.

“PCIe 2.0 uses an 8b/10b encoding scheme, therefore delivering, per-lane, an effective 4 Gbit/s max transfer rate from its 5 GT/s raw data rate” – wikipedia.

You’re right, I forgot.

However, USB 3.0 also uses 8b/10b, so theoretical PCIe bandwidth still matches one USB 3.0 port.

How?

You have a 8b/10b ‘reduction’ between SoC and USB host controller via PCIe. And at the other end of the USB3 host controller there’s 8b/10b again.

So data is pushed with 4 Gbits/sec max between SoC and the VL805 and back. And due to 8b/10b again being the coding scheme for USB3 SuperSpeed you end up with a maximum transfer rate of 3.2 Gbits/sec. Or most probably I’ m missing something…

Edit: right, it remains at the previous ‘reduction’ since the data rate that ends up being 4 Gbit/sec will not change once it’s sent over the wire again using 8b/10b coding since these additional bits are only added to the signal rate.

This is most probably the comment thread I spread most BS ever 🙁

Missing port for eMMC storage module from my wishlist.

Also read that Rpi4 doesn’t yet support USB boot.

Miss a header for eMMC storage module from my wishlist.

Also read that Rpi4 doesn’t yet support USB boot.

> Miss a header for eMMC storage module from my wishlist.

Well, according to the RPi Trading ‘experts’ eMMC is less reliable than SD cards since… SD cards have wear leveling, EMMC generally doesn’t, so if using them for the same thing, the EMMC will fail first.

eMMC = live fast, die young. Ordinary users prefer replaceable cheap storage with wear leveling. This board is mostly designed for educational purposes. Major other users are the consumers of illegal movies (now 4k) and casual gamers playing emulated legacly pirate games.

Thats just plain bullshit. There are no eMMCs (that i know of) that wouldn’t have any kind of wear levelling.

Remember, eMMC us just a soldered sd card and as such NEEDs a flash controller to work properly.

LOL, it get’s even better: eMMC is a nightmare of pain to implement (HW and SW) and costs a lot. These guys are really funny! 🙂

Reminds me of ‘fruitful discussions’ over there in RPi land when the clowns insisted that Micro USB would be the superior way to power SBC compared to sane barrel plugs. Also denying the undervoltage drama majority of RPi users is affected from.

Yeah, that guy instills no confidence. Implementing eMMC doesnt really take that much more SW if any; eMMC as ive said is just a soldered sd card. Unless you’re doing some additional commands, software side for SD slot alone should be enough.

These are either just excuses or they dont know what theyre talking about.

Also the dreaded 3V3 defect on earliest RPI1 rev1 boards never got adressed (a recall or a fix) they just cleaned it under the rug; even the thread on their forums is gone.

Quick sbc-bench run http://ix.io/1MFf shows the following:

* it’s still VideoCore/ThreadX 🙁

* 1.5GHz are real, temps climb up to 80°C within few minutes 7-zip.

* Vcore voltage a lot lower than before (0.86V now compared to 1.325V on RPi 3B+)

* memory bandwidth/latency not that great

* integer performance ~150% of RPi 3B+ (both single-/multi-threaded)

* no Crypto Extensions usable (but that’s due to cores in ARMv7 state)

Idle temperature looks a bit too high (+65°C) but most probably they rebooted an already busy RPi 4 (the test was conducted by German c’t magazine). So the thing still being a VideoCore explains how they manage to get video acceleration (proprietary as before) but with a good heatsink the RPi 4 seems like a good choice if one is comfortable with a board that runs a proprietary closed source OS as main operating system.

What do you mean by “no crypto due to ARMv7” ?

Here is the /proc/cpuinfo of a Cortex-A53 with crypto with an ARMv7 kernel (this is a Broadcom STB chip) :

processor : 0

model name : ARMv7 Processor rev 0 (v7l)

BogoMIPS : 54.00

Features : half thumb fastmult vfp edsp neon vfpv3 tls vfpv4 idiva idivt vfpd32 lpae evtstrm aes pmull sha1 sha2 crc32

CPU implementer : 0x42

CPU architecture: 7

CPU variant : 0x0

CPU part : 0x100

CPU revision : 0

If you don’t see aes/sha1/sha2 support, it would mean they didn’t include them in their A72.

Most probably I’m confusing things.

When playing with the Samsung/Nexell S5P6818 (octa-core A53) some time ago I noticed Crypto Extensions missing (with a 32-bit 3.4 kernel). So I thought they wouldn’t be there until @willy informed me after switching to a 4.4 64-bit kernel they showed up: https://www.cnx-software.com/2017/11/12/nanopi-fire2a-fire3-boards-released-with-samsungnexcell-quad-octa-core-processors/#comment-549018

But as you demonstrated it’s not related to ARMv7 vs. ARMv8…

The code to print “aes” in cpuinfo has been added in 3.15 for ARMv7 (https://github.com/torvalds/linux/commit/8258a9895c99cdaacad8edc4748c0a624c710961).

and in 3.14 for ARMv8 (https://github.com/torvalds/linux/commit/4bff28ccda2b7a3fbdf8e80aef7a599284681dc6).

So on older kernels it isn’t displayed, but the userspace can probably still use it.

Just to be clear, the above is not a CA53 per se — CPU implementer is not ARM (0x41) and CPU part is not CA53 (0xd03).

Yes, it’s officially a Broadcom Brahma-B53, but I don’t know if there is any real difference with an A53.

Raspbian Buster but is still 32 bit…. For versions 2GB and 4GB they should made 64 BIT. It is wasting of four A72 core power.

By the way – i ordered 4GB version. Mniam mniam….

Since there is no kernel source available yet, I did a diff of the device tree files: https://paste.ubuntu.com/p/M9wfTbr9td/

A few things I noticed:

– The USB3 (xhci) is listed as on-chip, but the board clearly has a PCI-USB host, no idea what’s going on there.

– There is a new high-speed bus called “scb” that contains pcie (brcm,bcm7211-pcie), gigabit ethernet (brcm,genet-v5), dma (brcm,bcm2838-dma), usb3 (generic-xhci), and something called argon (hevc-decoder, local-intc, h264-decoder, vp9-decoder). My guess is that this entire part of the chip was lifted from one of their set-top-box chips (bcm7xxx).

– The PCIe support seems to be rather crippled: it only has 32-bit DMA access (meaning it can’t reach the upper parts of the RAM for the largest board), MSI forwarding is broken (it turns all MSI to a single GIC interrupt), and MMIO space is limited to one 1GB non-prefetchable memory window, no 64-bit/prefetchable regions or PIO support.

– A number of on-chip devices have new identifiers (compatible strings): cprman, rng, dma, mailbox (vhiq)

– The main interrupt controller is now a standard gic-400 rather than their own thing.

– A third mmc host controller was added (brcm,bcm2711-emmc2), different from the two that were already there.

– there are additional ports for uart (6), spi (7), and i2c (7), same drivers as the existing ones.

> The USB3 (xhci) is listed as on-chip

And is

status = "disabled". Maybe USB3 is even more quirky than PCIe so they needed to go the PCIe attached USB3 route nicely increasing overall consumption?Perhaps it wasnt quite ready for prime time and instead of making another silicon spin, they just decided to go to external chip route.

https://github.com/raspberrypi/linux/blob/rpi-4.19.y/arch/arm/boot/dts/bcm2838.dtsi

Good to know code for BCM2711 processor is bcm2838.

No vulkan support? 🙁

I don’t understand the choice of name. They call it a B form factor, but it isn’t. Why not call it the C? I mean it has ‘compact’ connectors and a USB-C port. It would make a lot more sense.

Power consumption vs RK3399 boards? Four A72 means the RPi 4 is all BIG and no Little.

? Little GHz

A72 running like crazy in flip-flops while wearing a chunky woolly jumper.

LOL

Benchmarks and mini-review of Raspberry Pi 4 board:

https://www.cnx-software.com/2019/06/24/raspberry-pi-4-benchmarks-mini-review/

So much for the charity work, more a tax dodge?

” Industrial use

Alongside traditional educational use, more serious consumer, industrial and commercial uses are foreseen for Pi 4.

“Just as we help make coding more accessible for consumers, we also aim to democratise digital innovation in businesses and public services,” said Upton, “Today, over 50% of our $35 Raspberry Pi units are destined for industrial and commercial use. Raspberry Pi 4 builds on this, providing greatly increased performance at the same cost. We aim to provide a low-cost platform for technological innovation that is accessible to every organisation, from start-ups to multinationals.” ”

Electronicsweekly

Well, anyway, large corporations like Broadcom has so many patents so they probably use patent boxes through Ireland or Holland to pay 0,0005% taxes like Apple and others do.

Industrial use sells boards. Kodi use sells board. The profits from board sales fund the educational mission.

Where’s Jerry ? For once he could be here saying great stuff about RPi without being (too much) downvoted.

What would you want me to say? It’s a great new board no doubt and a really competitive price. I can’t imagine anyone buying that chinese cr*p anymore.

Jerry delivers again.

And just like that my interest in RK3399 and S922 based SBCs and even the Nvidia Jetson Nano has dropped significantly

I made the comment elsewhere that this means the death of all the recent RK3399 “something pi” boards. S922, however, is still far ahead of Pi4 in performance (4xA73+2xA53 clocked 25% higher) and media capabilities (MPEG2, HDR, etc). It has yet to be demonstrated whether Pi4 has a version of AFBC. If it does not then 4K@60 is going to be as challenging as it is on RK3328 (Rock64) due to memory bandwidth constraints. Whether its capable through brute force (like RK3399) depends on their memory controller interface to DRAM.

If the memset/memcpy values are any indication, it’s not. By half. It’s looking like *one* 4Kp30 display will be the limit.

So the 2*4Kp30 vs 1*4Kp60 perhaps comes from memory bandwidth.

The BCM2711 documentation page advertises LPDDR4-2400 support (nothing in the small datasheet), but the pictures show a much faster Micron D9WHV chip (LPDDR4-3733).

RK3399 has 64-bit wide DDR4 path so it has 2x the effective memory bandwidth of BCM2711B0. It is also a far more capable SoC. If anything, you will see RK3399 exceed BCM2711B0.

It could be to get the lower latencies? If you support a given latency at a higher clock speed, the number of clock cycles at a lower clock speed is less to get the same actual delay. Just a guess.

Given Broadcom STB chips support this kind of LPDDR4 frequency, I wonder why the raspberry pi 4 cannot (PCB or power constraints perhaps ?).

Hope Google will port ChromeOS to Raspberry Pi 4