Back in September, we reported that Espressif Systems planned to release a new ESP32-S3 with “AI instructions and multi-CPU cores” with few other details, except the chip would also be part of the MINI-series wireless modules.

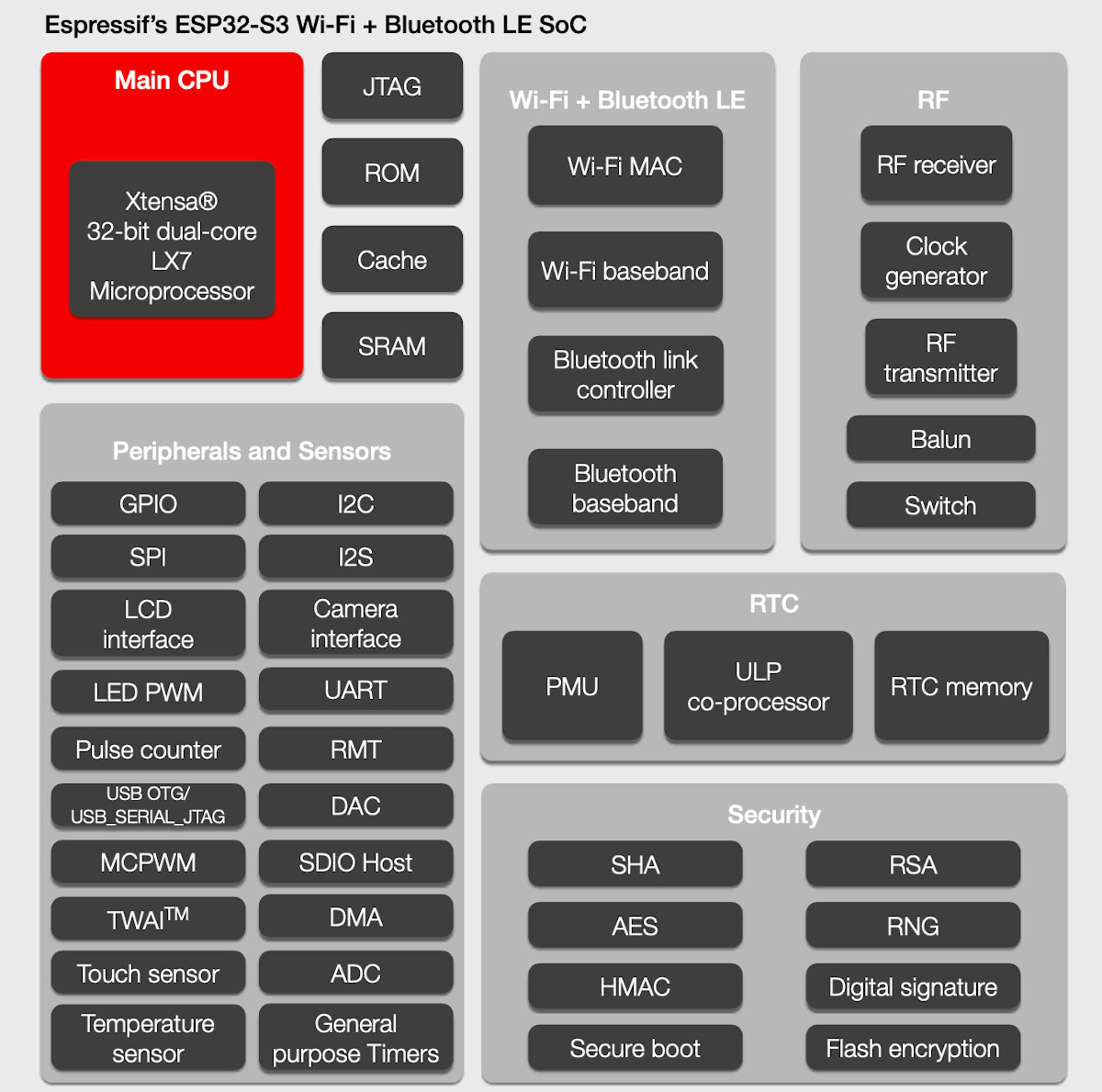

Now we have many more details, as the Shanghai-based company has now officially announced ESP32-S3. The processor features dual Tensilica LX7 cores, 2.4 GHz WiFi 4 & Bluetooth 5 connectivity, and as expected supports AI instructions to cater to the AIoT (AI + IoT) market.

ESP32-S3 key features and specifications:

- CPU

- Dual-core Tensilica LX7 up to 240 MHz with additional vector instructions for AI acceleration

- ULP core to handle low power modes

- Memory – 512 KB of internal SRAM

- Storage – Octal SPI flash and PSRAM support (supports larger, high-speed devices compared to ESP32)

- Cache –

- Connectivity

- 2.4 GHz 802.11 b/g/n Wi-Fi 4 with 40 MHz bandwidth support

- Bluetooth Low Energy (BLE) 5.0 connectivity with long-range support, up to 2Mbps data rate.

- Peripherals

- 44x programmable GPIOs (10 more than ESP32)

- SD/MMC host

- SPI, I2C, PWM, UART, RMT (Remote Control), TWAI (Two-Wire Automotive Interface)

- ADC, DAC

- I2S

- USB OTG

- Capacitive touch input

- Security

- AES-XTS-based flash encryption

- RSA-based secure boot.

- Digital signature peripheral and an HMAC module (similar to a secure element)

- “World Controller” peripheral that provides two fully-isolated execution environments and enables a trusted-execution environment or a privilege-separation scheme.

ESP32-S3 relies on the same 240 MHz LX7 core as ESP32-S2, except it comes with two. Since it’s a dual-core processor and supports both WiFi and Bluetooth LE it’s more comparable with the original ESP32 dual-core LX6 WiSoC.

ESP32-S3 will be faster with a 240 MHz stock frequency instead of 160 MHz, it should specifically be much faster for AI applications thanks to the vector extension, but Espressif did not provide numbers just yet. We just know the new vector extension will be used in ESP-WHO face detection and recognition framework and ESP-Skainet voice assistant.

Other key differences between ESP32-S3 and ESP32 include support for larger capacity and higher-speed SPI flash and PSRAM chips, a few more I/O pints, more security features, a lack of Ethernet MAC, and support for Bluetooth LE 5.0 connectivity with long-range and 2Mbps transfer support. You may remember ESP32 got Bluetooth LE 5.0/5.1 certifications nearly exactly a year ago, but as we noted in the article this was more to do with improved compatibility of the software, and key features of Bluetooth 5.0 like long-range and higher 2Mbps data rate were not supported, so this is a big change in ESP32-S3.

There’s no product page, nor datasheet that I can find at this stage, so all information comes from the press release.

Thanks to Alex for the tip.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

Just a few minor corrections, original ESP32 was already running at 240 MHz but was an LX6. And it has 36 GPIO which is 8 less than this new one. The SRAM decreased from 520 to 512 kB (well, in fact I suspect that they used to count the SRAM and a 8kB cache together and now they separate them). The ethernet MAC is gone. I didn’t see that many projects using it anyway.

I thought the stock frequency was 160 MHz, but it could be overclocked to 240.

It’s never been clear to me whether it’s overclocked or not, given that 240 MHz is mentioned everywhere in the datasheet. I’d instead suspect that 240 MHz is the nominal frequency and that 160 is the recommended one for a better performance/consumption tradeoff.

We are using it (the ethernet MAC)…

Octal SPI? That’s just parallel with SPI signalling.

no ethernet mac then ?

The block diagram includes USB OTG …

Naw, where are the ESP32-C3 dev boards? I want to see a RISC-V ESP32. I am not very interested in these Xtensa cores.

Does the octal-SPI support DDR? I’m looking at data sheets and you can move a lot of data over an octal-SPI/DDR link. This could be an increase of 4x over what the current chips support. Maybe even faster performance increas than that if they take advantage of some of the advanced features of octal-SPI (critical word first, etc.)

This could end up making a bigger difference in performance than the dual LX7 configuration. At least for codes with a larger RO memory footprint.

I’m sort of curious what the reasoning behind this decisions was. Were other similar memory interfaces considered? Was HyperRAM an option? I wonder if we can get an AMA with one of their people like Sprite_tm?