Linus Torvalds has just announced the release of Linux 5.13: So we had quite the calm week since rc7, and I see no reason to delay 5.13. The shortlog for the week is tiny, with just 88 non-merge commits (and a few of those are just reverts). It’s a fairly random mix of fixes, and being so small I’d just suggest people scan the appended shortlog for what happened. Of course, if the last week was small and calm, 5.13 overall is actually fairly large. In fact, it’s one of the bigger 5.x releases, with over 16k commits (over 17k if you count merges), from over 2k developers. But it’s a “big all over” kind of thing, not something particular that stands out as particularly unusual. Some of the extra size might just be because 5.12 had that extra rc week. And with 5.13 out the door, that obviously means […]

Ingenic T40 4K Video & AI Vision Processor mixes MIPS & RISC-V cores with AI accelerator

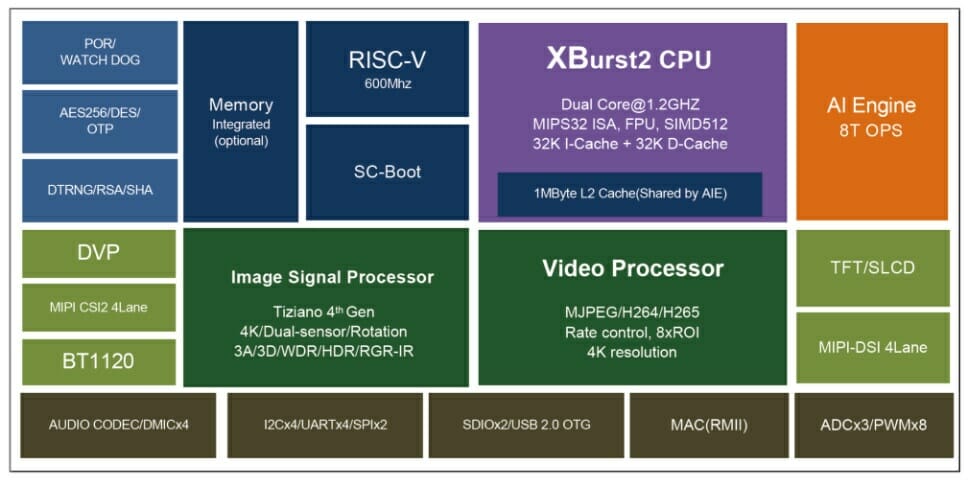

Ingenic T31 MIPS & RISC-V AI video processor was introduced last year with the MIPS core including SIMD128 Vector instructions for deep learning. The Chinese company has now introduced the new Ingenic T40 processor still with MIPS and RISC-V cores, but also a dedicated 8 TOPS AI engine/CNN accelerator. The new processor is especially suited to smart AI vision application thanks to support for 4K cameras, and 4K MJPEG/H.264/H.265 hardware video encoding, complemented by the 8 TOPS AI engine for computer vision workloads such as people detection, face recognition, object detection, and so on. Ingenic T40 key features and specifications: CPU – Dual-core MIPS XBurst2 @ 1.2 GHz with 256KB L2 Cache, SIMD512 instruction set MCU – 600MHz RISC-V coprocessor AI Engine – 8 TOPS neural network accelerator with 1MB memory pool, support for int16/int8/int4/int2 convolution width Memory – DDR2/DDR3/DDR3L up to 2GB Storage – SPI NOR flash, SPI NAND flash, […]

Linux 5.10 LTS release – Main changes, Arm, MIPS and RISC-V architectures

Linus Torvalds has just released Linux 5.10: Ok, here it is – 5.10 is tagged and pushed out. I pretty much always wish that the last week was even calmer than it was, and that’s true here too. There’s a fair amount of fixes in here, including a few last-minute reverts for things that didn’t get fixed, but nothing makes me go “we need another week”. Things look fairly normal. It’s mostly drivers – as it should be – with a smattering of fixes all over: networking, architectures, filesystems, tooling.. The shortlog is appended, and scanning it gives a good idea of what kind of things are there. Nothing that looks scary: most of the patches are very small, and the biggest one is fixing pin mapping definitions for a pincontrol driver. This also obviously means that the merge window for 5.11 will start tomorrow. I already have a couple […]

Ingenic X2000 IoT Application Processor Combines 32-bit MIPS Xburst 2 Cores with Xburst 0 Real-time Core

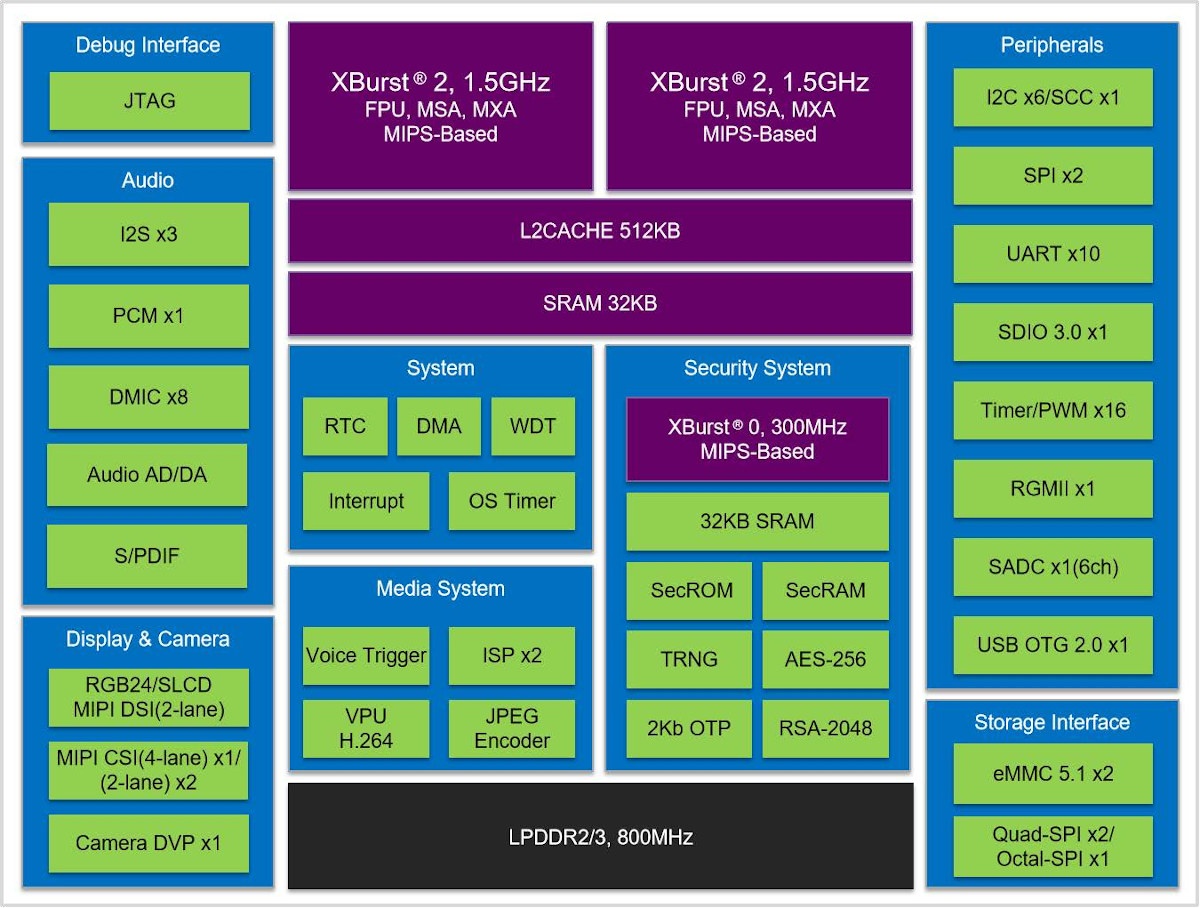

In Arm’s world, heterogeneous processors are pretty common, with for example big.LITTLE / dynamIQ application processors mixing powerful Cortex-A7x cores with power-efficient Cortex-A5x cores., or “industrial” processor such NXP i.MX 8M family with Cortex-A53 application cores combined with Cortex-M4F real-time core. Maybe I did not follow enough, but I hadn’t really seen anything equivalent in MIPS world, except if we count Ingenic T31 with RISC-V and MIPS cores. That is until today where I was informed about documents related to Ingenic X2000 IoT application processor with two 32-bit MIPS Xburst 2 core, one MIPS Xburst 0 real-time cores, as well as up to 256MB RAM built-into the SoC. Ingenic X2000 specifications: CPU Core – Dual XBurst 2, MIPS ISA based, frequency up to 1.5 GHz with 32KB L1 x2 Cache, 512KB L2 Cache, 32KB SRAM, FPU,128bit SIMD MCU Core – XBurst 0 MIPS core @ 300MHz for security and real-time […]

Ingenic T31 AI Video Processor Combines MIPS & RISC-V Cores

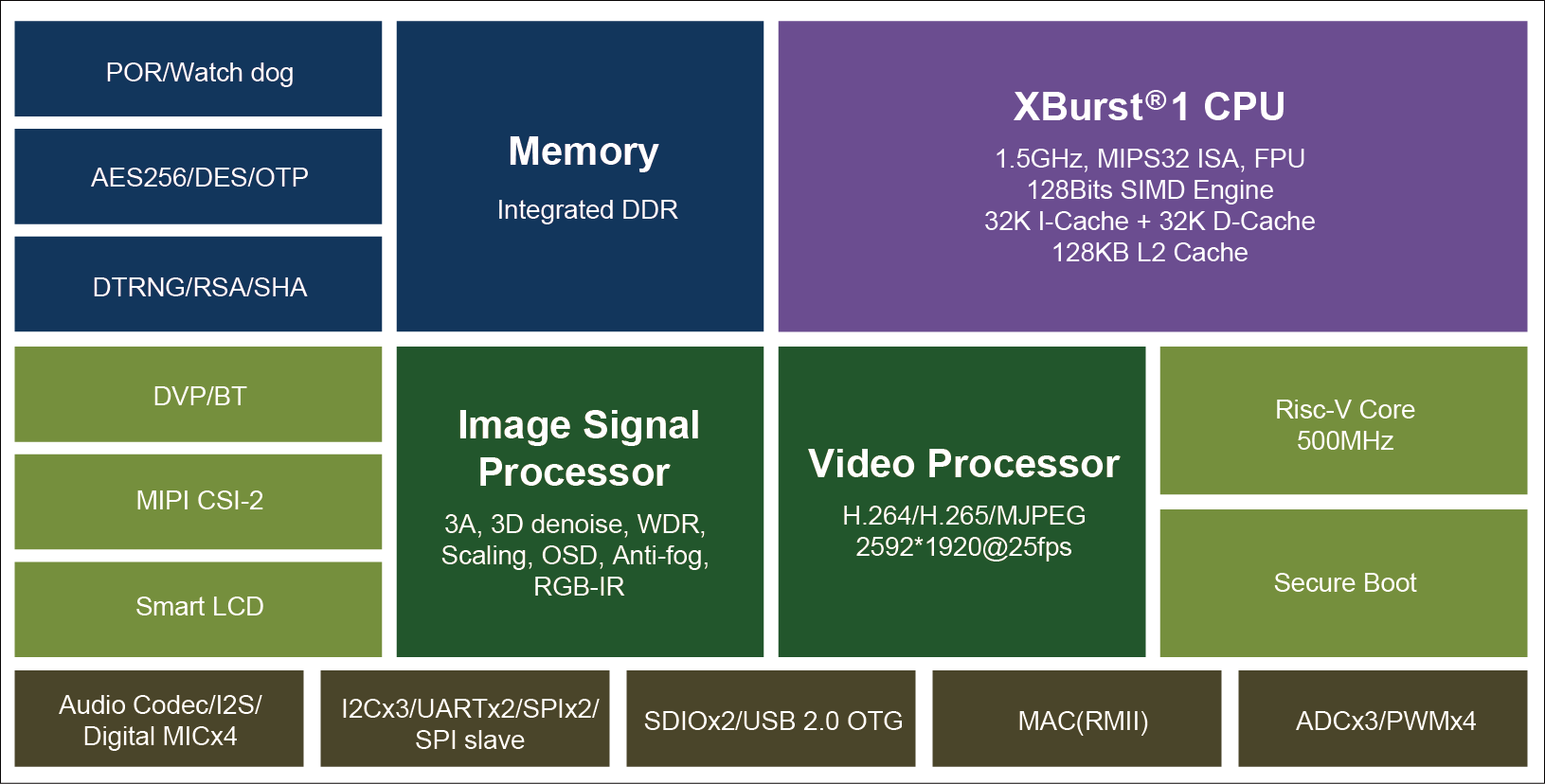

Last week we asked “is MIPS dead?” question following the news that Wave Computing had filed for bankruptcy, two MIPS Linux maintainers had left, and China-based CIP United now obtained the exclusive MIPS license rights for mainland China, Hong Kong, and Macau. Ingenic is one of those Chinese companies that have offered MIPS-based processors for several years, but one commenter noted that Ingenic joined the RISC-V foundation, and as a result, we could speculate the company might soon launch RISC-V processors, potentially replacing their MIPS offerings. But Ingenic T31 video processor just features both with a traditional Xburst MIPS Core combines with a RISC-V “Lite” core Ingenic T31 specifications: Processors XBurst 1 32-bit MIPS core clocked at 1.5GHz with Vector Deep Learning accelerator based on SIMD128, 64KB + 128KB L1/L2 Cache RISC-V independent lite core System Memory – Built-in 512Mbit (64MB) or 1Gbit (128MB) DDR2 Storage – Quad SPI flash, […]

Ingenic X1830 IoT Processor Features a 32-bit MIPS Core, 128MB DDR2 RAM

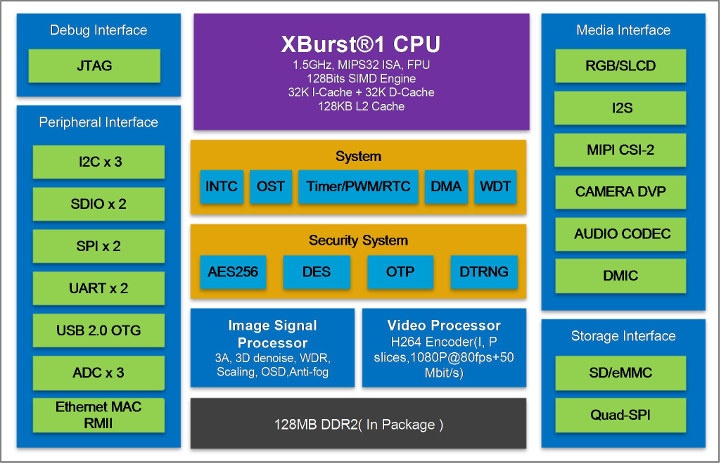

Ingenic is a silicon vendor based in Beijing, China and known for its MIPS Xburst processors such as JZ4780 dual-core SoC or T10 video processor. It’s been a while (a few years) since we last covered new processors from the company, but it appears the company launched another MIPS SoC for IoT applications last year. Meet Ingenic X1830 processor. X1830 specifications: CPU – MIPS32 XBurst-1 core @ up to 1.5 GHz with SIMD engine, 32KB instruction cache, 32KB data cache, 128KB unified L2 cache Memory – 128MB DDR2 in package Storage I/F – 2x SD/eMMC controllers, and Quad SPI (QSPI) VPU H264 Encoder up to 1080p80 or 1560×1600 resolution JPEG compressing/decompressing up to 70Mega-pixels per second ISP 12-bit RAW or up to 24-bit RGB Max input resolution 2688×2048 @20fps, 1080p @60fps,720p @120fps 2-D and 3-D noise reduction filter, advanced demosaic, color processing, lens shading, defog, glare, static/dynamic defect pixel… Image […]

Linux 5.4 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds has just announced the release of Linux 5.4: Not a lot happened this last week, which is just how I like it. And as expected, most of the pull requests I got were for the 5.5 merge window, which I’ll obviously start working through tomorrow. What little there is here is mostly some networking updates (mix of network drivers and core networking), and some minor GPU driver updates. Other than that it’s a small collection of random other things all over. The appended shortlog is small enough that you might as well just scroll through it. Anyway, this obviously opens the merge window for 5.5. It’s not ideal timing with Thanksgiving week coming up, but it hopefully shouldn’t be too much of an issue. If I fall behind (not because I’m all that big of a fan of the indiscriminate and relentless turkey-killing holiday) it’s because we’ve got […]

PrinCube Said to Be Smallest Handheld Smartphone Color-Inkjet Printer That Prints on Anything (Crowdfunding)

PrinCube the smallest, color-inkjet printer on the market. PrinCube is a portable handheld color ink-jet printer that is palm-sized, wirelessly controlled by a smartphone, and easy to set up. The IndieGoGo campaign has exploded to more than $2,000,000.00 USD and featured on a number of tech sites. Article Intent For clarity and function of the PrinCube abilities, there needs to be a careful examination of the facts that surround wireless, handheld, color inkjet, printer, that can print on any surface. Other Handheld, Smartphone, Color-Inkjet Printers There is another product, similar to PrinCube, PrintBrush, which is also a handheld wireless color inkjet printer, connected to a smartphone. It should be noted that while PrinCube is a very popular campaign, PrintBrush, which came out earlier than PrinCube, has very similar claims. It is worth looking over the websites for both printers Here are the campaigns PrintBrush XDR- Colors Everywhere on Kickstarter PrinCube […]