The Embedded Open Source Summit 2024 (EOSS 2024) will take place on April 16-18 and the Linux Foundation has already announced the schedule with conference sessions, lightning talks, and birds of a feather (BoF) sessions covering embedded Linux, Zephyr OS, and real-time (RT) Linux. While I won’t be attending in person, I still find it interesting to check out the schedule as we may learn more about the current status of embedded Linux. So I’ve created my own little virtual schedule out of the available talks. Tuesday, April 16 – Day 1, Embedded Open Source Summit 2024 9:05 – 9:45 – No, It’s (Still) Never Too Late to Upstream Your Legacy Linux-Based Platforms by Neil Armstrong, Linaro Nearly 7 years ago, Neil already spoke about this subject in Berlin, and it’s still very true. Do you maintain or used to maintain a Linux-based board or SoC off-tree? Then there are […]

Microchip PIC18-Q20 low-pin count MCU comes with up to two I3C interfaces

Microchip PIC18-Q20 is a new family of microcontrollers (MCUs) with a low-pin count (14 and 20-pin packages) that integrates up to two I3C interfaces as well as multi-voltage I/O (MVIO) interfaces. MIPI I3C was first teased in 2014, then officially announced in 2017, and the first MIPI I3C specification was released the following year, as a backward compatible update to I2C with lower power consumption, and higher bitrate allowing it to compete against SPI. We’ve seen it used in a few application processors and microcontrollers, but it’s the first time I3C can be found in a lower-cost, low-pin count microcontroller. Microchip PIC18-Q20 specifications: Core – PIC18 8-bit RISC microcontroller core @ 64 MHz Memory – 1KB to 4KB RAM Storage – 16KB to 64KB with Memory Access Partition (MAP) support, 256B EEPROM Peripherals Up to 2x I3C device interfaces Adhere to MIPI I3C Basic Specification 1.0 Support Target Reset Action […]

EPIC-ADS7-PUC Alder Lake-S embedded system is made for robotics, automation, healthcare imaging

AAEON EPIC-ADS7-PUC is an embedded system based on an up to 12th Gen Intel Core i7-12700E Alder Lake-S processor and designed for robotics, automation, and healthcare imaging applications. The embedded computer supports up to 32GB DDR5 and two SATA III storage devices, offers three 4K video outputs via HDMI and DisplayPort connectors, one 2.5GbE and three Gigabit Ethernet ports, along with Intel TCC support, up to six USB 3.2 Gen 2 ports, two RS232/422/4485 COM ports, and some SKUs support Intel Time Coordinated Computing (TCC) for real-time control. Key Features: SoC – Intel Core Alder Lake-S processor, up to the 12-core (8P+4E) Core i7-12700E processor clocked at up to 4.8 GHz with Intel UHD Graphics 770; TDP: 65W Chipset – Intel 600 Series Desktop Chipset (R680E/Q670E/H610E) System Memory – Up to 32GB DDR5 4800 via 2x SODIMM socket (16GB max each) Storage – 2x SATA 3 with +5V onboard SATA […]

Imagination unveils IMG RTXM-2200 32-bit RISC-V real-time “Catapult” CPU

Imagination IMG RTXM-2200 32-bit RISC-V real-time CPU core is the first member of the company’s Catapult family comprised of four distinct RISC-V families for dynamic microcontrollers, real-time embedded CPUs, high-performance application CPUs, and functionally safe automotive CPUs. The company says it’s a highly scalable real-time, deterministic, 32-bit embedded CPU, that is feature-rich and flexible in design for mainstream devices, but, excuse the pun, leaves most of the details to your imagination… The new core will mostly be used as a helper core (aka co-processor) in more complex SoCs for 5G modems, cellular base stations, networking solutions for data transfer, packet management, and storage controllers, but may also find its way into smart meters. In all fairness, we do have some limited technical details with L1 cache sizes up to 128KB, I/D TCM sizes up to 128KB, and PMA regions. The real-time core will also include optional features such as single-point […]

Ubuntu 22.04 LTS “Jammy Jellyfish” released

Canonical has just released Ubuntu 22.04 LTS “Jammy Jellyfish” right on schedule. The new version of the Linux operating system provides cloud confidential computing, a new real-time kernel for industrial applications, Arm optimization, support for Raspberry Pi SBCs, as well as support for enterprise Active Directory, PCI-DSS, HIPAA, FIPS, and FedRAMP compliance. Confidential Computing aims to improve data protection and privacy in public clouds without requiring any changes to existing application deployments, and Ubuntu 22.04 supports Azure Confidential VMs. Speaking about cloud computing, Canonical also says they optimized Ubuntu 22.04 LTS images for AWS Graviton for greater performance on Arm servers. The new real-time PREEMPT_RT kernel is currently in beta and available for both x86 and Aarch64 architectures. It is designed for telco (5G gateways) as well as other latency-sensitive applications such as industrial automation and robotics. Ubuntu 22.04 LTS is also the first long-term support release with Ubuntu Desktop […]

Linux 5.17 release – Main changes, Arm, RISC-V, and MIPS architectures

Linus Torvalds has just released Linux 5.17: So we had an extra week of at the end of this release cycle, and I’m happy to report that it was very calm indeed. We could probably have skipped it with not a lot of downside, but we did get a few last-minute reverts and fixes in and avoid some brown-paper bugs that would otherwise have been stable fodder, so it’s all good. And that calm last week can very much be seen from the appended shortlog – there really aren’t a lot of commits in here, and it’s all pretty small. Most of it is in drivers (net, usb, drm), with some core networking, and some tooling updates too. It really is small enough that you can just scroll through the details below, and the one-liner summaries will give a good flavor of what happened last week. Of course, this means […]

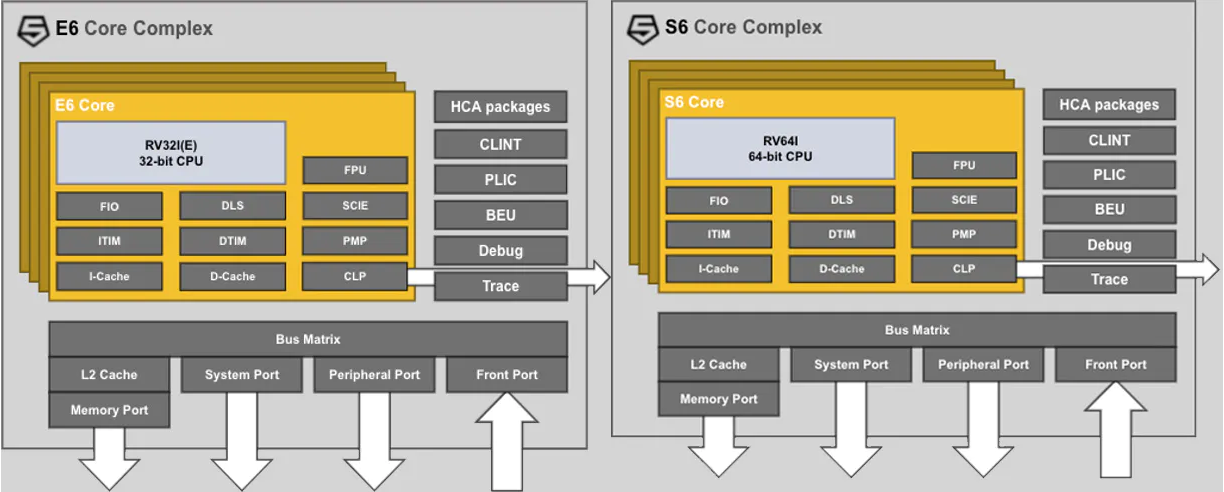

Sifive Essential 6-Series RISC-V processors target Linux, real-time applications

SiFive has been busy. Just a few days after SiFive Performance P650 announcement, the company has announced the SiFive Essential 6-Series RISC-V processor family starting with four 64-bit/32-bit real-time core, and two Linux capable application cores, plus the SiFive 21G3 release with various improvements to existing families. SiFive Essential 6-Series range of RISC-V processors There Essential 6-Seris family is comprised of three sub-families with two processors each: E6 Series with 1.91 DMIPS/MHz, 3.69 CoreMark/MHz E61-MC – Quad-core 32-bit embedded processor E61 – Mid-range performance 32-bit embedded processor (one-core) S6 Series with 2.07 DMIPS/MHz, 3.73 CoreMark/MHz S61-MC – Quad-core 64-bit embedded processor S61 – Mid-range performance 64-bit embedded processor (one-core) U6 Series with 2.07 DMIPS/MHz, 3.73 CoreMark/MHz U64-MC – Quad-core 64-bit application processor U64 – Mid-range performance Linux-capable processor (one-core) E6-Series and S6 Series real-time processors have practically the same features except for the 32-bit and 64-bit cores, and a different […]

Imagination introduces Catapult RISC-V CPU cores

As expected, Imagination Technologies is giving another try to the CPU IP market with the Catapult RISC-V CPU cores following their previous unsuccessful attempt with the MIPS architecture, notably the Aptiv family. Catapult RISC-V CPUs are/will be available in four distinct families for dynamic microcontrollers, real-time embedded CPUs, high-performance application CPUs, and functionally safe automotive CPUs. The new 32-/64-bit RISC-V cores will be scalable to up to eight asymmetric coherent cores-per cluster, offer a “plethora of customer configurable options”, and support optional custom accelerators. What you won’t see today are block diagrams and detailed technical information about the cores because apparently, all that information is confidential even though some Catapult RISC-V cores are already shipping “in high-performance Imagination automotive GPUs”. The only way to get more details today is to sign an NDA. Having said that we have some more information about the target markets and development tools. Imagination Capapult […]