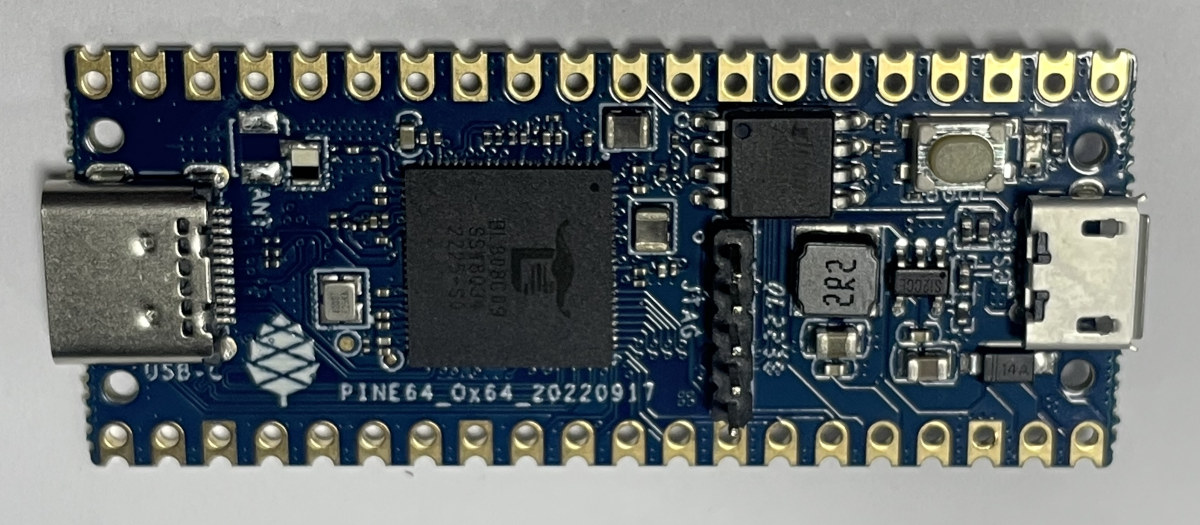

Pine64 Ox64 is a single board computer powered by Bouffalo Lab BL808 dual-core 64-bit/32-bit RISC-V processor with up to 64MB embedded RAM, multiple radios for WiFi 4, Bluetooth 5.0, and 802.15.4 (Zigbee), as well as an AI accelerator. The board also features up to 16MB XSPI NOR flash, a MicroSD card socket, a USB 2.0 OTG port with support for a 2-lane MIPI CSI camera module, and two 20-pin GPIO headers for expansion. It measures just 51 x 21mm, or in other words, is about the size of a Raspberry Pi Pico W. Pine64 Ox64 specifications: SoC – Bouffalo Lab BL808 with: CPU Alibaba T-head C906 64-bit RISC-V core @ 480MHz Alibaba T-head E907 32-bit RISC-V core @ 320MHz Alibaba T-head E902 32-bit RISC-V @ 150MHz Memory – 728KB SRAM, 64MB embedded DRAM AI accelerator – NPU BLAI-100 (Bouffalo Lab AI engine) for video/audio detection/recognition Wireless 2.4 GHz 802.11 b/g/n […]

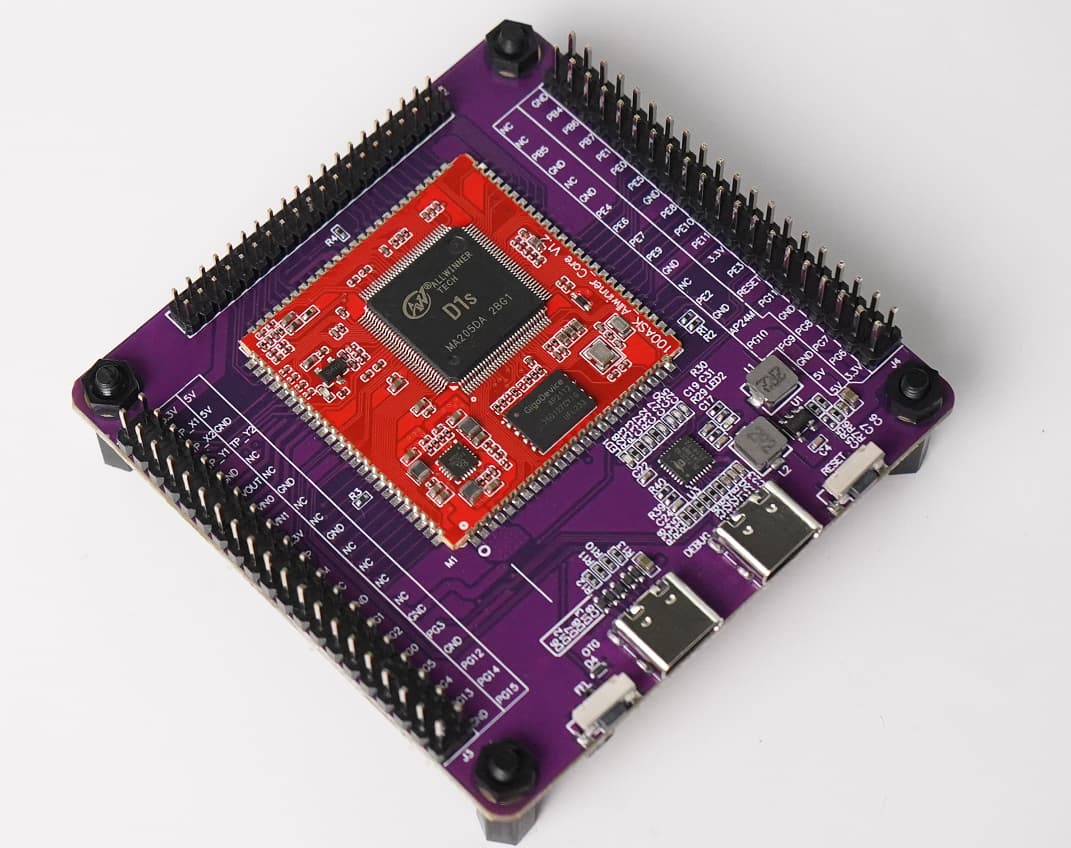

DongshanPI-D1s – An Allwinner D1s RISC-V development board designed to teach programming

The DongshanPI-D1s development board is comprised of a soldered-on Allwinner D1s RISC-V system-on-module board (SoM) and a carrier board with two 40-pin headers and a 2.0mm dedicated header. This development board is specifically designed to teach programming with a focus on the RISC-V architecture. The development board was designed by 100ask. They previously designed the Dongshan NeZha STU a development board based on the Allwinner D1. The main difference between the two is that 100ask did not include the Ethernet and HDMI interfaces on the DongshanPI-D1s board. The pinout of the headers is also slightly different because they opted to make the headers compatible with the widely used 40-pin GPIO from Raspberry Pi single board computers. DongshanPI-D1s preliminary specifications: D1s Core Lite SoC – Allwinner D1s single-core XuanTie C906 64-bit RISC-V processor @ 1.0 GHz with with 32 KB I-cache + 32 KB D-cache Memory – 64 MB DDR2 (SIP) […]

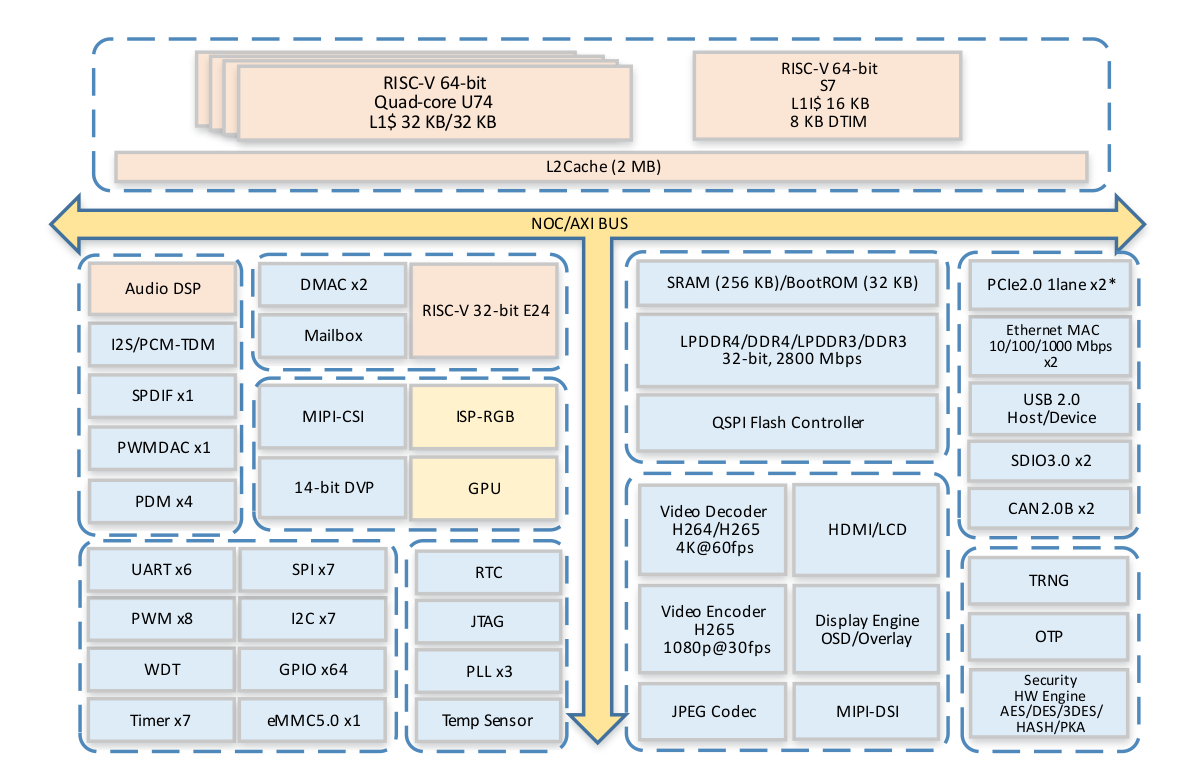

StarFive JH7110 RISC-V processor specifications released

With the Star64 and VisionFive 2 single board computers, we’ve already got two hardware platforms based on the StarFive JH7110 quad-core RISC-V processor, but somehow we did not get the detailed specifications of the new processor, and some details such as the presence of AI accelerators or exact PCIe specifications were lacking. Some documentation for the StarFive JH7110 processor has been released and answers some of those questions. It’s actually an SoC with six RISC-V cores, of which four 64-bit RISC-V cores run the main OS, plus a 64-bit RISC-V monitoring core, and a 32-bit RISC-V real-time core. The AI accelerators found in the JH7100 (Neural Network Engine and NVDLA) appear to be gone for good, and there are two 1-lane PCIe 2.0 interfaces up to 5 Gbps each. StarFive JH7110 specifications: CPU sub-system Quad-core 64-bit RISC-V SiFive U74 (RV64GC) processor @ up to 1.5 GHz with 32KB D-Cache, 32KB […]

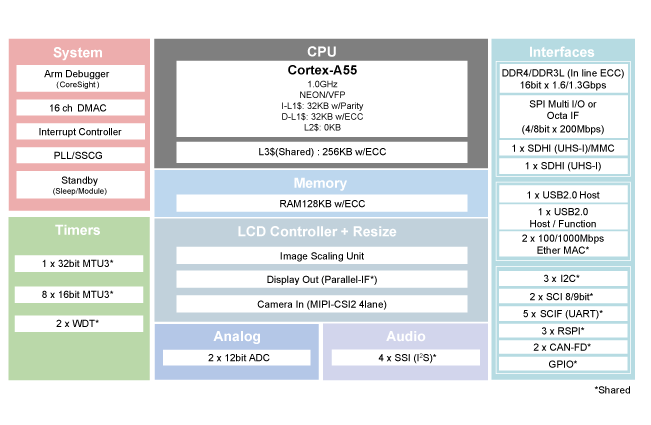

Renesas RZ/A3UL Cortex-A55 CPU runs RTOS for HMI with quick startup times

Renesas RZ/A3UL is a single-core Cortex-A55 processor clocked at up to 1 GHz designed to run FreeRTOS or Azure RTOS on high-definition (1280×800) HMI solutions requiring quick startup times such as industrial equipment, home appliances, office automation equipment, audio equipment, and POS terminals. The new RZ/A3UL processor family has the same peripheral functions and package pin assignments as the RZ/G2UL (Arm Cortex-A55/M33) and RZ/Five (RISC-V) families targeting Linux-based HMI applications. Renesas also designed a SMARC 2.1 compliant System-on-Module (SoM) based on the Renesas RZ/A3UL microprocessor to speed up time to market. Renesas RS/A3UL specifications: CPU – Single-core Arm Cortex-A55 processor @ up to 1.0 GHz with 32KB I-cache with parity, 32KB D-cache with ECC, 256KB L3 cache with ECC Internal Memory – 128KB SRAM with ECC Memory & Storage I/F 16-bit DDR4-1600 or DDR3L-1333 memory interfaces with in-line ECC; up to 4GB RAM Octal Peripheral Interface (OPI) for flash or […]

RISC-V design challenge – Get a free board, RISC-V chips, and cash prizes

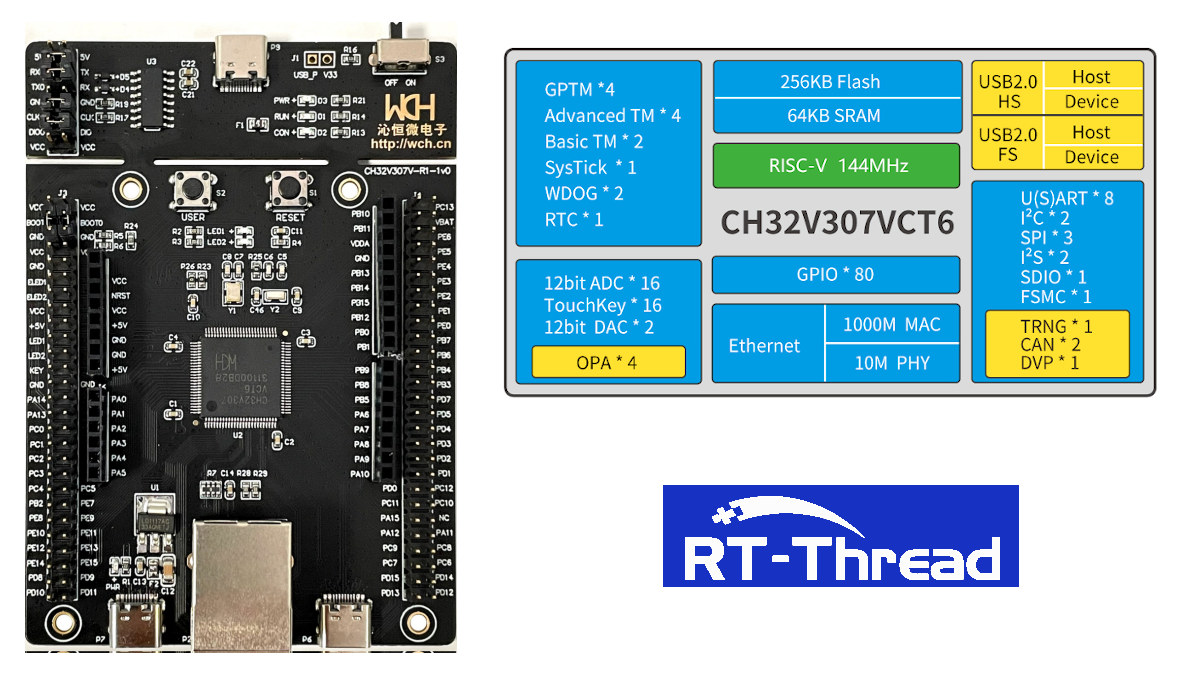

A little while ago, I wrote about WCH CH32V307 32-bit RISC-V MCU that was found in a board with eight UART ports that could be controlled over Ethernet or USB, and the company has released some source code to use the board while inviting the community to submit pull requests to the project. But now WCH, RT-Thread, LCSC, and EasyEDA have joined hands to launch the RISC-V design challenge where the companies will provide a free board or two RISC-V chips to selected participants, as well as cash prizes with up to $1000 offered to the best projects. The companies have prepared 300 boards and 200 chips for this contest. All you need to do to get a chance to get either one CH32V307V-EVT-R1 development board or two CH32V307 RISC-V microcontrollers is to enter your contact and project details in this Google form by April 30, 2022. The conditions are […]

RISC-V or Arm? This tiny 4x4cm Linux board with WiFi offers both options

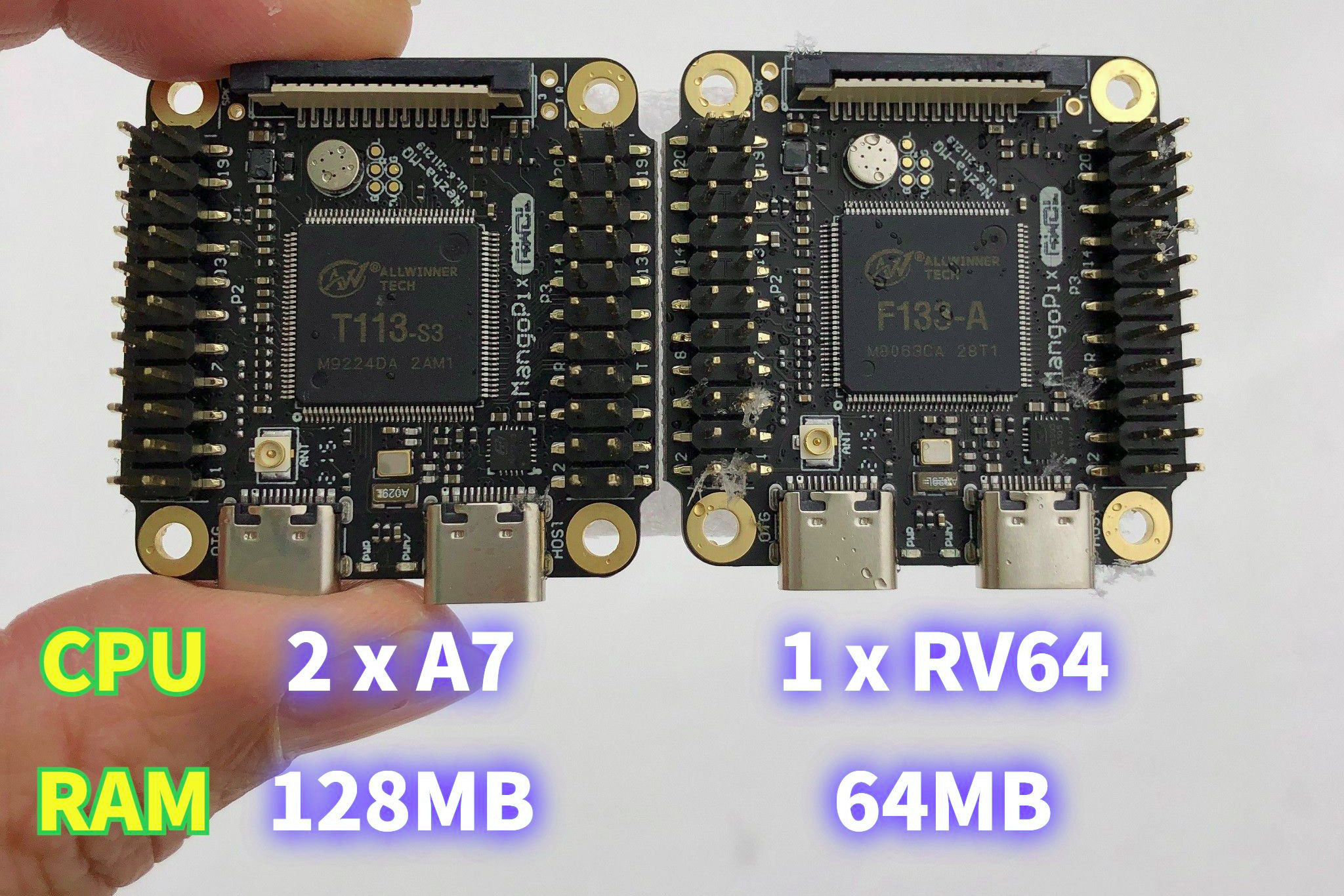

Last fall, we wrote about Allwinner D1s/F133-A RISC-V processor and the upcoming MangoPi MQ1, a tiny 4x4cm board based on the processor. The board is not for sale, but we have more details, and the company is also working on an Arm version equipped with Allwinner T113-S3 dual-core Cortex-A7 processor that is pin-to-pin compatible with F133-A SoC. The Allwinner F133-A board will finally be called MangoPi Nezha-MQ, or MangoPi MQ for shorts, and come with 64MB on-chip RAM while the Allwinner T113-S3 board, with 128MB on-chip RAM, will be named MangoPi MQ-Dual. Both are fitted with a Realtek RTL8189-based Wi-Fi module, offer display and camera interfaces, two USB-C interfaces, and headers for GPIOs. MangoPi MQ RISC-V or Arm Linux board MangoPi MQ/MQ-Dual specifications: SoC (one or the other) MangoPi MQ – Allwinner D1s/F133-A 64-bit RISC-V processor @ 1 GHz with 64 MB DDR2 MangoPi MQ-Dual – Allwinner T113-S3 32-bit dual-core […]

Allwinner T113-S3 dual-core Cortex-A7 SoC features 128MB DDR3, targets automotive and industrial applications

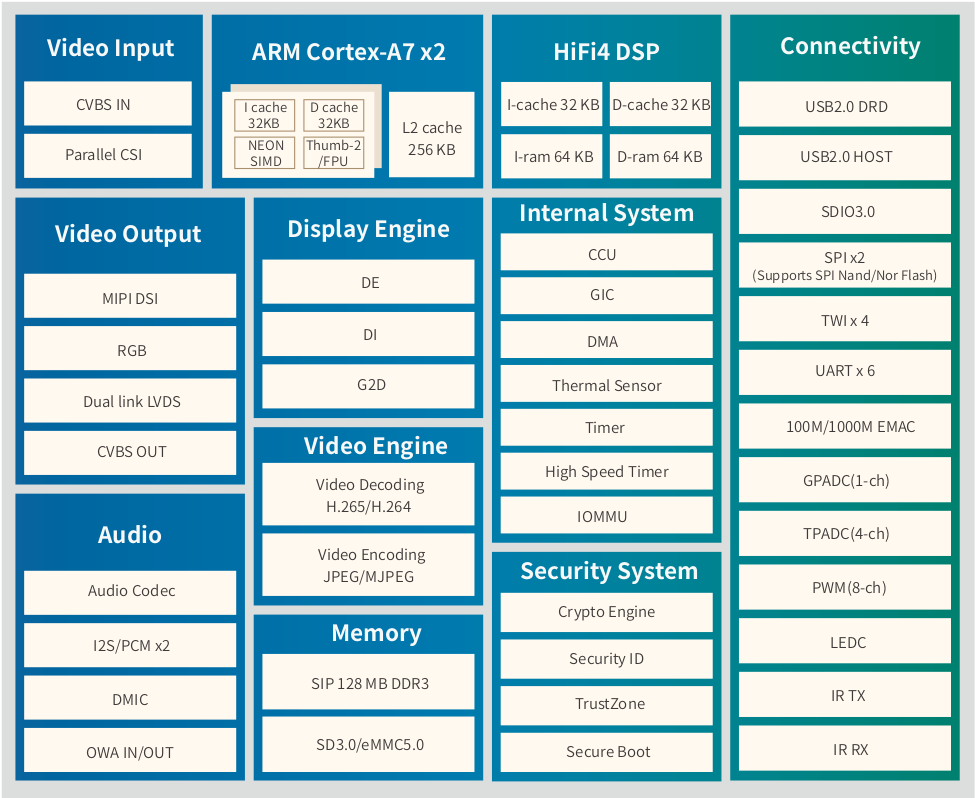

Allwinner T113-S3 is a dual-core Cortex-A7 processor with 128MB DDR3 on-chip memory that is designed for smart control and HMI applications in the automotive and industrial sectors. At first glance, the new processor looks quite similar to Allwinner S3, but with twice the number of cores. However there’s more to it, as a a HiFi4 DSP has been added for smart audio applications, the H.264 encoder is gone replaced by an MPJEG encoder, and the company claims support for “industrial level working temperature”, plus a 10-year life cycle. among other differences. Allwinner T113-S3 specifications: CPU – Dual-core Arm Cortex-A7 with 32 KB L1 I-cache + 32 KB L1 D-cache per core, and 256 KB L2 cache DSP – Single-core HiFi4 Memory – 128 MB DDR3 Storage I/F – SD3.0/eMMC 5.0, SPI Nor/NAND Flash Video Decoding – H.264, H.265, MPEG-1/2/4, (M)JPEG, VC1 up to 1080p60 Encoding – JPEG/MJPEG up to 1080p60 […]

congatec launches 10 new COM-HPC and COM Express Computer-on-Modules with 12th Gen Intel Core processors (Sponsored)

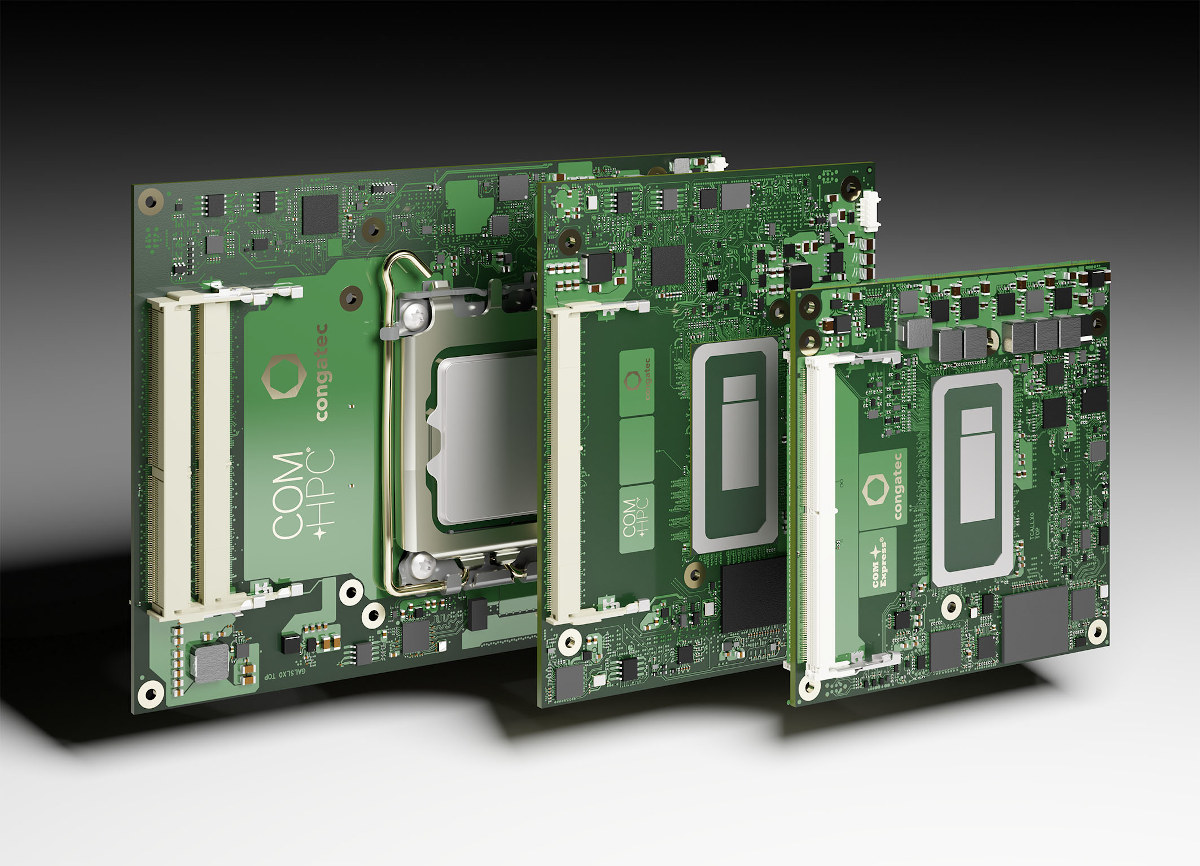

congatec – a leading vendor of embedded and edge computing technology – introduces the 12th Generation Intel Core mobile and desktop processors (formerly code-named Alder Lake) on 10 new COM-HPC and COM Express Computer-on-Modules. Featuring the latest high-performance cores from Intel, the new modules in COM-HPC Size A and C as well as COM Express Type 6 form factors offer major performance gains and improvements for the world of embedded and edge computing systems. Most impressive is the fact that engineers can now leverage Intel’s innovative performance hybrid architecture. Offering up to 14 cores/20 threads on BGA and 16 cores/24 threads on desktop variants (LGA mounted), the 12th Gen Intel Core processors provide a quantum leap [1] in multitasking and scalability levels. Next-gen IoT and edge applications benefit from up to 6 or 8 (BGA/LGA) optimized Performance-cores (P-cores) plus up to 8 low-power Efficient-cores (E-cores) and DDR5 memory support to […]