Linus Torvalds has just announced the release of Linux 5.16: Not a lot here since -rc8, which is not unexpected. We had that extra week due to the holidays, and it’s not like we had lots of last-minute things that needed to be sorted out. So this mainly contains some driver fixes (mainly networking and rdma), a cgroup credential use fix, a few core networking fixes, a couple of last-minute reverts, and some other random noise. The appended shortlog is so small that you might as well scroll through it. This obviously means that the merge window for 5.17 opens tomorrow, and I’m happy to say I already have several pending early pull requests. I wish I had even more, because this merge window is going to be somewhat painful due to unfortunate travel for family reasons. So I’ll be doing most of it on the road on a laptop […]

Sifive Essential 6-Series RISC-V processors target Linux, real-time applications

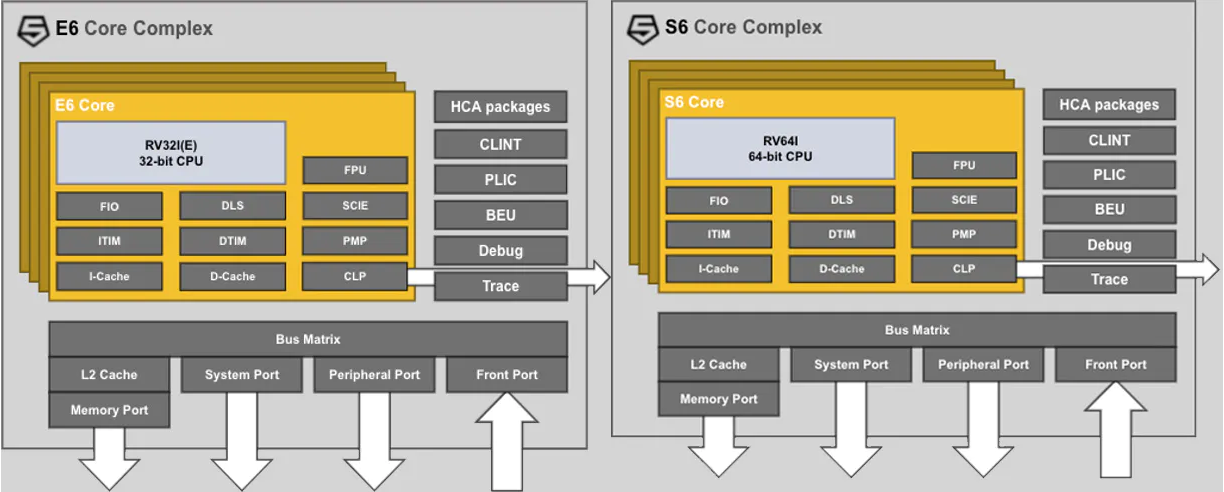

SiFive has been busy. Just a few days after SiFive Performance P650 announcement, the company has announced the SiFive Essential 6-Series RISC-V processor family starting with four 64-bit/32-bit real-time core, and two Linux capable application cores, plus the SiFive 21G3 release with various improvements to existing families. SiFive Essential 6-Series range of RISC-V processors There Essential 6-Seris family is comprised of three sub-families with two processors each: E6 Series with 1.91 DMIPS/MHz, 3.69 CoreMark/MHz E61-MC – Quad-core 32-bit embedded processor E61 – Mid-range performance 32-bit embedded processor (one-core) S6 Series with 2.07 DMIPS/MHz, 3.73 CoreMark/MHz S61-MC – Quad-core 64-bit embedded processor S61 – Mid-range performance 64-bit embedded processor (one-core) U6 Series with 2.07 DMIPS/MHz, 3.73 CoreMark/MHz U64-MC – Quad-core 64-bit application processor U64 – Mid-range performance Linux-capable processor (one-core) E6-Series and S6 Series real-time processors have practically the same features except for the 32-bit and 64-bit cores, and a different […]

SiFive Performance P650 RISC-V core to outperform Arm Cortex-A77 performance per mm2

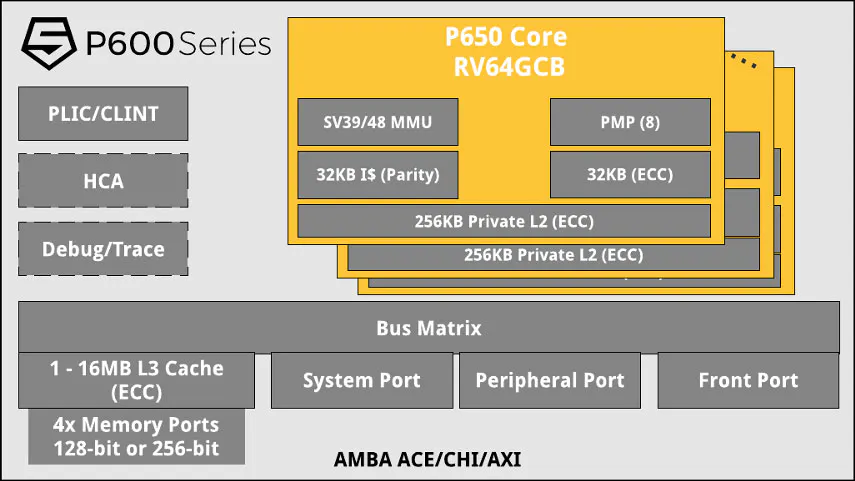

About six months have passed since the SiFive announcement of the Performance P550 “fastest 64-bit RISC-V processor” ever, and the company has now introduced an even faster RISC-V core with the Performance P650 that’s expected to match Cortex-A77 performance. Building upon the Performance P550 design, the SiFive Performance P650 is scalable to sixteen cores using a coherent multicore complex, and delivers a 40% performance increase per clock cycle based on SiFive engineering estimated performance in SPECInt2006/GHz, thanks to an expansion of the processor’s instruction-issue width. The company compares P650 to the Arm family by saying it “maintains a significant performance-per-area advantage compared to the Arm Cortex-A77”. SiFive Performance P650 key features: 64-bit RISC-V (RV64GCB) core Sv39/Sv48 Virtual Memory Support Multi-core, multi-cluster processor configurations with up to 16 cores Performance > 11 SpecINT2006/GHz Thirteen stage, four-issue, out-of-order pipeline tuned for scalable performance Private L2 Caches and Streaming Prefetcher for improved memory […]

Ubuntu 20.04/21.04 64-bit RISC-V released for QEMU, HiFive boards

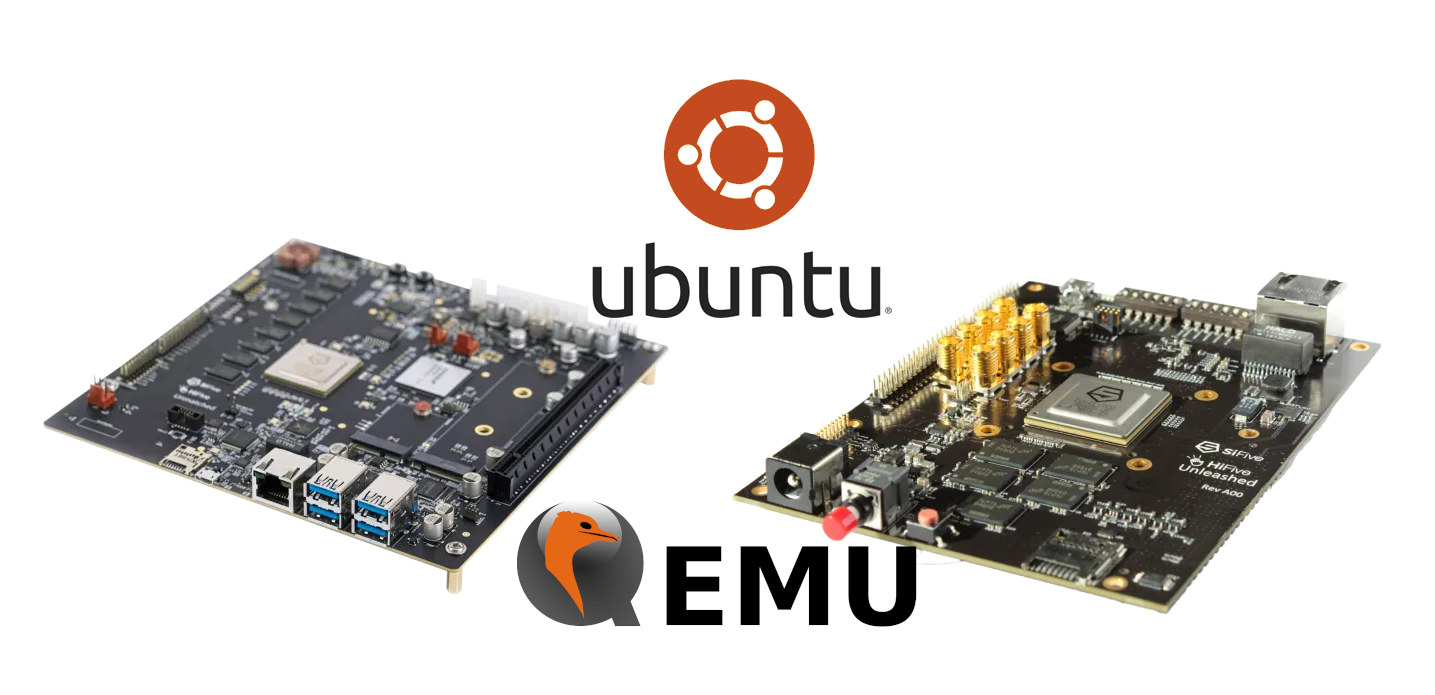

Let’s a lot of excitement around RISC-V open architecture, but a lot of work still needs to be done to bring the ecosystem to level with Arm or x86 architecture from the silicon to the software. Progress is made step-by-step and one of these steps is Canonical released Ubuntu 64-bit RISC-V (RISCV64) images for some of SiFive HiFive boards, as well as QEMU open-source emulator. Specifically, Canonical released an Ubuntu 20.04.2 LTS image for HiFive Unleashed & QEMU, and an Ubuntu 21.04 image for HiFive Unleashed, HiFive Unmatched, and QEMU. Note those are only server images, and there’s no desktop image yet like for Ubuntu 21.04 on Raspberry Pi 2/3/4. It’s been possible to run RISC-V Linux in QEMU for at least three years, but when I tried it was a minimal system based on Busybox, so let’s try again with Ubuntu 21.04 following the instructions provided on Discourse. I […]

SiFive Performance P550 is the fastest 64-bit RISC-V processor so far

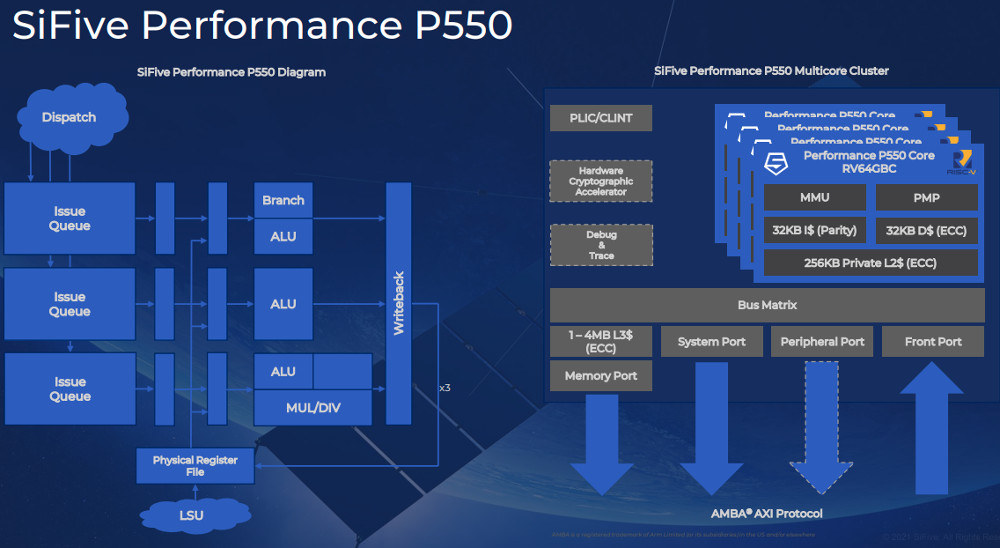

SiFive has announced two RISC-V “Performance” cores with Performance P550 that should be the fastest 64-bit RISC-V processor so far with a SPECInt 2006 score of 8.65/GHz, as well as a Performance P270 Linux capable processor with full support for the RISC-V vector extension v1.0 rc. SiFive Performance P550 P550 highlights: RISC-V RV64GBC ISA 13 stage, 3-issue high-performance out-of-order pipeline Supports multicore coherence with up to 4 cores in a core complex Private 32KB+32KB L1 cache and a private 256KB L2 cache per core Up to 4MB L3 cache in a four-core cluster SPECint 2006 – 8.65/GHz 2.4 GHz in 7nm with a footprint of less than 0.25 mm SiFive compares the Performance P550 core to Arm’s Cortex-A75 with higher performance in SPECint2006 and SPECfp2006 integer/floating-point benchmark, all a much smaller area which would enable a quad-core P550 cluster on about the same footprint as a single Cortex-A75 core. There […]

RISC-V International to give away 1,000 RISC-V development boards

The best way for a new platform to get good software support is to bring hardware into the hands of developers. That’s exactly what RISC-V International is doing by inviting developers to sign up for a RISC-V developer board sponsored by RISC-V and contributing members. There are 1,000 boards on offer with 1GB to 16GB RAM depending on the target project from five companies and organizations namely Allwinner, Beagleboard.org, SiFive, Microchip Technology (previously Microsemi), and RIOS. Here are the stated goals of the giveaway: Spur innovation Enable new opportunities for the next generation of developers to work with the RISC-V ISA Provide a platform For testing To write programs that run on RISC-V Develop software Integrate existing software stacks Optimize ecosystem software Share feedback on the product such as ease to integrate software stacks, develop and test extensions, etc. The company did not provide an exact list of development board […]

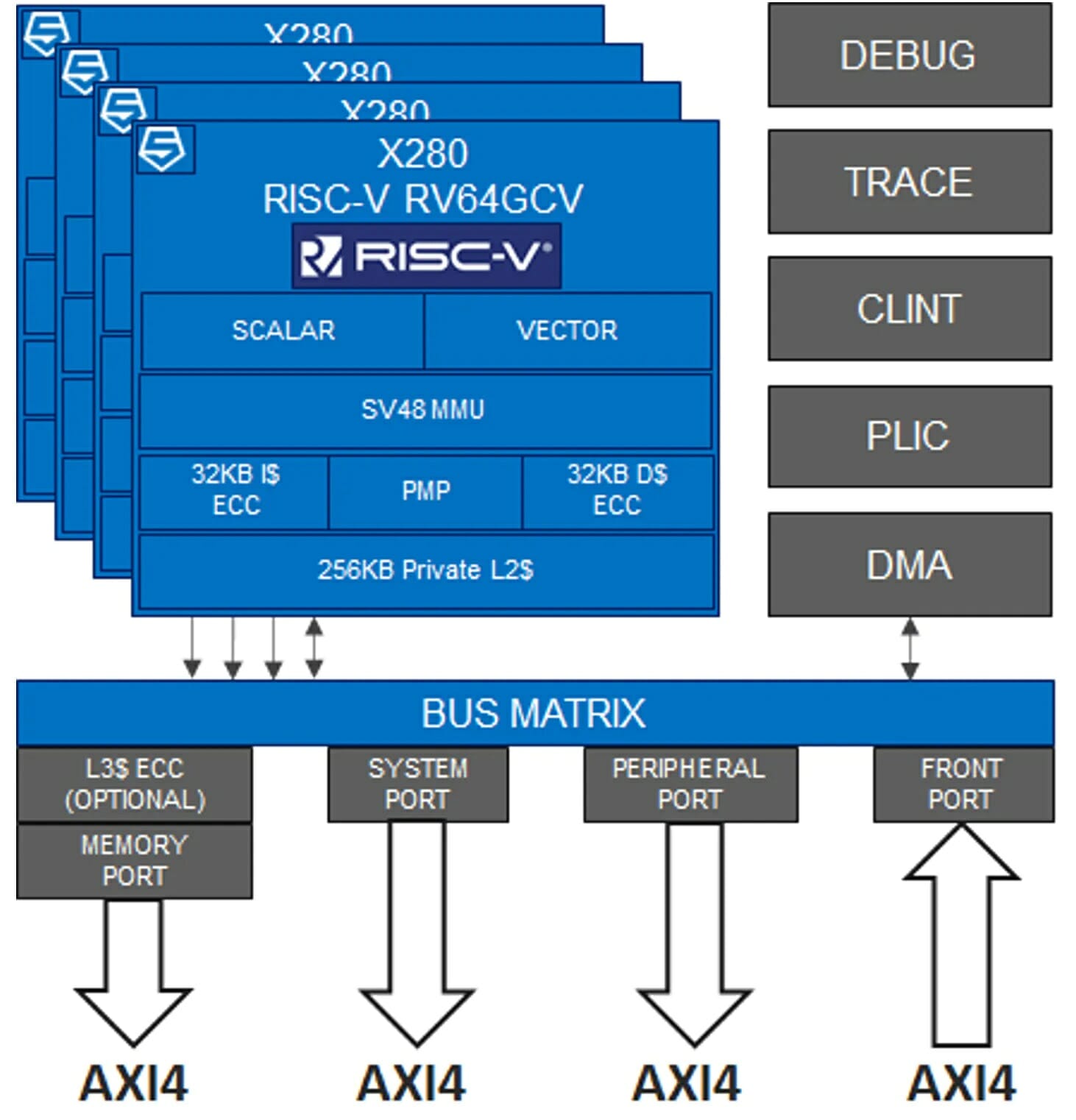

SiFive Intelligence X280 64-bit RISC-V processor integrates AI extensions

The last RISC-V core announced by SiFive was the U8-Series out-of-order RISC-V Core IP that aims to compete against Arm Cortex-A72 Core. But in their latest announcement, the company built upon the 64-bit RISC-V U7-series with the SiFive Intelligence X280 multi-core, Linux capable RISC-V processor adding vector extensions and SiFive Intelligence Extensions, and optimized for AI/ML compute at the edge. SiFive Intelligence X280 key features: 64-bit RISC-V ISA with 8-stage dual-issue in-order pipeline, coherent multi-core, Linux capable based on U7 series core. SiFive Intelligence Extensions for ML workloads – BF16/FP16/FP32/FP64, int8 to 64 fixed-point data types 512-bit vector register length – Variable-length operations, up to 512-bits of data per cycle High-performance vector memory subsystem Memory parallelism provides cache miss tolerance Virtual memory support with precise exceptions Up to 48-bit addressing SiFive Intelligence includes software solutions to leverage the X280’s features and provide “great AI inference performance” using TensorFlow Lite. No […]

SiFive Core IP 21G1 release improves bit manipulation, floating-point unit, reduces code footprint

As SiFive has a portfolio of RISC-V cores ranging from low-power E2-series to high-performance U8-series cores with performance similar to Cortex-A7x cores, the company has not released new cores for a while, and instead focuses on improving their current RISC-V cores. We saw that last year with the SiFive 20G1 release that improved performance & efficiency, and lowered the silicon area for the same features set. SiFive further improved its cores and ecosystem with the latest SiFive 21G1 release. The main new features brought by SiFive 21G1 release include: SiFive 2-Series and 7-Series processors are now available with the “Bit Manipulation” extension, RV32B, with Zba and Zbb extensions. This can accelerate Cryptographic Hash algorithms by up to 35% Support for FP16 half-precision floating-point computation in order to reduce memory size and power consumption, and for some AI workloads The memory map is now fully programmable SiFive RV64 processors support up […]