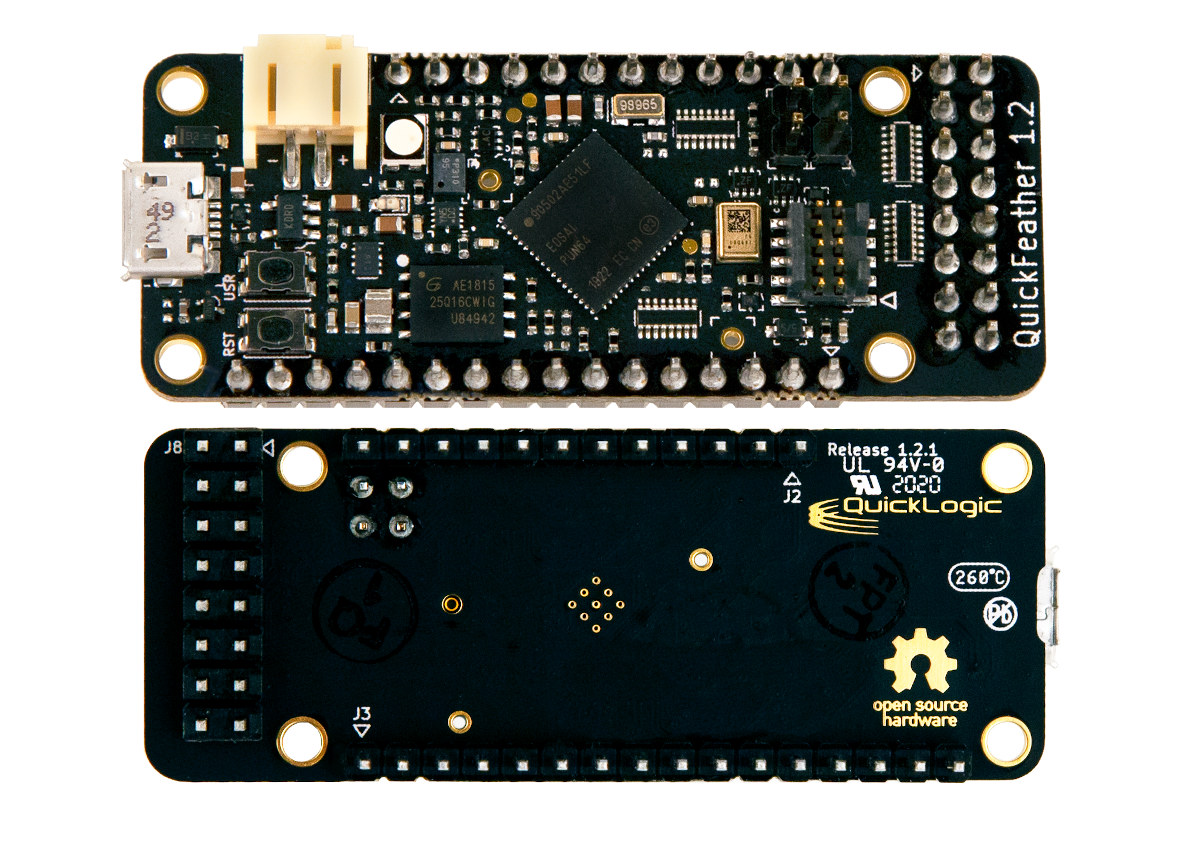

Yesterday, I wrote about what I felt what a pretty unique board: Evo M51 board following Adafruit Feather form factor, and equipped with an Atmel SAMD51 Cortex-M4F MCU and an Intel MAX 10 FPGA. But less than 24 hours later, I’ve come across another Adafruit Feather-sized Cortex-M4F board with FPGA fabric. But instead of using a two-chip solution, QuickLogic QuickFeather board leverages the company’s EOS S3 SoC with a low-power Cortex-M4F core and embedded FPGA fabric. QuickFeather board QuickFeather specifications: SoC – QuickLogic EOS S3 with Arm Cortex-M4F Microcontroller @ up to 80 MHz and 512 Kb SRAM, plus an embedded FPGA (eFPGA) with 2400 effective logic cells and 64Kb RAM Storage – 16Mbit SPI NOR flash USB – Micro USB port with data signals tied to eFPGA programmable logic Sensors – Accelerometer, pressure sensor, built-in PDM microphone Expansion I/Os – Breadboard-compatible 0.1″ (2.54 mm) pitch headers including 20 Feather-defined […]

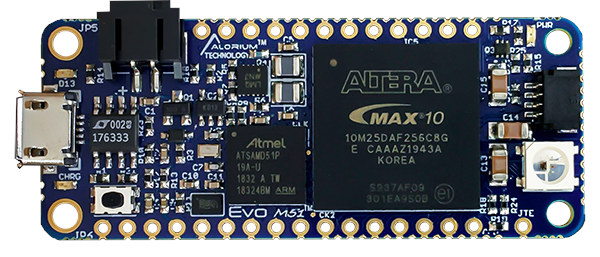

Feather-Sized Evo M51 Board Combines Atmel SAMD51 MCU with Intel MAX 10 FPGA

Arduino unveiled its first FPGA board around two years ago with MKR Vidor 4000 combining an Intel Cyclone FPGA with Microchip SAMD21 Cortex-M0+ MCU in a form factor similar to Arduino Zero. But in case you are looking for an even smaller Arduino compatible FPGA board, Alorium Technology’s Evo M51 might be exactly what you are after. The Adafruit Feather-sized board is equipped with an Atmel SAMD51 Arm Cortex-M4F microcontroller coupled with an Intel MAX 10 FPGA. Evo M51 specifications: MCU – Microchip (Atmel) SAMD51 Arm Cortex-M4F microcontroller clocked at 120 MHz with 512KB flash, 192 KB SRAM FPGA – Intel MAX 10 (10M25) FPGA with 25K LEs, 675Kbit block memory Storage – 2MB external flash USB – 1x micro USB port for power and programming I/O Digital 55x Total Digital I/O – 21x through-hole/castellated vias, 34x additional castellated-only 6x digital pins shared with analog pins 3.3V Inputs, 3.3V Outputs […]

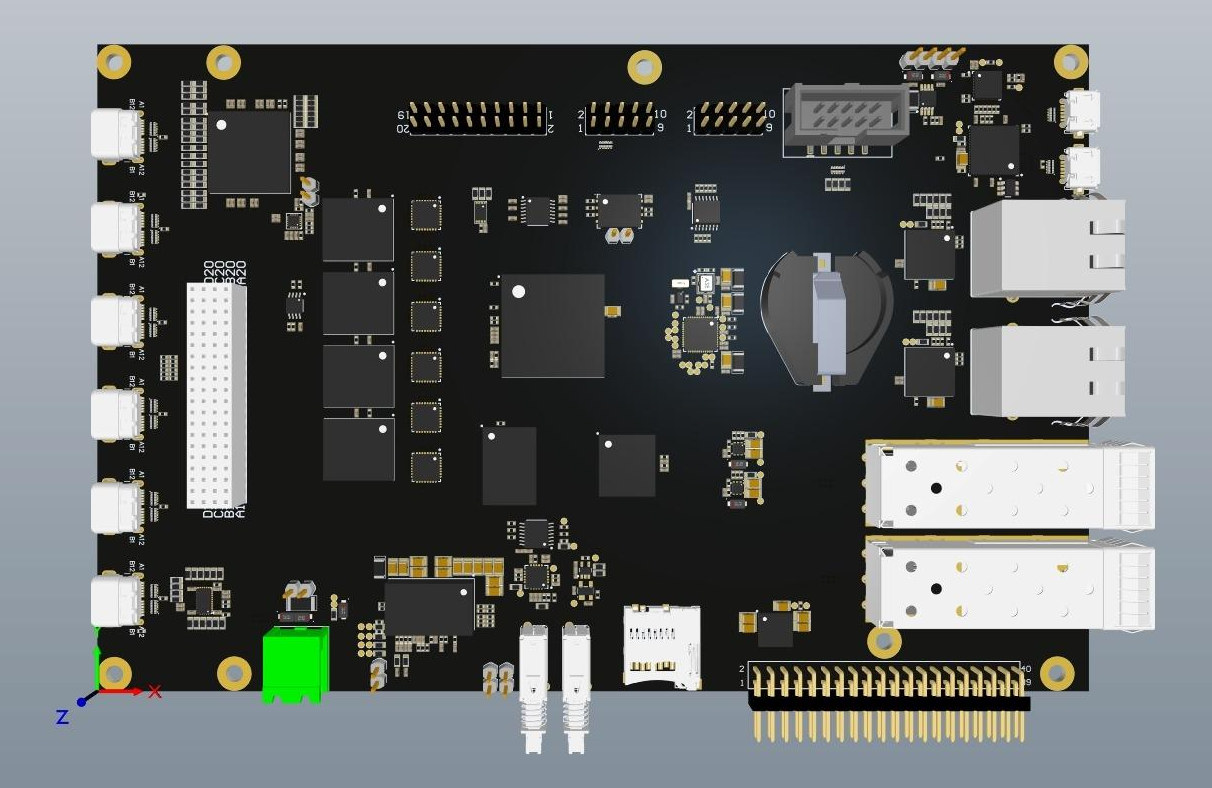

Upcoming SAVVY-V Open Source RISC-V Cluster Board Supports 10GbE via Microsemi PolarFire 64-bit RISC-V SoC

RISC-V based PolarFire SoC FPGA by Microsemi may be coming up in the third quarter of this year, but Ali Uzel has been sharing a few details about SAVVY-V advanced open-source RISC-V cluster board made by FOSOH-V (Flexible Open SOurce Hardware for RISC-V) community of developers. It’s powered by Microsemi Polarfire RISC-V SoC MPFS250T with four 64-bit RISC-V cores, a smaller RV64IMAC monitor core, and FPGA fabric that allows 10GbE via SFP+ cages, and exposes six USB Type-C ports. The solution is called a cluster board since up to six SAVVY-V boards can be stacked via a PC/104+ connector and interfaced via the USB-C ports. SAVVY-V cluster board preliminary features and specifications: SoC – Microsemi Polarfire RISC-V SoC MPFS250T with a quad-core 64-bit RV64IMAFDC (RV64GC) processor @ up to 667 MHz, a RV64IMAC monitor core, and FPGA fabric with 250K logic elements; 3.0 CoreMarks/MHz, 2.0 DMIPs/MHz; Also compatible with MPFS160T, […]

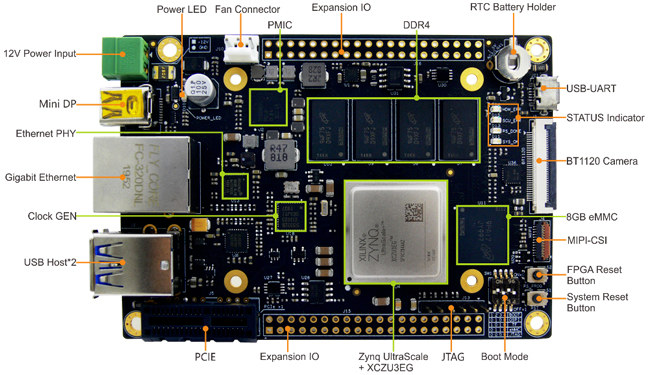

Zynq UltraScale+ Arm FPGA FZ3 Deep Learning Accelerator Card Supports Baidu Brain AI Tools

MYIR’s FZ3 card is a deep learning accelerator board powered by Xilinx Zynq UltraScale+ ZU3EG Arm FPGA MPSoC delivering up to 1.2TOPS for artificial intelligence products based on Baidu Brain AI open platform. The FZ3 card also features 4GB RAM, 8GB eMMC flash, USB 2.0 & USB 3.0 ports, Gigabit Ethernet, DisplayPort (DP) output, PCIe interface, MIPI-CSI and more. MYIR FZ3 card specifications: SoC – Xilinx Zynq UltraScale+ XCZU3EG-1SFVC784E (ZU3EG) MPSoC Quad-core Arm Cortex-A53 @ 1.2 GHz Dual-core Arm Cortex-R5 processor @ 600MHz Arm Mali-400MP2 GPU FPGA fabric System Memory – 4GB DDR4 Storage – 8GB eMMC flash, 32MB QSPI flash, 32KB EEPROM, MicroSD card slot Video Output – 1x Mini DisplayPort up to 4Kp30 Camera I/F 1 x MIPI-CSI Interface (25-pin 0.3mm pitch FPC connector) 1 x BT1120 Camera Interface (32-pin 0.5mm pitch FPC connector) Connectivity – 1x Gigabit Ethernet USB – 1x USB 2.0 Host, 1x USB 3.0 Host […]

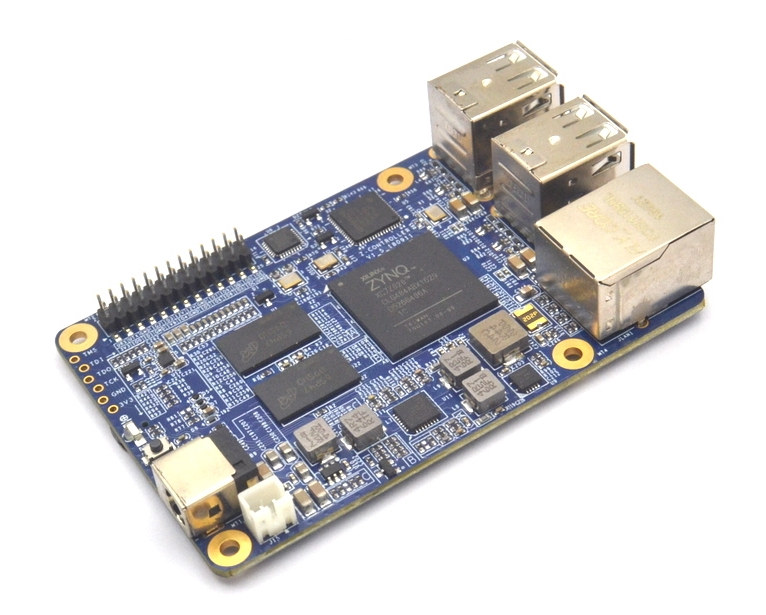

Sipeed TANG Hex is a Low-Cost Xilinx Zynq-7020 Arm FPGA Board

Last year, Sipeed launched a $5 FPGA board called Sipeed Tang and based on an entry-level Gowin GW1N-1-LV FPGA. But I had not noticed the company had also worked on a more powerful, yet still low-cost Xilinx Zynq-7020 board in a business card form factor not too dissimilar from the Raspberry Pi model B form factor. Meet Sipeed TANG Hex. So far a low-cost Zynq-7010 or Zynq-7020 board met you had to spend $99 to $199 with products such as MyIR Z-Turn and Digilent PYNQ-Z1. But Sipeed Tang HEX can be purchased for as little as $73 shipping on Aliexpress, or 439 RMB ($62) on Taobao for people based in mainland China. It might be tempting to get a low-cost board to get started, but is it worth it? Read on to find out. Sipeed TANG Hex specifications: SoC – Xilinx Zynq-7020 (XC7Z020-1CLG484) dual-core Arm Cortex-A9 processor and FPGA with […]

zGlue Launches the Open Chiplet Initiative in Collaboration with Google and Antmicro

We first covered zGlue’s ZiP (zGlue Integration Platform) in 2018 as the company introduced its multi-chip module similar to SiP (system-in-package) via a crowdfunding campaign. Just like SiP, the technology packages several components into a single package, but costs have been brought down to enable low-volume production of custom chips for a reasonable price. Since then the company announced new ZiP multi-chip modules such as nRF52832 based Omnichip and the FPGA, Arm or/and RISC-V based GEM ASIC by Antmicro. The company recently announced the Open Chiplet Initiative, a collection of open-source designs, tools and file formats, launched in collaboration with Google and Antmicro. There are four main types of tools within the Open Chiplet Initiative: Open Chiplet Interfaces – Currently only ZEF (zGlue Chiplet Info Exchange Format) is provided. It defined the part numbers, pins, and mechanical dimensions of various parts. The ZEF specification can be found on Github. Design […]

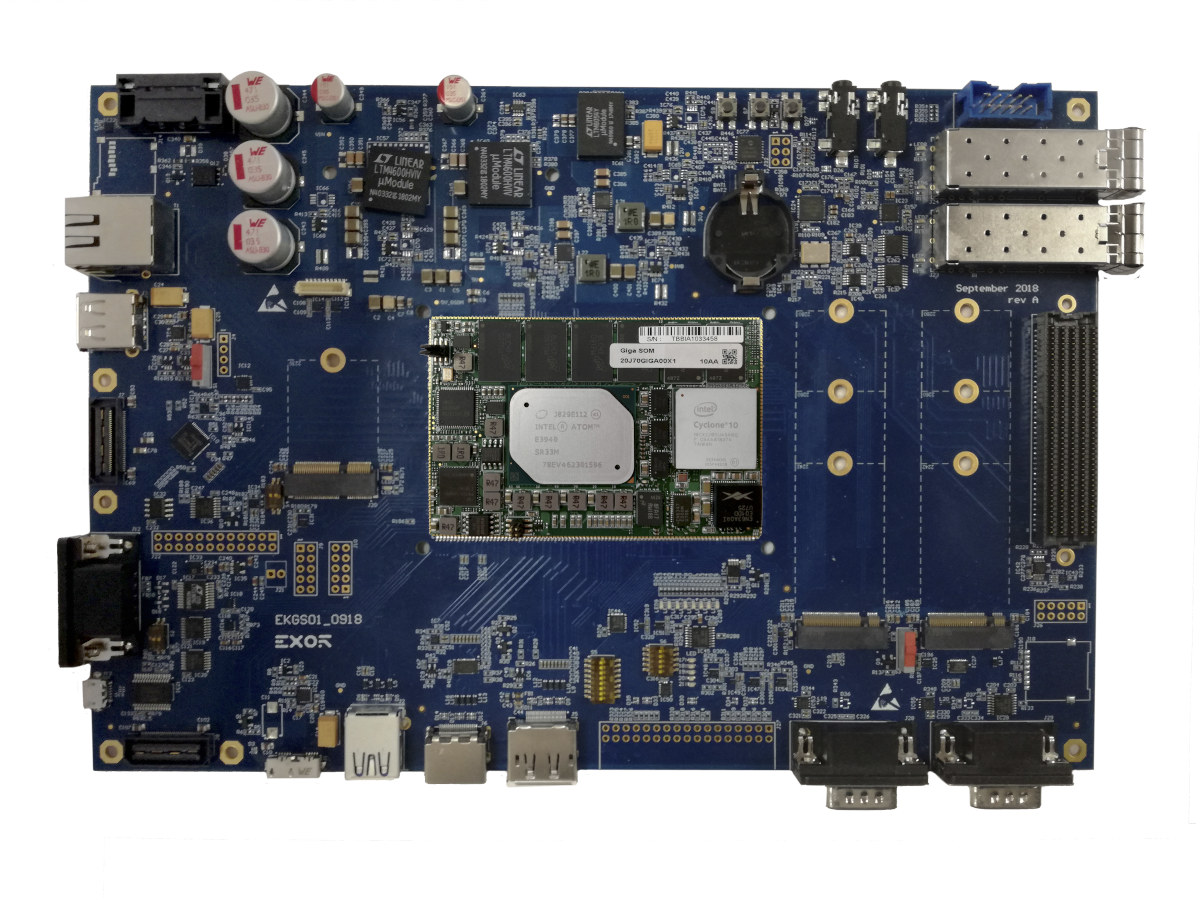

Exor GigaSOM GS01 SoM and Devkit Combine Intel Atom E39xx CPU and Cyclone 10 GX FPGA

EXOR International has worked in collaboration with Arrow Electronics to design and manufacture GigaSOM GS01 system-on-module combining an Intel Atom E39xx Apollo Lake processor and Cyclone 10 GX FPGA. The module and corresponding development kit are specifically designed for smart factory & “Industrie 4.0” applications with the processor running Intel’s time-coordinated computing plus a real-time “IoT stack”, and the FPGA supporting IEEE 802.1 time-sensitive networking (TSN) and 10Gbps connectivity. GigaSOM GS01 module specifications: Apollo Lake SoC (one or the other) Intel Atom x5-E3930 dual-core processor @ 1.3 GHz / 1.8 GHz (Turbo) with 12EU Intel HD Graphics 500; 6.5W TDP Intel Atom x5-E3940 quad-core processor @ 1.6 GHz / 1.8 GHz with 12EU Intel HD Graphics 500; 9.5W TDP Intel Atom x7-E3950 quad-core processor @ 1.6 GHz / 2.0 GHz with 18EU Intel HD Graphics 505; 12W TDP FPGA – Intel Cyclone 10 GX up to 220 KLE System Memory […]

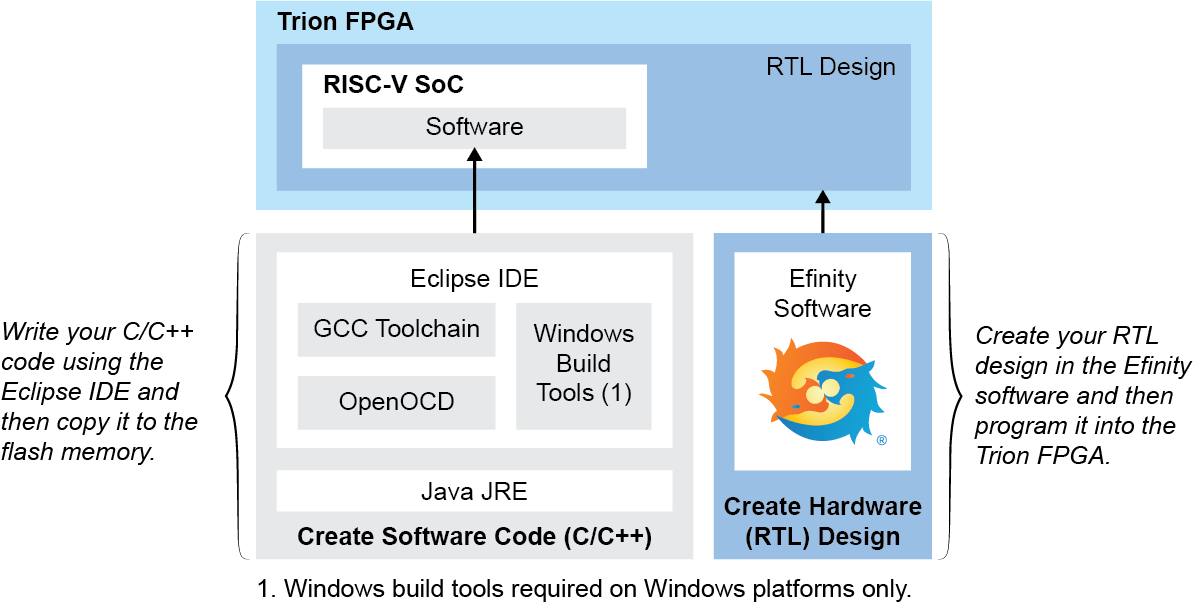

Efinix Releases Three RISC-V Software-Defined SoC’s Optimized for Trion FPGA’s

Efinix has announced three RISC-V Software-defined SoC’s based on Charles Papon’s VexRiscv core and optimized for the company’s Trion T8 to T120 FPGA’s. VexRiscv is a 32-bit RISC-V CPU using RISCV32I ISA with M and C extensions, has five pipeline stages (fetch, decode, execute, memory, and writeback), and a configurable feature set. Each SoC includes a RISC-V core, memory, as well as various I/O and interfaces. Key features for each of three RISC-V SoC’s: Ruby SoC FPGA footprint – ~12K LEs/78 RAM blocks Performance – 50 MHz (1.16 DMIPS/MHz) Memory – 4 KB on-chip RAM, up to 3.5 GB DDR DRAM Peripherals – 16x GPIO, Timer, PLIC, 3x SPI masters, 3x I2C masters/slaves, 2x UARTs 1x AXI4, 2x APB3 user peripherals Target applications – real-time system controls and image signal processing. Jade SoC FPGA footprint – ~7K LEs/93 RAM blocks Performance – 50 MHz (1.2 DMIPS/MHz) Memory – 32 KB […]