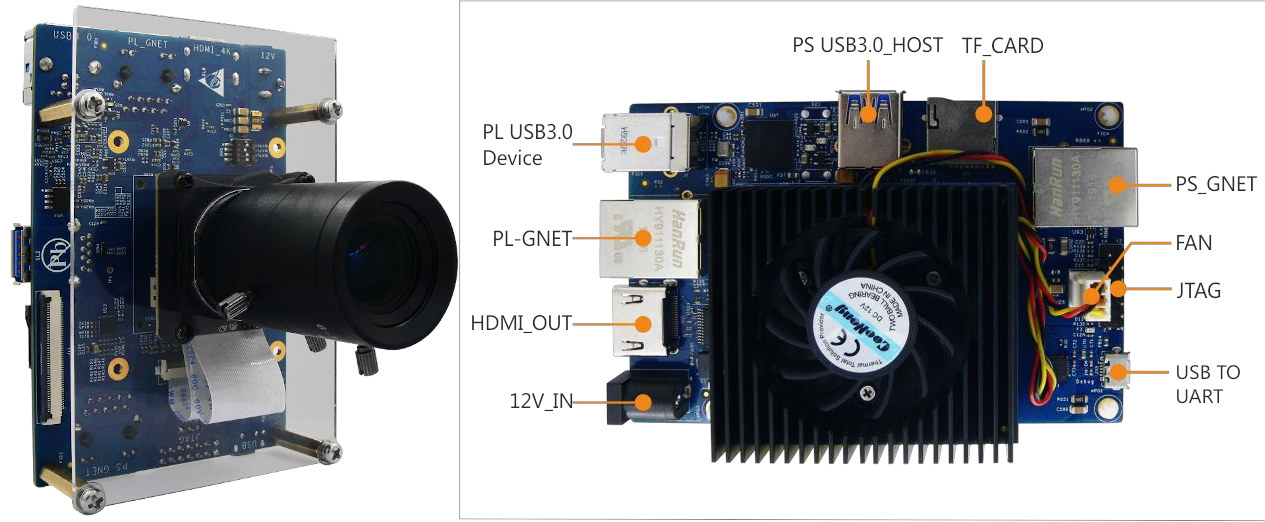

Last year, MyIR Tech introduced MYD-CZU3EG development board powered by a Xilinx Zynq UltraScale+ ZU3EG MPSoC with Arm Cortex-A53 cores and FPGA fabric designed for applications such as cloud computing, machine vision, flight navigation, and other complex embedded applications. The company has now announced another Zynq Ultrascale+ ZU3EG based platform dedicated to machine vision. The VECP Starter Kit (Vision Edge Computing Platform) is comprised of MYD-CZU3EG-ISP development board fitted with the company’s MYC-CZU3EG Zynq UltraScale+ MPSoC CPU module, a fansink, and a SONY IMX334 4K camera sensor. MYD-CZU3EG-ISP development board specification: MYC-CZU3EG SoM MPSoC – Xilinx Zynq UltraScale+ XCZU3EG-1SFVC784E (ZU3EG, 784 Pin Package) MPSoC with quad-core Arm Cortex-A53 processor @ 1.2 GHz, dual-core Cortex-R5 processor @ 600 MHz, Arm Mali-400MP2 GPU, and 16nm FinFET+ FPGA fabric (154K logic cells, 7.6 Mb memory, 728 DSP slices) System Memory – 4GB DDR4 @ 2,400MHz Storage – 4GB eMMC Flash, 128MB QSPI Flash […]

Radiona ULX3S Open Source Hardware ECP5 FPGA Development Board Launched for $99 and Up (Crowdfunding)

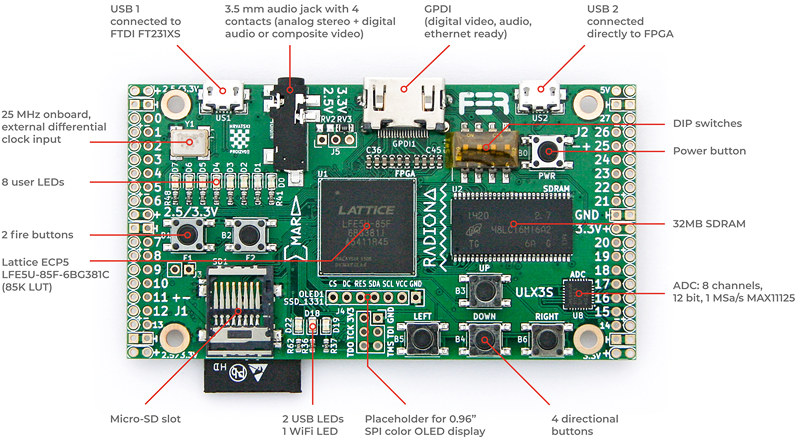

Last summer, we wrote about Radiona ULX3S education board combining a Lattice Semi ECP5 FPGA with an Espressif Systems ESP32 WiFi & Bluetooth WiSoC. Designed for a digital logic course at the University of Zagreb, the board is open-source hardware with KiCAD hardware design files released on GitHub, and programmable with the Arduino IDE (FPGArduino) and ProjectTrellis open-source toolchain. At the time, there was only a version based on Lattice ECP5 85F with 84K LUT, but they’ve now made versions with cheaper variants of ECP5 FPGA and launched the board on Crowd Supply. Radiona ULX3S specifications: FPGA (one of the other) Lattice ECP5 LFE5U-85F-6BG381C with 84K LUT Lattice ECP5 LFE5U-45F-6BG381C with 44K LUT Lattice ECP5 LFE5U-12F-6BG381C with 12K LUT System Memory – 32MB SDRAM @ 166 MHz Storage – 4–16MB Quad-SPI Flash for FPGA config and user data storage; MicroSD slot Audio – 3.5 mm jack with 4 contacts (analog […]

Register to the Embedded Online Conference for Free Before February 29th

Events such as the Embedded Linux Conference and Embedded Systems Conference take place in the US and Europe every year. There are plenty of talks and it’s certainly good for networking, but you need to travel to the event and the entrance fee to have access to all session costs several hundred dollars if you book early, and over one thousand dollars if you register close to the date of the event. Most ELC/ELCE videos usually end up on The Linux Foundation YouTube channel, but the Beningo Embedded Group and Embedded Related website decided to organize a similar conference happening online and simply called the “Embedded Online Conference“. The conference offers topics about embedded systems, DSP, machine learning and FPGA and will take place on May 20. There are currently 17 talks, but they are still calling for talks so more sessions may be added before the actual event. You’ll […]

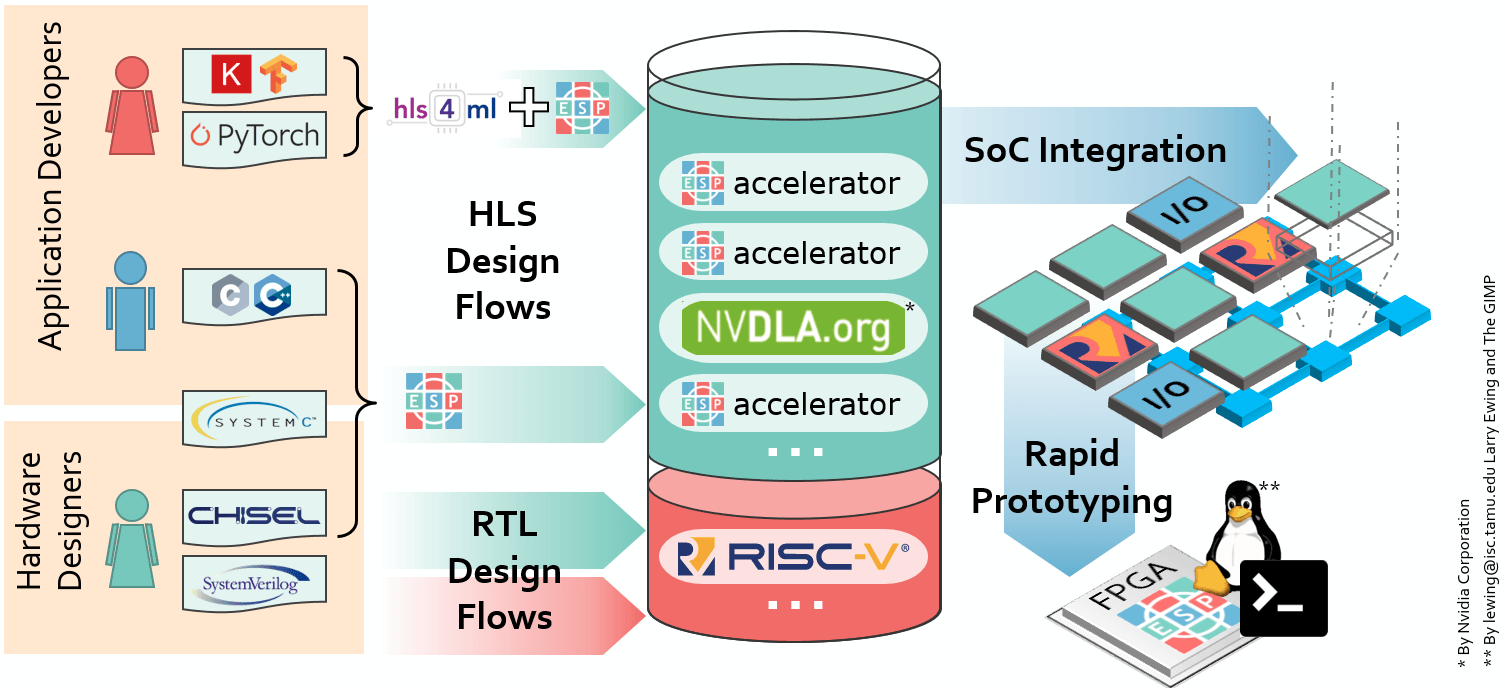

ESP Open Source Research Platform Enables the Design of RISC-V & Sparc SoC’s with Accelerators

FOSDEM 2020 will take place next week, and there will be several interesting talks about open-source hardware and software development. One of those is entitled “Open ESP – The Heterogeneous Open-Source Platform for Developing RISC-V Systems” with an excerpt of the abstract reading: ESP is an open-source research platform for RISC-V systems-on-chip that integrates many hardware accelerators. ESP provides a vertically integrated design flow from software development and hardware integration to full-system prototyping on FPGA. For application developers, it offers domain-specific automated solutions to synthesize new accelerators for their software and map it onto the heterogeneous SoC architecture. For hardware engineers, it offers automated solutions to integrate their accelerator designs into the complete SoC. If we go to the official website, we can see ESP (Embedded Scalable Platform) actually supports both 32-bit Leon3 (Sparc) and 64-bit Ariane (RISC-V) cores, and various hardware accelerators from the platform or third parties. Highlights: […]

Lattice Introduces CrossLink-NX FPGA for Edge AI & Embedded Vision

Lattice CrossLink-NX FPGA Lattice Semiconductor has announced the first product associated with its Nexus Platform, the CrossLink-NX FPGA designed for embedded vision and Edge AI applications. There are two offerings at this time, the CrossLink-NX FPGA 17, and the CrossLink-NX FPGA 40. Recent Announcements The Nexus Platform was introduced at the beginning of December 2019, and now CrossLink-NX has been developed and is being manufactured. The first announcements of Lattice Nexus Platform and The CrossLink-NX Product Family came as the company’s moved to capture the embedded vision systems market. The Standout Features The low-power consumption, low soft error immunity, and 10Gbps MIPI are highlights of the CrossLink-NX FPGA. Other features include Instant On, with IO configured in 3 ms, and a total of 8 ms for the device. The Cross-Platform FPGAs The trends in technology are leading to devices that can cross function in a number of different tech environments. […]

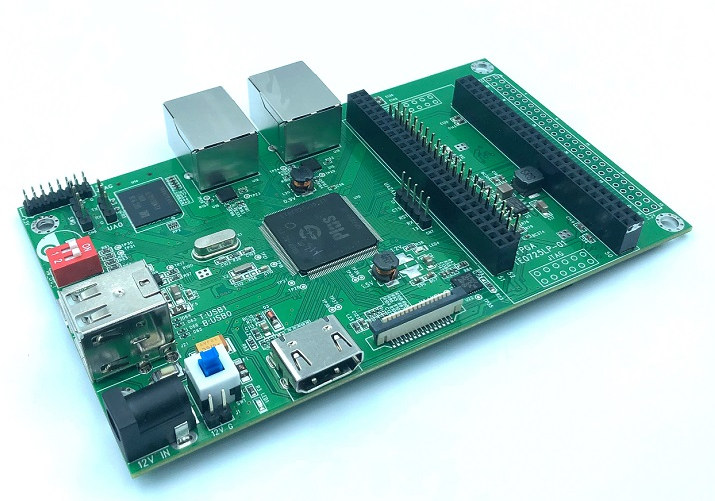

Banana Pi BPI-F2S Industrial SBC Launched for $58 with Linux 4.19 based Debian or Fedora OS

Last month we covered Banana Pi BPI-F2S single board computer (SBC) for industrial, IoT, and smart audio application that was powered by the intriguing SunPlus SP7021 “Plus1” processor featuring four Cortex-A7 cores, one ARM9 ARM9 real-time core, and one 8051 I/O controller core, as well as up to 512MB built-in DDR3 RAM. At the time, the board was not available, and we had limited information about software support, except the company would provide a Yocto-based Linux distribution. The good news is that you can now buy Banana Pi BPI-F2S industrial SBC on Aliexpress for $58 and Taobao for 390 RMB, and the company released source code and OS images for the board. Here’s a reminder of Banana Pi BPI-F2S specifications: SoC – Sunplus SP7021 “Plus1” with a quad-core Cortex-A7 processor @ 1.0 GHz, one Arm A926 microprocessor, an 8051 core to handle I/Os, and 128MB or 512MB DDR3 DRAM. Storage […]

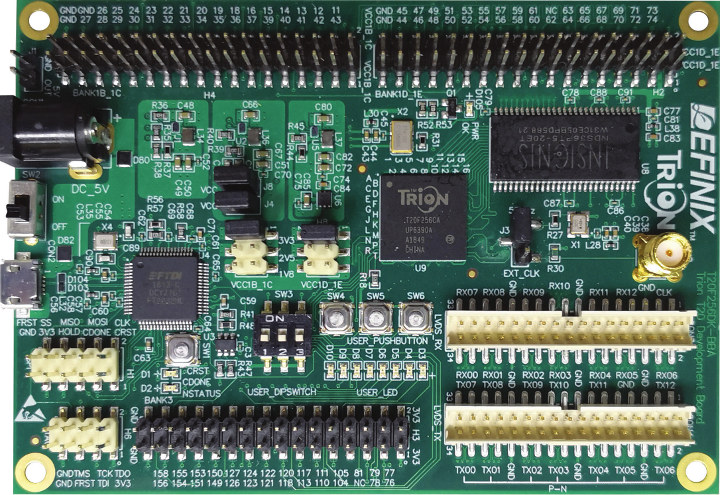

Trion T20 BGA256 FPGA Development Kit Supports “PulseRain Reindeer” RISC-V RV32IM soft CPU

A few months ago I wrote about FireAnt low-cost FPGA development board powered by Efinix Trion T8 FPGA, and it was the first time I personally heard about the company. Trion FPGA family range from the T4 with 3,888 logic elements up to the Trion T200 with 192,000 LE’s. A board more powerful than FireAnt, but not quite high-end, recently showed up on Digikey with Trion T20 BGA256 development kit going for $150. Trion T20 BGA256 Development Kit specifications: FPGA – Efinix Trion T20 FPGA with 19,728 LE’s, 1,044 Kbit embedded RAM, 36 18×18 multipliers, 7 PPL’s, up to 220 GPIO’s; 256-ball FBGA (13×13 mm) System Memory – 256 Mbit SDR SDRAM Storage – NOR flash USB – 1x Micro-USB port for programming Debug / Configuration – SPI and JTAG headers to facilitate configuration Expansion 3x I/O headers to connect to external devices LVDS TX header, LVDS RX & clock […]

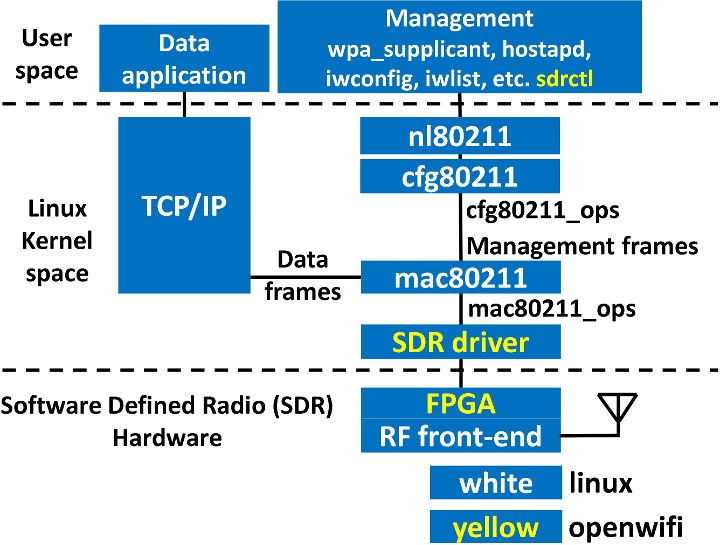

OpenWiFi Open-Source Linux-compatible WiFi Stack Runs on FPGA Hardware

WiFi is omnipresent on most connected hardware, and when it works it’s great, but when there are issues oftentimes they can not be solved because the firmware is a closed-source binary. I understand companies do that either to protect their IP and/or make sure end-users do not break FCC compliance. OpenWiFi project aims to deliver a completely open-source SDR (Software Defined Radio) WiFi implementation compatible with Linux and running on FPGA hardware. OpenWiFi currently supported features: 802.11a/g; 802.11n MCS 0~7; 20MHz Mode tested: Ad-hoc; Station; AP DCF (CSMA/CA) low MAC layer in FPGA Configurable channel access priority parameters: duration of RTS/CTS, CTS-to-self SIFS/DIFS/xIFS/slot-time/CW/etc Time slicing based on MAC address Easy to change bandwidth and frequency: 2MHz for 802.11ah in sub-GHz 10MHz for 802.11p/vehicle in 5.9GHz The developers tested OpenWiFi on Xilinx ZC706 FPGA evaluation kit coupled Analog Devices fmcomms2/fmcomms4 RF board to form an access point, and connected it to […]