Avnet Ultra96 was unveiled last year as one of the four 96Boards AI platforms designed to develop applications leveraging hardware to accelerated artificial intelligence workloads. The 96Boards CE compliant board comes with a Xilinx Zynq UltraScale+ MPSoC, 2GB RAM, a 16GB microSD card, WiFi and Bluetooth connectivity and more. The company has now launched an upgraded version with Ultra96-V2 featuring most of the same specifications but with a WiFi & Bluetooth module certified in 75 countries, industrial temperature range, and Infineon’s PMIC’s for additional power control and monitoring. Ultra96-V2 specifications: SoC – Xilinx Zynq UltraScale+ MPSoC ZU3EG A484 with four Cortex A53 cores, two Cortex-R5 core, Arm Mali-400MP2 GPU, and FPGA Fabric System Memory – 2 GB (512M x32) LPDDR4 Memory Storage – 16 GB MicroSD card + adapter pre-loaded with PetaLinux environment Video Output – Mini DisplayPort (MiniDP) Connectivity – Microchip ATWILC3000 certified 802.11 b/g/n WiFi 4 / Bluetooth […]

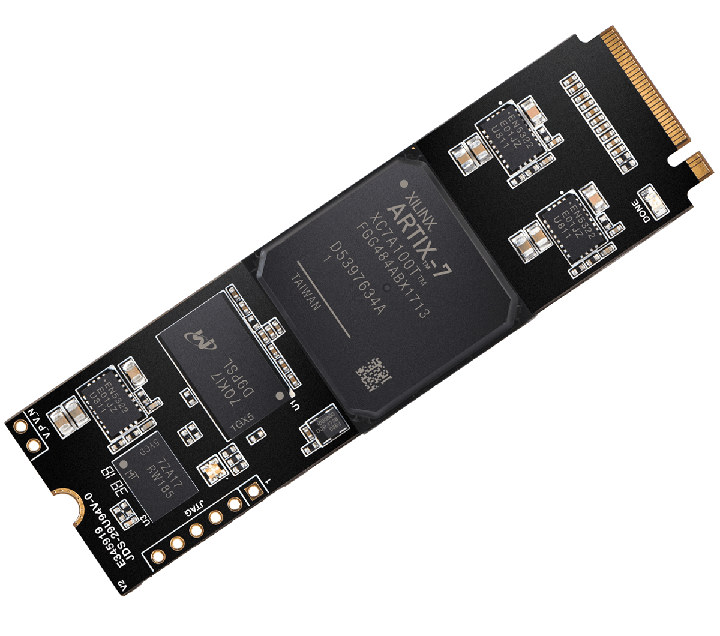

Aller Artix-7 FPGA Board with M.2 Interface Fits into a Laptop

A few days ago, we wrote about Nitefury M.2 card equipped with a Xilinx Artix-7 FPGA, and which you can connect to any laptop, board, a computer with a spare M.2 socket. It turns out Numato Lab has done something similar with the Aller board, specifically designed for development and integration of FPGA based accelerated features into other larger designs, and provided in a standard 2280 M.2 form factor M-key slot. Aller FPGA M.2 card key features & specifications: FPGA- Xilinx Artix-7 FPGA (XC7A100T-1FGG484C) with 101,440 Logic cells, ~126K Flip-flops, ~600KiB Block RAM, and 240 DSP slices System Memory – 2Gbit DDR3 (MT41J128M16JT-125:KTR) Storage – On-board 1Gb QSPI flash memory for FPGA configuration Host Interface – 4 lane PCIe Gen1 (2.5GT/s) via M.2 Connector Interface, M-Key Debugging – JTAG header for programming and debugging Security – 1x Trusted Platform Module (AT97SC3205) Misc – 100 MHZ CMOS oscillator, 1x RGB LED […]

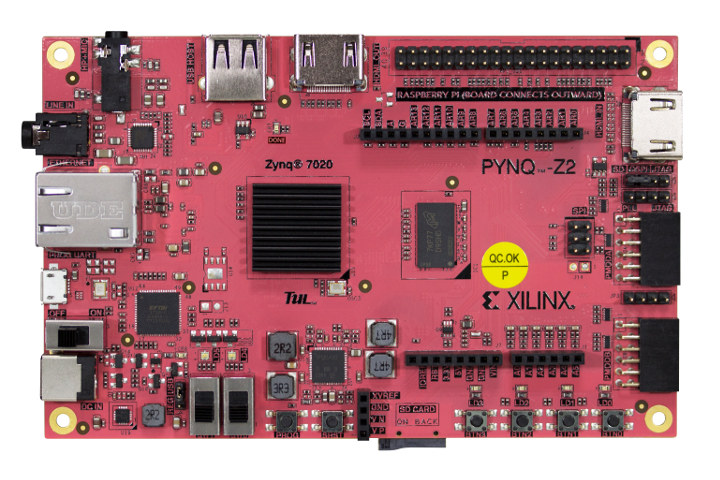

PYNQ-Z2 Python FPGA Board Adds Raspberry Pi Header, 24-Bit Audio Codec

PYNQ-Z1 is a board by Digilent powered by Xilinx Zynq-7020 Arm Cortex-A9 + FPGA SoC that’s designed specifically for PYNQ, an open-source project that aims to ease the design of embedded systems with Xilinx Zynq Systems on Chips (SoCs) by leveraging the Python language and libraries. PYNQ-Z2 is very similar to PYNQ-Z1, but it’s made by Taiwanese company TUL, and the board is slightly longer to allow for an extra 40-pin Raspberry Pi compatible header, and Analog Devices ADAU1761 24-bit audio codec. PYNQ-Z2 board specifications: SoC – Xilinx Zynq-7020 (XC7Z020-1CLG400C) dual core Arm Cortex-A9 processor @ 650 MHz with FPGA with 13,300 logic slices, each with four 6-input LUTs and 8 flip-flops System Memory – 512MB DDR3 Storage – Micro SD card slot, 16MB QSPI Flash with factory programmed globally unique identifier (48-bit EUI-48/64 compatible). Video – HDMI In and HDMI Out Audio – Mic in, Line Out ADAU1761 codec […]

NiteFury Puts Xilinx Artix-7 FPGA into an M.2 Card (Crowdfunding)

NiteFury is an FPGA development board, but it works differently than most, as RHS Research LLC put a Xilinx Artix-7 FPGA into an M.2 Key M card that you can easily insert into a laptop or mini PC with a 80mm M.2 socket. The board also includes DDR3 memory, and exposes a few configurable I/Os. You can use NiteFury to experiment with Xilinx PCIe IP, but also as FPGA co-processor for example to handle encryption, and encoding/decoding data. NiteFury card specifications: FPGA – Xilinx Artix XC7A200T-2FBG484E delivering up to ~1000 GMAC/s, with 215,360 Logic cells, 33,650 Slices, 269,200 CLB flip-flops, and 740 DSP slices. System Memory – 8 Gbit DDR3 (512 MB x 16) Host Interface – PCIe 4x gen 2 (2 Gb/s) External I/Os Via I/O connectors – 12x I/O including 4x selectable analog or digital – JTAG ready Via PCIe connector – 1x 3.3 V digital I/O (LED), […]

TechNexion AXON and FLEX SoM Families Feature i.MX 8M Mini SoC, FPGA Fabric

Taiwan based Technexion has introduced several new products at Embedded World 2019 including two new SoM families: AXON and FLEX. AXON is a product family of small form factor (58 x 37 mm) modules designed for specialized embedded applications requiring extra I/O flexibility, while FLEX series is a low-cost family making use of the standard LPDDR4 SO-DIMM connector. Specifically, the company launched new AXON and FLEX modules powered by NXP i.MX 8M Mini processor with AXON-IMX8M-MINI featuring AXON Fabric programmable logic, a specialized IC that provides additional functions including nearly infinite pinmuxing, and FLEX-IMX8M-MINI that offers HD multimedia streaming and integrated 3D graphics for cost sensitive applications. AXON-IMX8M-MINI SoM AXON-IMX8M-MINI SoM specifications: SoC – NXP i.MX 8M Mini Solo, Dual or Quad Arm Cortex-A53+M4 processor FPGA – “Axon Fabric” making use of a Lattice MachXO3LF FPGA with 2100 LUTs (LookUp Tables) System Memory – Up to 4GB LPDDR4 RAM Storage […]

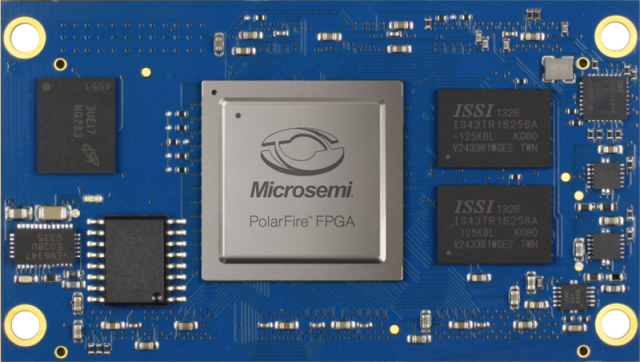

ARIES M100PF PolarFire FPGA System-on-Module Targets Industrial Applications, RISC-V Development

MicroSemi unveiled PolarFire RISC-V FPGA SoC at the end of last year, bringing an alternative to Xilinx Zynq (Arm Cortex-A9 + FPGA) and UltraScale+ (Cortex A53 + FPGA) SoCs. The system-on-chip is expected to be mass produced later in 2019, so development is done on HiFive Unleashed RISC-V board and its FPGA expansion board. In the meantime, MicroSemi PolarFire FPGAs (without RISC-V hard core) are available now, and ARIES Embedded planning to showcase what they claim is the first PolarFire FPGA system-on-module at Embedded World 2019 with their M100PF SoM targeting industrial applications. ARIES Embedded M100PF key features and specifications: A choice of 3 PolarFire FPGAs MPF100T – 109KLE, 336 Math Blocks (18x18MACC) MPF200T – 192KLE, 588 Math Blocks (18x18MACC) MPF300T – 300KLE, 924 Math Blocks (18x18MACC) System Memory – 512 MiB / 1 GiB / 2 GiB DDR3 RAM Storage – 256 MiB configuration device, 4 GiB eMMC flash […]

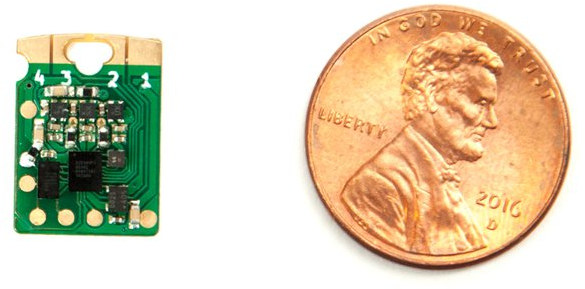

Fomu FPGA board fits inside a USB port, Supports Python, RISC-V Softcore

Sutajio Ko-usagi launched Tomu, a tiny open source hardware USB board that fits inside a USB port at the very beginning of this year. The company is back with a similarly shaped board, but instead of featuring a Silicon Labs EFM32 Arm Cortex-M0+ microcontroller, Fomu is equipped with a Lattice ICE40 UltraPlus FPGA. Fomu specifications: FPGA – Lattice ICE40UP5K FPGA with 5280 logic cells System Memory – 128 kB RAM for a soft CPU Storage – 1 or 2 MB SPI flash Clock – 48 MHz crystal oscillator USB – 1x USB 2.0 FS (12 Mbps) port Misc – 4x buttons, 1x RGB LED The default Fomu firmware exposes a USB bootloader running a RISC-V softcore, and the platform is powerful enough to run a port of Python. It’s also possible to experiment with LM32 and OpenRISC softcores on the platform. Using the board is pretty straightforward as just you […]

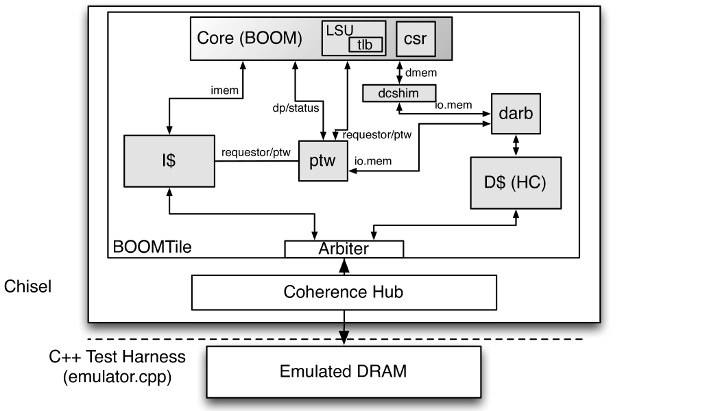

BOOM Open Source RISC-V Core Runs on Amazon EC2 F1 Instances

The Berkeley Out-of-Order Machine (BOOM) is an open source RV64G RISC-V core written in the Chisel hardware construction language, and mainly ASIC optimized. However, it is also usable on FPGAs, and developers support the FireSim flow to run BOOM at over 90 MHz on Xilinx Ultrascale+ FPGAs found in Amazon EC2 F1 instances. The BOOM core was created at the University of California, Berkeley in the Berkeley Architecture Research group, in order to create a high performance, synthesizable, and parameterizable core for architecture research. Key features of BOOM core: ISA – RISC-V (RV64G) Synthesizable FPGA support Parameterized Floating Point (IEEE 754-2008) Atomic Memory Op Support Caches & Virtual Memory Boots Linux Privileged Arch v1.11 External Debug BOOM is said to be inspired by the MIPS R10k and the Alpha 21264 out–of–order processors, based on a unified physical register file design (aka as “explicit register renaming”). The source code for the […]