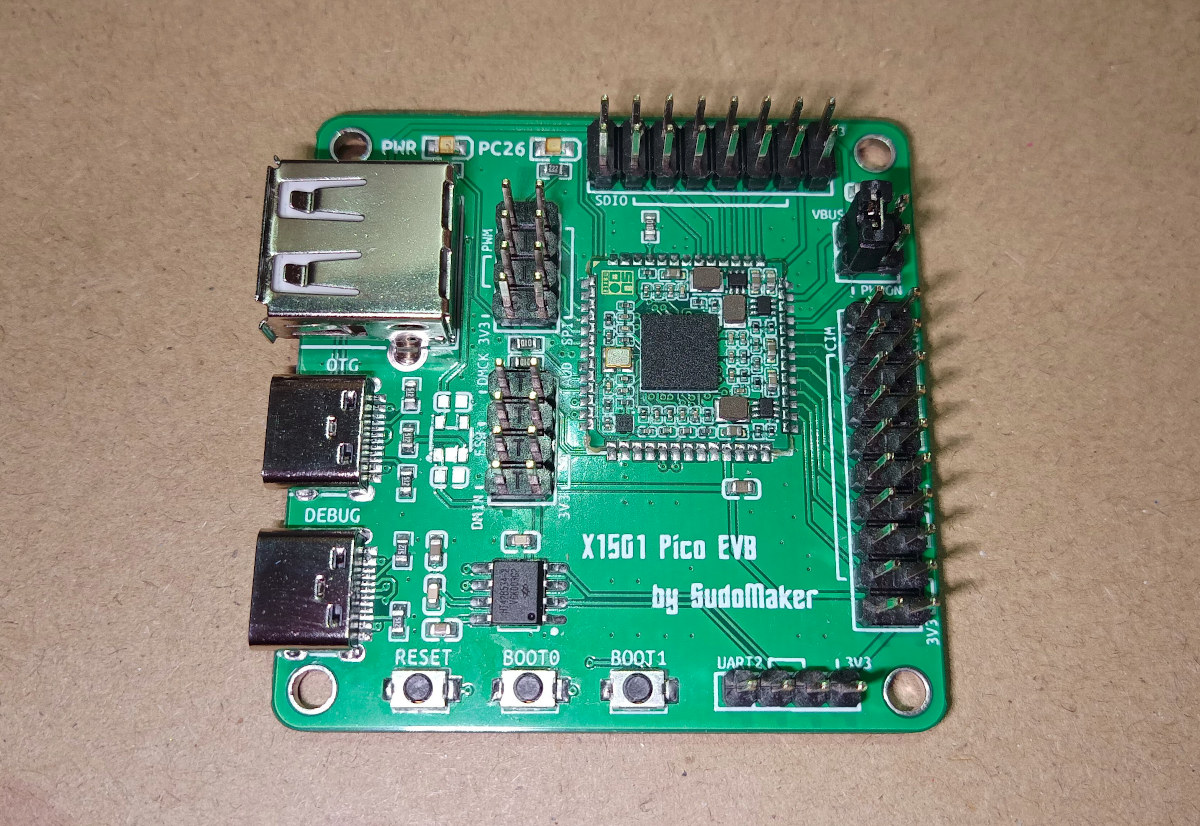

We’ve just written about the Notkia phone repurposing Nokia 168x phones with a new PCB featuring an Ingenic X1000E MIPS processor running mainline Linux, but it turns out the developer (Reimu NotMoe, CTO of SudoMaker) has also designed the X1501 Pico SoM, a tiny 16×16 system-on-module equipped with Ingenic X1501 MIPS system-in-package (SiP). The module can be that small because the single-core 1GHz Ingenic 1501 SiP embeds 8MB LPDDR, as well as apparently a 16Mbit NOR flash that stores stripped-down versions of U-boot and the Linux kernel, plus a minimal, busybox-based rootfs. X1501 Pico system-on-module specifications: SoC – Ingenic X1501 MIPS32r2 processor @ 1GHz, a MIPSr2 real-time core @ 300 MHz (not shown in datasheet), 8MB LPDDR and 16KB tightly coupled SRAM, 16Mbit NOR flash Castellated holes with USB 2.0 OTG, I2C, SPI, SDIO and DVP, analog mono audio output & digital microphone input EFUSE based Secure Boot Power Management […]

Ingenic T40 4K Video & AI Vision Processor mixes MIPS & RISC-V cores with AI accelerator

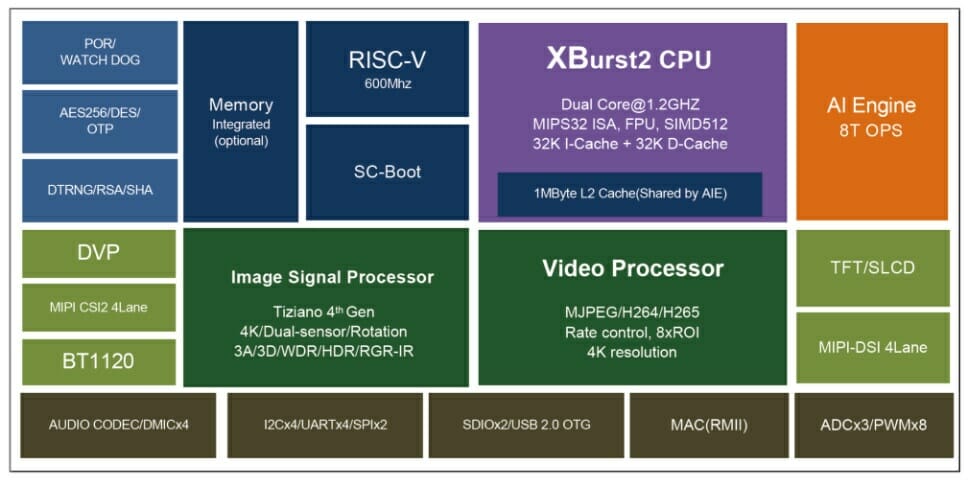

Ingenic T31 MIPS & RISC-V AI video processor was introduced last year with the MIPS core including SIMD128 Vector instructions for deep learning. The Chinese company has now introduced the new Ingenic T40 processor still with MIPS and RISC-V cores, but also a dedicated 8 TOPS AI engine/CNN accelerator. The new processor is especially suited to smart AI vision application thanks to support for 4K cameras, and 4K MJPEG/H.264/H.265 hardware video encoding, complemented by the 8 TOPS AI engine for computer vision workloads such as people detection, face recognition, object detection, and so on. Ingenic T40 key features and specifications: CPU – Dual-core MIPS XBurst2 @ 1.2 GHz with 256KB L2 Cache, SIMD512 instruction set MCU – 600MHz RISC-V coprocessor AI Engine – 8 TOPS neural network accelerator with 1MB memory pool, support for int16/int8/int4/int2 convolution width Memory – DDR2/DDR3/DDR3L up to 2GB Storage – SPI NOR flash, SPI NAND flash, […]

Ingenic T31 AI Video Processor Combines MIPS & RISC-V Cores

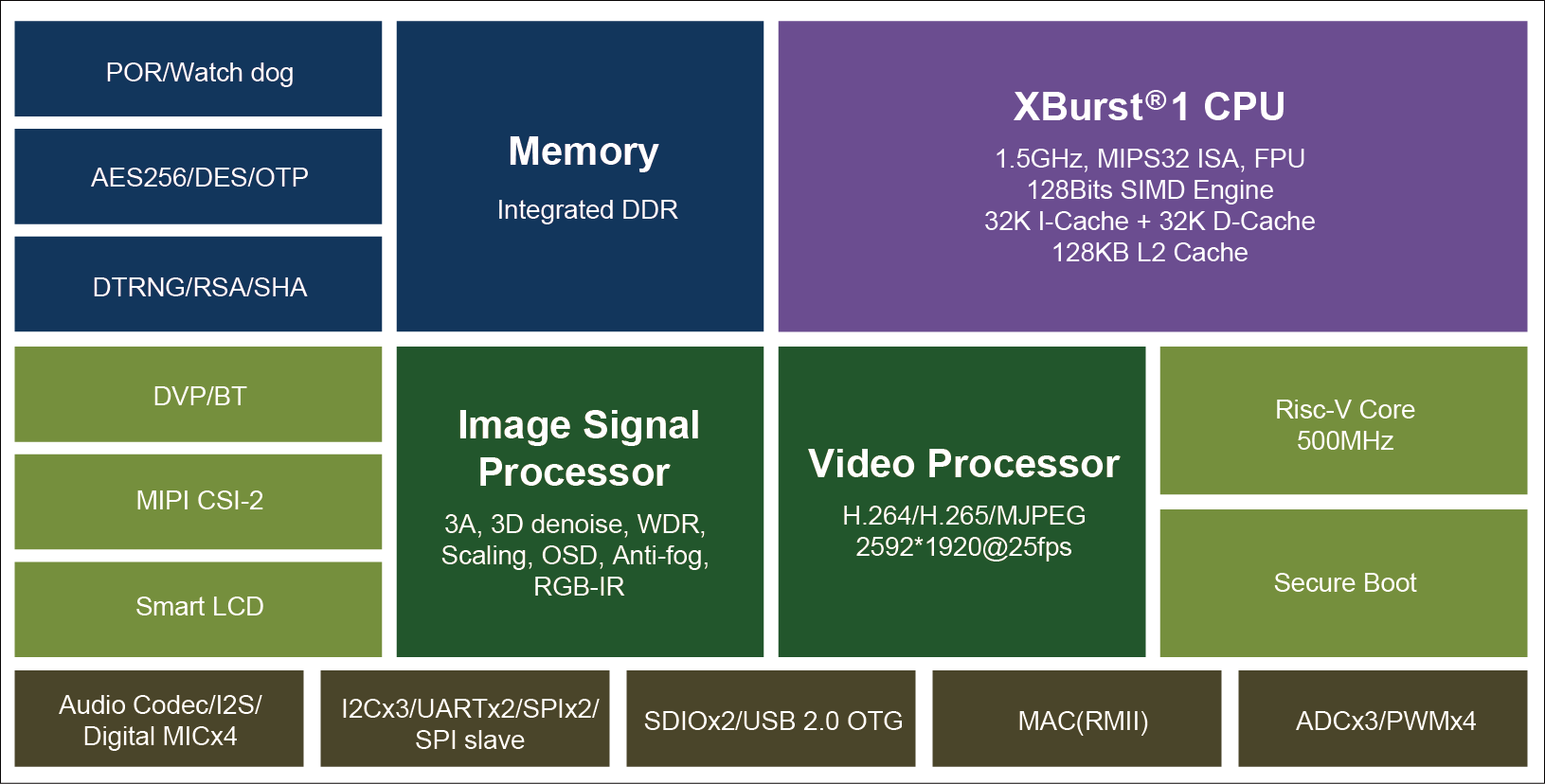

Last week we asked “is MIPS dead?” question following the news that Wave Computing had filed for bankruptcy, two MIPS Linux maintainers had left, and China-based CIP United now obtained the exclusive MIPS license rights for mainland China, Hong Kong, and Macau. Ingenic is one of those Chinese companies that have offered MIPS-based processors for several years, but one commenter noted that Ingenic joined the RISC-V foundation, and as a result, we could speculate the company might soon launch RISC-V processors, potentially replacing their MIPS offerings. But Ingenic T31 video processor just features both with a traditional Xburst MIPS Core combines with a RISC-V “Lite” core Ingenic T31 specifications: Processors XBurst 1 32-bit MIPS core clocked at 1.5GHz with Vector Deep Learning accelerator based on SIMD128, 64KB + 128KB L1/L2 Cache RISC-V independent lite core System Memory – Built-in 512Mbit (64MB) or 1Gbit (128MB) DDR2 Storage – Quad SPI flash, […]

Ingenic X1830 IoT Processor Features a 32-bit MIPS Core, 128MB DDR2 RAM

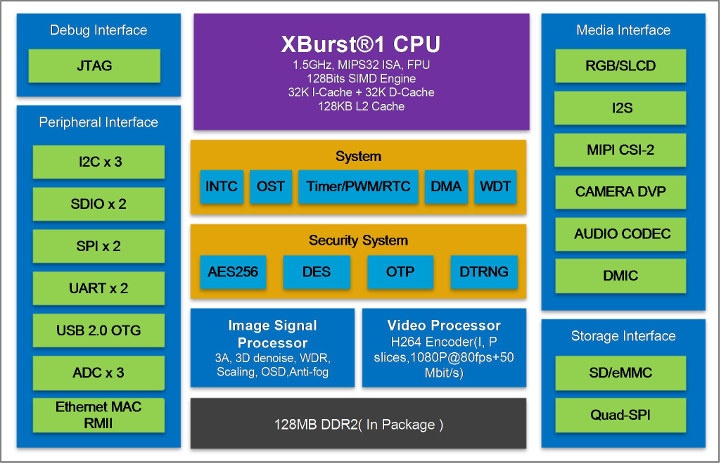

Ingenic is a silicon vendor based in Beijing, China and known for its MIPS Xburst processors such as JZ4780 dual-core SoC or T10 video processor. It’s been a while (a few years) since we last covered new processors from the company, but it appears the company launched another MIPS SoC for IoT applications last year. Meet Ingenic X1830 processor. X1830 specifications: CPU – MIPS32 XBurst-1 core @ up to 1.5 GHz with SIMD engine, 32KB instruction cache, 32KB data cache, 128KB unified L2 cache Memory – 128MB DDR2 in package Storage I/F – 2x SD/eMMC controllers, and Quad SPI (QSPI) VPU H264 Encoder up to 1080p80 or 1560×1600 resolution JPEG compressing/decompressing up to 70Mega-pixels per second ISP 12-bit RAW or up to 24-bit RGB Max input resolution 2688×2048 @20fps, 1080p @60fps,720p @120fps 2-D and 3-D noise reduction filter, advanced demosaic, color processing, lens shading, defog, glare, static/dynamic defect pixel… Image […]

Ingenic T10 is a MIPS Based Video Processor for 720p Cameras

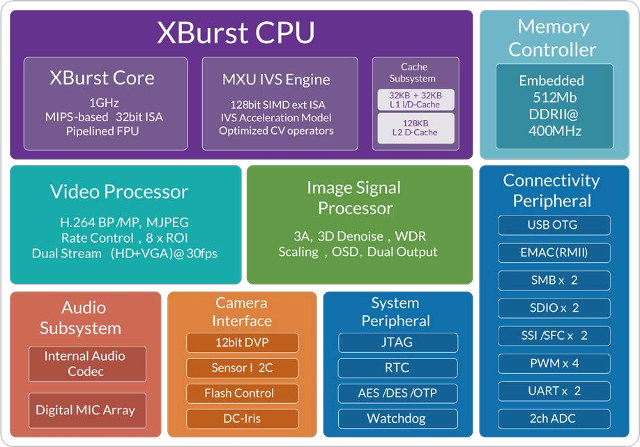

Ingenic has been designing MIPS based SoCs using their Xburst processor engine for several years, which are found in tablets, development boards, and wearables. The company has now launched T10 smart video processor based on the same MIPS32 processor but mobile camera, security survey, video talking, video analysis and so on with image resolution up to 1280×960 (datasheet says 1280×1024), and videos up to 720p30 or VGA @ 30fps. Ingenic T10 specifications: CPU – XBurst single core MIPS32 processor up to 1GHz with FPU, 32KB L1 I-cache, 32KB L1 D-cache, and 128KB L2 unified cache. Memory – Embedded DDRII@400Mhz up to 512Mbit Encoder engine -H.264 baseline, main profile; MJPEG/JPEG Baseline Encode Performance Max resolution 1280×960 Up to H.264 960p@40fps encode H.264 multiple streams 720p@30fps + VGA@30fps + JPEG@15fps 960p@30fps + VGA@30fps + JPEG@15fps ABR/VBR/CBR/CQP 8 ROIs (Regions of Interest) 5-layer OSD with hardware ISP AE, AWB (automatic white balance), AF […]

Ingenic X1000 MIPS Processor and X1000 Phoenix Board Target IoT and Embedded Applications

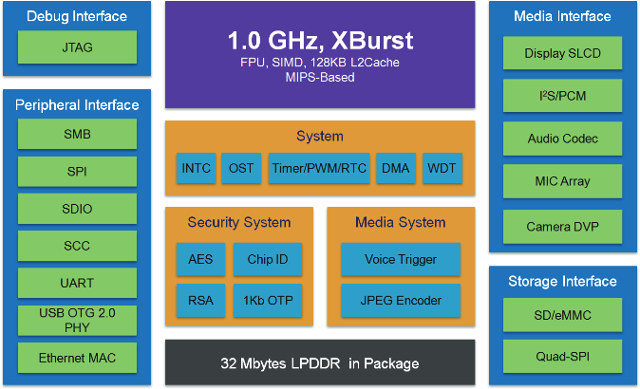

Ingenic is a Chinese SoC vendor that makes processors featuring their X-Burst cores based on MIPS architecture. Their JZ47 series can be found in tablets and development boards such a MIPS Creator CI20, while their M series, including Ingenic M200, are dedicated to wearables & IoT applications. The company has now launched X series starting with X1000 processor which include an audio codec, a Voice Trigger Engine (VTE) and 32MB RAM in package. Ingenic X1000 features: CPU Core – Ingenic MIPS XBurst 32-bit core up to 1.0 GHz, Double precision hardware float point unit, L1 cache 16KB/16KB, and L2 cache 128KB Security Core – On-chip security ROM and RAM, hardware AES and RSA, supports security boot and user customization Memory 32MB LPDDR in package Support 16-bit DDR2, DDR3 and LPDDR up to 512MB Support Quad-SPI NOR/NAND, eMMC, SDHC Display – 8-bit, 9-bit, 16-bit parallel interface SLCD up to 640×480@60Hz, 24 […]

Linux 4.2 Release – Main Changes, ARM and MIPS Architectures

Linus Torvalds released Linux Kernel 4.2 last Sunday: So judging by how little happened this week, it wouldn’t have been a mistake to release 4.2 last week after all, but hey, there’s certainly a few fixes here, and it’s not like delaying 4.2 for a week should have caused any problems either. So here it is, and the merge window for 4.3 is now open. I already have a few pending early pull requests, but as usual I’ll start processing them tomorrow and give the release some time to actually sit. The shortlog from rc8 is tiny, and appended. The patch is pretty tiny too. Go get it, Linus Some notable changes made to Linux 4.2 include: File systems New features for F2FS including per file encryption CIFS support SMB 3.1.1 (experimental) Cryptography – Jitter Entropy Random Number Generator, Chacha20 stream cipher and Poly1305 authentication (RFC7539),New RSA implementation. See lwn.net […]

Ingenic Halley is a $20 Linux based IoT Board with Wi-Fi and Bluetooth 4.1 Connectivity

Ingenic introduced Newton2 platform for wearables a few months ago, and the kit with an AMOLED display, camera board and other accessories should go on sale in March for $80. In the meantime, the company has also been working on a lower cost internet of things (IoT) module and development kit powered by Ingenic M150 with Wi-Fi and Bluetooth 4.1 targeting smart appliances, Wi-Fi speakers, smart toys, industrial control applications, and other smart devices. Halley IoT module specifications: SoC – Ingenic M150 XBurst (MIPS) single-core processor up to 1.0GHz with 128MB LPDDR on-chip, 2D graphics GPU, VPU supporintg 720p30 H.264 video decoding. Storage – 8MP SPI NOR flash (GIGA GD25LQ64) Connectivity – Wi-Fi 802.11 b/g/n and Bluetooth 4.1 via Broadcom 43438 chip. Expansion headers (2mm pitch) 8-bit parallel LCD interface, Audio – MIC, Line-In and headphone, 2x I2S, SD card (MMC interface) USB device 2.0, and USB host 1.1 3x […]