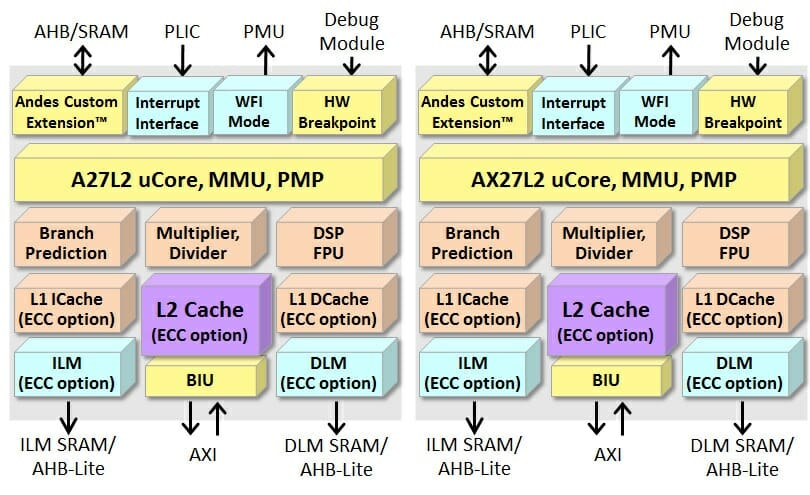

Last year, Andes introduced the AndesCore 27-Series of Linux capable RISC-V cores with a vector processing unit for AI acceleration with specifically the 32-bit A27 and the 64-bit AX27 cores. The company also introduced the higher-end AndesCore 45-series (A45 and AX45) at about the same time, but we somehow missed the announcement. Andes has now added more Linux capable RISC-V AndesCore to the aforementioned families with the high-performance superscalar A45MP and AX45MP multi-core processors, and A27L2 and AX27L2 processors with an L2 cache controller. Andes A27L2 and AX27L2 cores Based on the highlights, the new cores look identical to the A27 and AX27L2 cores announced last year expect the additional L2 cache that comes with optional ECC. AndesCores A27L2 and AX27L2 key features and specifications: AX27L2 – 64-bit, 5-stage pipeline CPU architecture (RV64GCPN), enabling software to utilize the memory spaces far beyond 4GB A27L2 – 32-bit, 5-stage pipeline CPU architecture […]

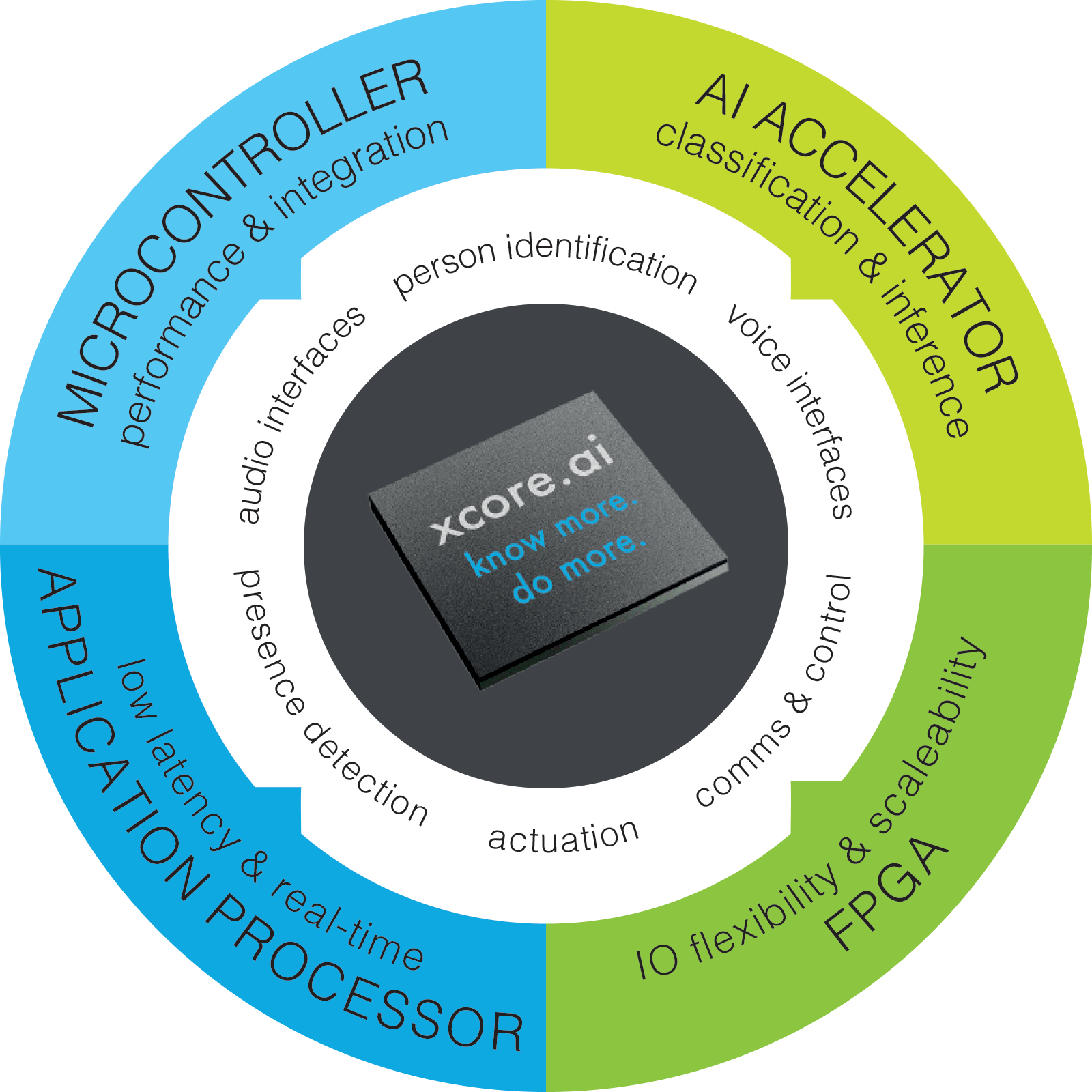

XMOS launches Xcore.AI, a scalable AI processor for the Edge

XMOS, known for its high-performance voice interfaces, is joining the AIoT bandwagon with the announcement of the Xcore.ai, a flexible and economical processor delivering high-performance AI, DSP, control, and I/O’s in a single device. IoT and AI have been one of the most trending topics and fields in the last decade. Both areas have seen large innovations in between them. Deep neural networks have become better, IoT deployment cost has also been greatly reduced, and most importantly, they both have a significant impact on multiple industries. An interesting trend recently is the emergence of applications merging AI and IoT together to form so-called AIoT applications. IoT will be the digital nervous system, while AI will become the brain that makes all the critical decisions which will control the whole system. AIoT has led to the development and deployment of what we call AI processors or AI modules that can be […]

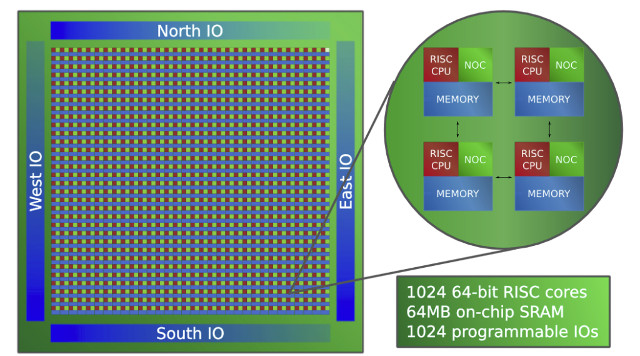

Parallella 1024-core Epiphany-V RISC Processor Coming Soon

Parallella project’s goal is to ” democratize access to parallel computing by offering affordable open source hardware platforms and development tools”, and they’ve already done that with their very first $99 “Supercomputer” board combining a Xilinz Zynq FPGA + ARM SoC to the company’s Epiphany-III 16-core coprocessor. But the company has made progress after their 64-core Epiphany-IV, by taping out Epiphany-V processor with 1024-core last October. Epiphany-V main features and specifications: 1024 64-bit RISC processors 64-bit memory architecture 64-bit and 32-bit IEEE floating point support 64 MB of distributed on-chip SRAM 1024 programmable I/O signals 3x 136-bit wide 2D mesh NOCs (Network-on-Chips) 2052 separate power domains Support for up to one billion shared memory processors Support for up to one petabyte of shared memory (That’s 1,000,000 gigabytes) Binary compatibility with Epiphany III/IV chips Custom ISA extensions for deep learning, communication, and cryptography TSMC 16FF process 4.56 Billion transistors, 117mm2 silicon area With […]

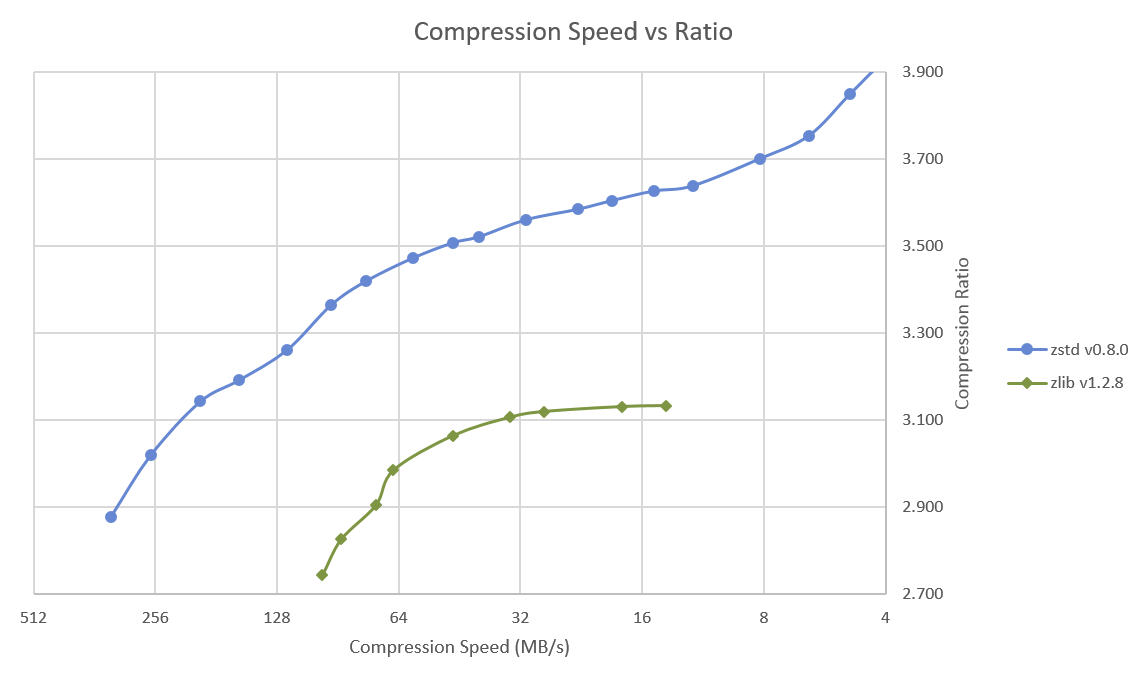

Facebook Zstandard “zstd” & “pzstd” Data Compression Tools Deliver High Performance & Efficiency

Ubuntu 16.04 and – I assume – other recent operating systems are still using single-thread version of file & data compression utilities such as bzip2 or gzip by default, but I’ve recently learned that compatible multi-threaded compression tools such as lbzip2, pigz or pixz have been around for a while, and you can replace the default tools by them for much faster compression and decompression on multi-core systems. This post led to further discussion about Facebook’s Zstandard 1.0 promising both smaller and faster data compression speed. The implementation is open source, released under a BSD license, and offers both zstd single threaded tool, and pzstd multi-threaded tool. So we all started to do own little tests and were impressed by the results. Some concerns were raised about patents, and development is still work-in-progess with a few bugs here and there including pzstd segfaulting on ARM. Zlib has 9 levels of […]

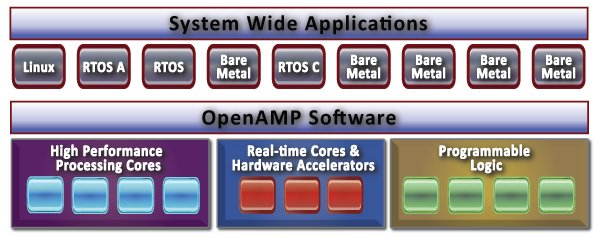

OpenAMP Open Source Framework Provides the Glue between Linux, RTOS, and Bare Metal Apps in Heterogeneous SoCs

SoCs becoming more complex, and go beyond homogeneous multicore systems by mixing different type of cores such as high performance cores, low power real-time cores, or even FPGA fabric. Examples include NXP i.MX6 SoloX with an ARM Cortex A9 core for Linux apps, and an ARM Cortex M4 core for real-time tasks, or Xilinx Zynq UltraScale+ MPSoC with Cortex A53 core for higher level apps, Cortex R5 cores for real-time processing, and Ultrascale FPGA logic. All these different cores are running their own Linux based OS, real-time operating system or bare metal application, and all this makes software development an even greater difficult tasks. In order to reduce the complexity, and address some of the issues, the Multicore Association has launched a new working group targeting the management, expansion, and standardization of OpenAMP (Open Asymmetric Multi Processing), an open source framework that allows operating systems to interact within a broad […]

XMOS xCORE-XA Octa-core ARM Cortex-M3 SoC and $14.99 StartKIT Board

XMOS is a fabless semiconductor company that specialized in multicore MCUs that delivers scalable, parallel multitasking compute, which are used in embedded applications for consumer, industrial and automotive markets. They’ve recently announced xCORE-XA (eXtended Architecture), their first MCU based on ARM technology with one ARM Cortex M3 core, and seven xCORE core, as well as a low cost development board called XMOS StartKIT featuring xCORE-A (Analog) with eight cores. XMOS xCORE-XA SoC xCore-XA is actually an octa-core MCU with the following key features: Eight 32bit processors – seven xCORE logical cores supporting DSP instructions, and an ARM Cortex-M3 processor (up to 500 MIPS in total) On-chip Memory – 192KB SRAM, and 512 or 1024KB SPI Flash depending on model. 38 I/O including I2C, SPI, ADC, DAC, op-amps, capacitive sensing comparators, and optional USB 2.0 interface. Hardware response ports – Eliminate the need for interrupts and provide up to 100x faster […]

ARM TechCon 2013 Schedule – ARM Servers, Internet of Things, Multicore, Hardware and Software Optimization and More

ARM Technology Conference (TechCon) 2013 will take place on October 29 – 31, 2013, in Santa Clara, and the detailed schedule for the event has just been made available. In the previous years, the conference was divided into Chip Designs day (1 day), and the other 2 days were reserved for Software & System Design, but this year it does not appear to be the case. Whether you’ll be able to attend the event or not, it’s worth having a look at what will be discussed there in order to have a better understanding of what will be the key ARM developments in the near future in terms of hardware and software. There will be around 90 sessions categorized into 15 tracks: Accelerating Hardware Development – This track explores the resources, tools, and techniques that designers can employ to quickly bring hardware to market. Topics include multicore design, ARM IP, […]

ARM TechCon 2012: Software & System Design Schedule

ARM Technology Conference (TechCon) 2012 will take place on October 30 – November 1, 2011, in Santa Clara, and UBM Electronics has already posted the detailed schedule for the event. The first day (October 30) will be Chip Designs day and the other 2 days will focus on Software & System Design. Even if, like me, you are not be able to go there, it’s still interesting to know what will be discussed at the conference, to have a better idea where ARM is going, and what new technologies and/or development techniques are (or will become) available. There will be around 70 sessions categorized in 15 tracks: Android / Open Source – Development tools, middleware for native application development, and optimized drivers for Android, Linux, FreeRTOS etc … Compute Platforms – Development and implementation of standards and specifications, from board/module design to consumer and server designs Developing / Debugging – […]