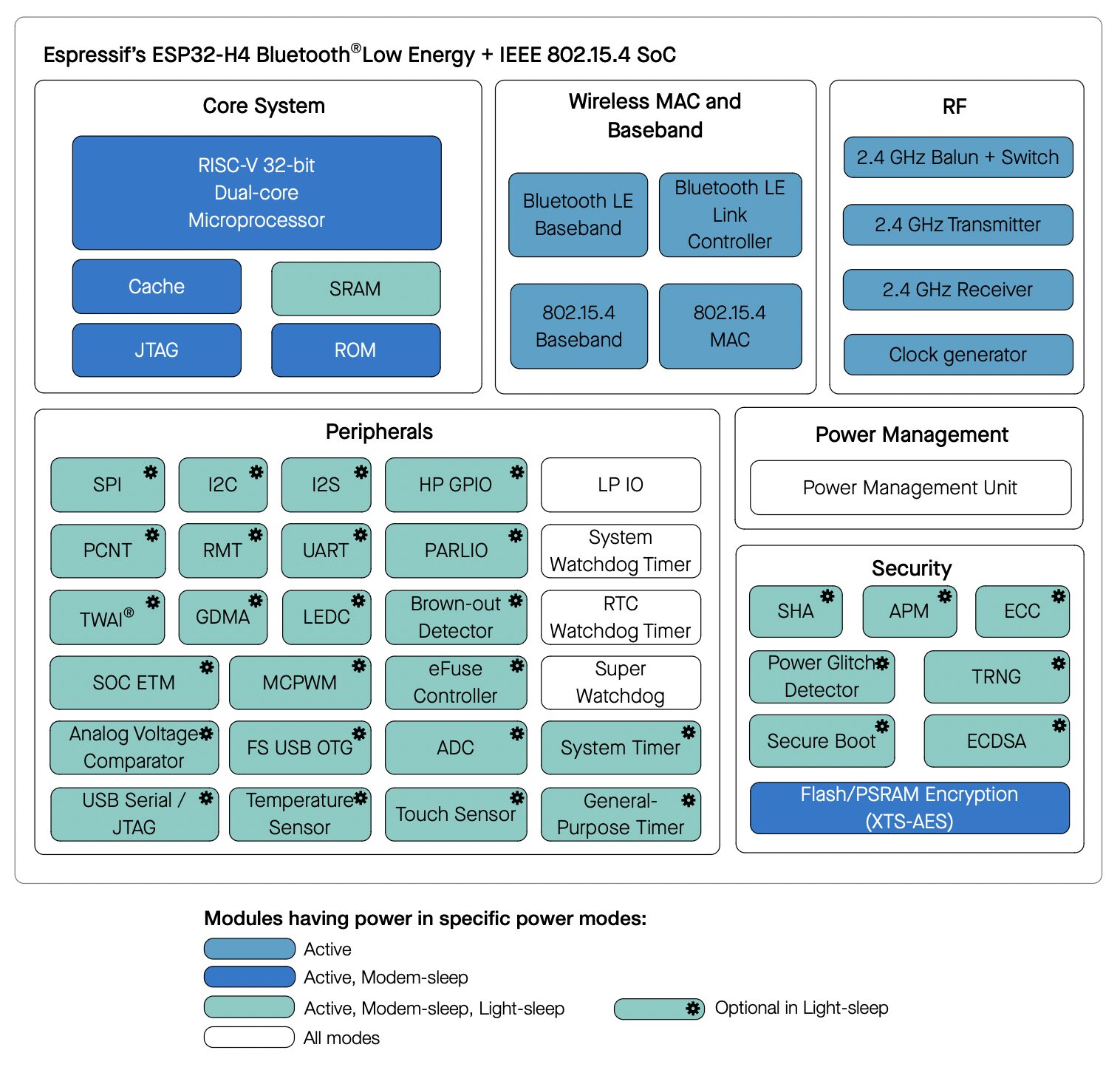

Espressif Systems has formally announced the ESP32-H4 low-power dual-core 32-bit RISC-V wireless microcontroller with support for 802.15.4 and Bluetooth 5.4 LE portfolio after having unveiled it at CES 2024. It’s the first Espressif chip to support Bluetooth 5.4 LE with previous models such as ESP32-H2 or ESP32-C6 only supporting Bluetooth 5.0/5.2. Besides BLE 5.4 support, the new ESP32-H4 dual-core RISC-V WiSoC is an evolution of the ESP32-H2 single-core chip with PSRAM support (up to 4MB built-in), additional GPIOs (36 vs 24), touch sensing GPIOs, and some extra security features such as a power glitch detector also found in the recently announced ESP32-C61. ESP32-H4 specifications: CPU – Dual-core 32-bit RISC-V core (at up to 96 MHz) RAM – 320KB KB SRAM, optional PSRAM up to 4MB Storage – 128KB ROM, External flash support Wireless connectivity IEEE 802.15.4 radio with Zigbee and Thread support, Matter protocol Bluetooth 5.4 (LE) radio designed in-house, […]

Imagination launches the APXM-6200 RISC-V “Catapult” CPU for cost-sensitive consumer and industrial applications

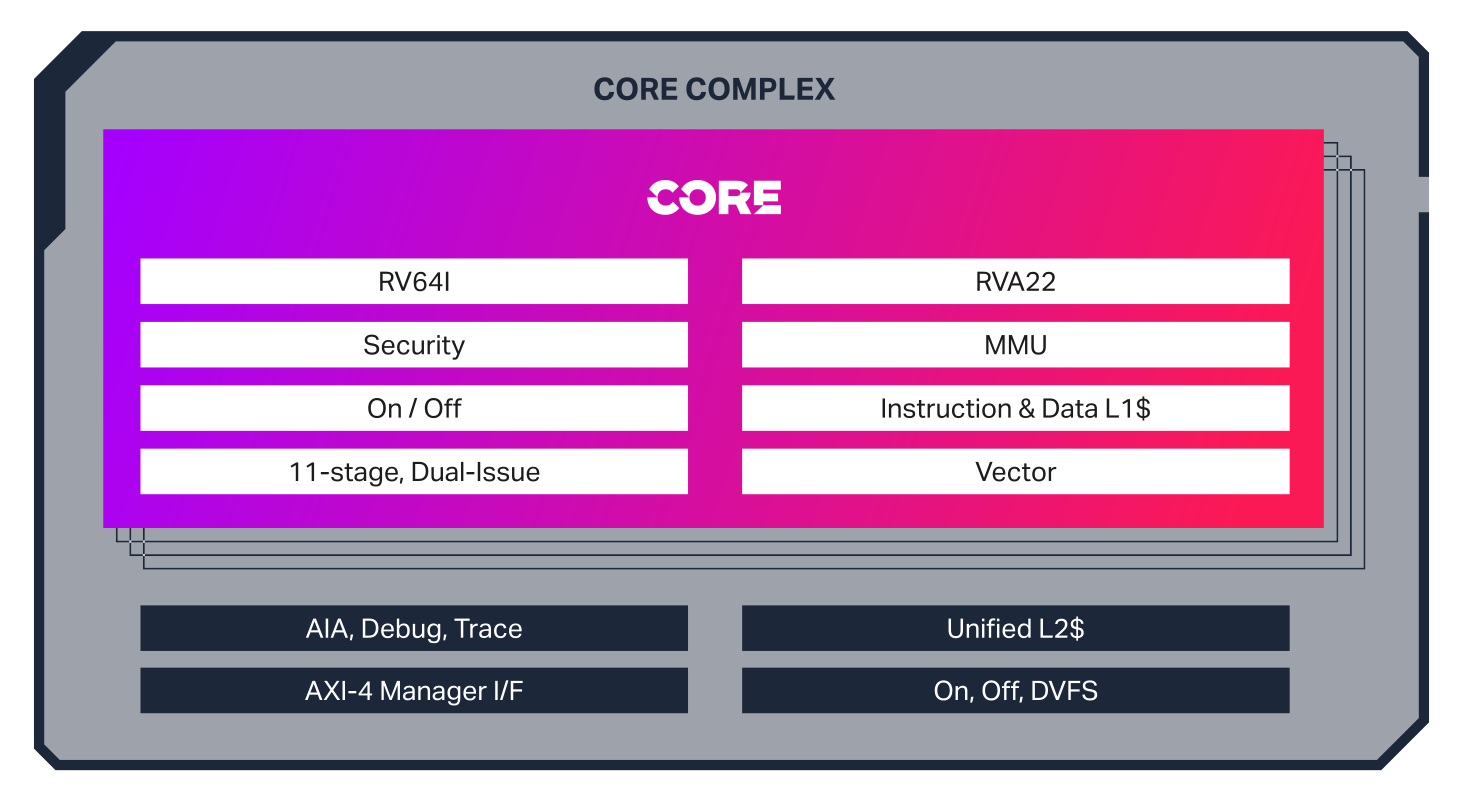

Imagination has expanded its Catapult product portfolio to include a new RISC-V core, the Imagination APXM-6200 CPU. The APXM-6200 is a 64-bit, in-order application processor with an 11-stage, dual-issue pipeline. There isn’t much information on the new Imagination RISC-V core on the product page but we know it offers “best-in-class” performance density, a minimal silicon footprint, and industry-standard security features. The CPU is targeted at intelligent consumer and industrial applications and delivers a 2.5x improvement in performance density and a 65% improvement in normalized performance over comparable Arm Cortex-A53 and other cores on the market. It’s also faster than the Cortex-A510 Armv9 core in SpecINT2k6. Imagination claims that combining the APXM-6200 CPU with their GPUs will ensure a 2x increase in bus utilization and a 2x reduction in memory traffic. It also comes with RISC-V vector extensions, and AI compute libraries and supports fast data coupling with AI accelerators for […]

u-blox ALMA-B1 and NORA-B2, Bluetooth 5.4 LE modules are based on Nordic nRF54H20 and nRF54L15 SoCs

Wireless communication solutions provider, u-blox has added two new modules to its Bluetooth LE portfolio with the ALMA-B1 and NORA-B2 modules built upon the latest low-power wireless nRF54 chips from Nordic Semiconductor. Both modules come in a portable, power-efficient layout and support Bluetooth 5.4 and 802.15.4 (Thread, Matter, Zigbee). The ALMA-B1 and NORA-B2 BLE modules are powered by the low-power nRF54H20 and nRF54L15 SoCs, respectively. This enables them to provide IoT devices with sufficient processing power for edge computing and machine learning without the need for external components. u-blox claims that the ALMA-B1 module provides “more than twice the processing power of previous Bluetooth LE modules” and can replace general-purpose microcontrollers in compact solutions. Also, the NORA-B2 reportedly “consumes up to 50% less current compared to previous generations of Bluetooth LE modules,” leading to longer battery life or smaller batteries in end products. Both modules are classified as open CPU […]

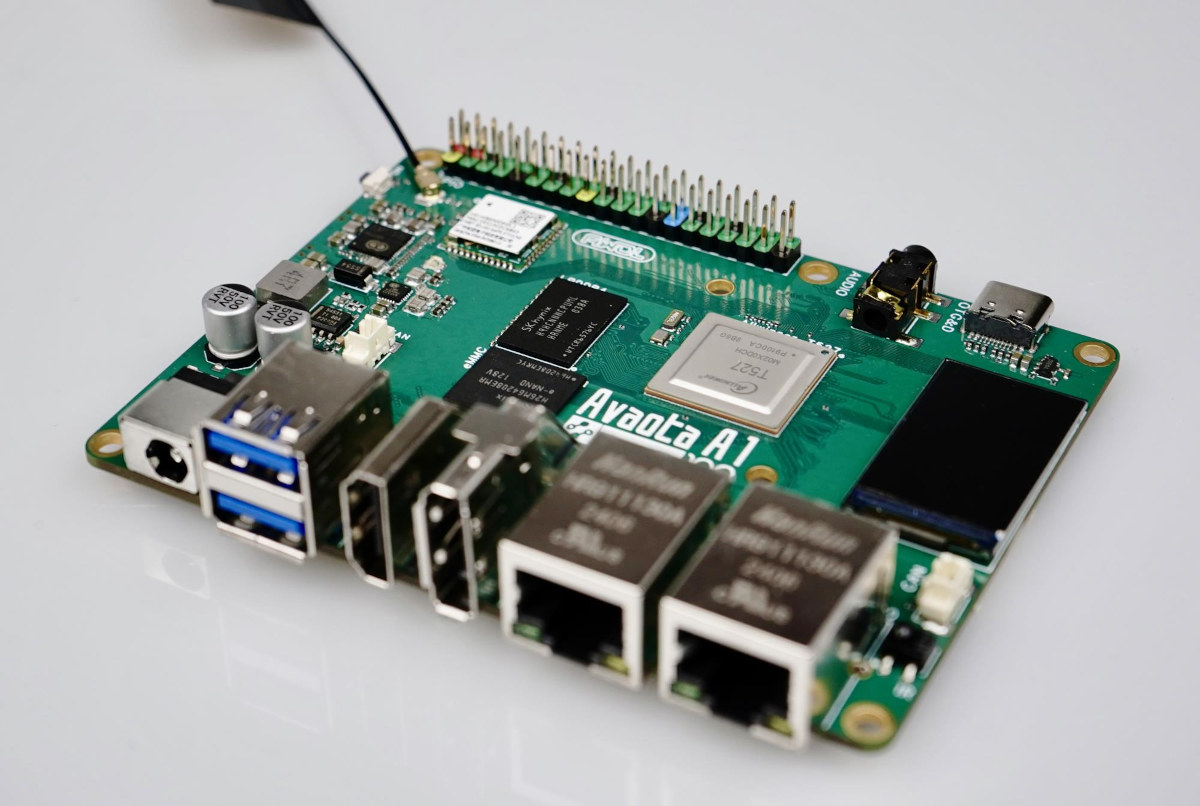

Avaota A1 open-source hardware SBC is powered by Allwinner T527 octa-core Cortex-A55 SoC

We’ve recently covered MYiR Tech MYD-LT527 industrial development board based on Allwinner T527 octa-core Cortex-A55 AI SoC and noted Orange Pi is working on one that should even get mainline Linux support. The Avaoto A1 offers another Allwinner T527 hardware option with an SBC design that’s fully open-source. The board is equipped with up to 4GB RAM, 128GB eMMC flash, HDMI and DisplayPort video outputs, two gigabit Ethernet ports, a WiFi 6 and Bluetooth 5.4 module, a few USB ports, a 3.5mm audio jack and the usual 40-pin GPIO header for expansion. Avaota A1 specifications: SoC – Allwinner T527 (or Allwinner A527 with Avaota A1C board, not sure what the differences are between the two) CPU Octa-core Arm Cortex-A55 processor with four cores @ 1.80 GHz and four cores @ 1.42GHz XuanTie E906 RISC-V core up to 200 MHz GPU – Arm Mali-G57 MC1 GPU with support for OpenGL ES […]

Orange Pi Developer Conference 2024, upcoming Orange Pi SBCs and products

Orange Pi held a Developer Conference on March 24, 2024, in Shenzhen, China, and while I could not make it, the company provided photos of the event where people discussed upcoming boards and products, as well as software support for the Orange Pi SBCs. So I’ll go through some of the photos to check out what was discussed and what’s coming. While Orange Pi is mostly known for its development boards the company has also been working on consumer products including the Orange Health Watch D Pro and the OrangePi Neo handheld console. The Orange Pi Watch D Pro is said to implement non-invasive blood glucose monitoring, blood pressure monitoring, one-click “micro-physical examination” and other functions to to help users monitor their health monitoring. The Watch D Pro uses a technique that emits a green light to measure glucose levels in the blood, and we’re told it’s accurate enough to […]

LoLRa project – Transmitting LoRa packets without radio using CH32V003, ESP8266, or ESP32-S2 MCU

The LoLRa project is a firmware-only LoRa transmission open-source project that works without a Semtech radio and instead relies on an I2S or SPI interface (so not exactly bit-banging) to transmit data with microcontrollers such as WCH CH32V003, or Espressif Systems ESP8266 and ESP32-S2 microcontrollers. LoRa is a proprietary protocol by Semtech, but people have been trying to reverse-engineer the LoRa PHY for years, and this culminated with a LoRa GNU Radio SDR implementation last year. But CNLohr found out you don’t even need a radio to send LoRa packets and you can instead use SPI or I2S interfaces from general-purpose microcontrollers to send packets that can be decoded by commercial off-the-shelf LoRa gateways and other chips. The current implementation is designed for the ITU Region 2 (aka The Americas) targeting the 902-928MHz frequency band, but the code could be changed for Region 1 (EU, Russia, Africa) to target 863-870MHz […]

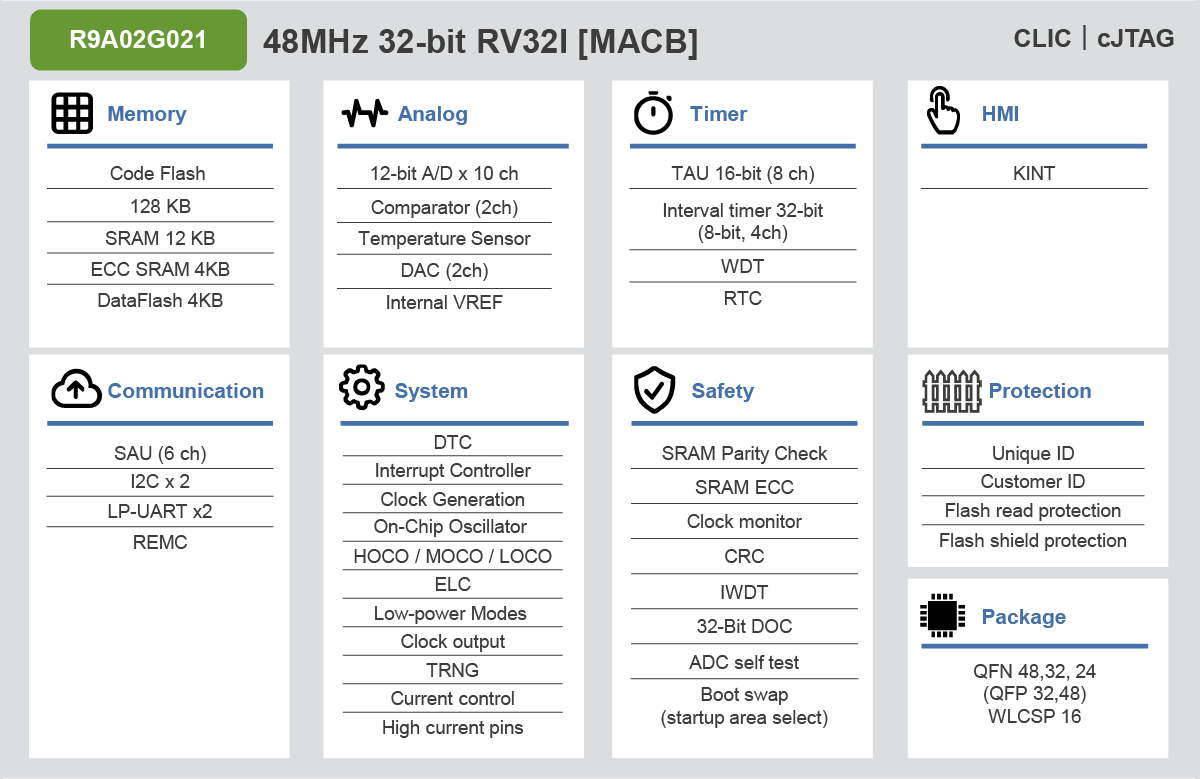

R9A02G021 is the first microcontroller with Renesas 32-bit RISC-V CPU core design

Renesas R9A02G021 is the first MCU group to use the company’s in-house designed 32-bit RISC-V CPU core with 3.27 CoreMark/MHz, RV32I base plus M/A/C/B extensions, and features such as a stack monitor register, a dynamic branch prediction unit, and a JTAG debug interface. Renesas has been making RISC-V chips at least since 2022 with the likes of RZ/Five 64-bit microprocessor and R9A06G150 32-bit voice control ASSP. All those were based on Andes RISC-V cores, but since the company has now designed its own 32-bit core, future Renesas 32-bit RISC-V microcontrollers are all likely to feature the in-house core, starting with the R9A02G021 general-purpose MCU group. Renesas R9A02G021 key features and specifications: RISC-V Core Renesas RISC-V instruction-set architecture (RV32I + MACB + Ziscr, Control and Status Register (CSR) instructions + RISC-V Zifencei Instruction-Fetch Fence) Maximum operating frequency – 48 MHz Debug and Trace – RISC-V External Debug Support cJTAG Debug Port […]

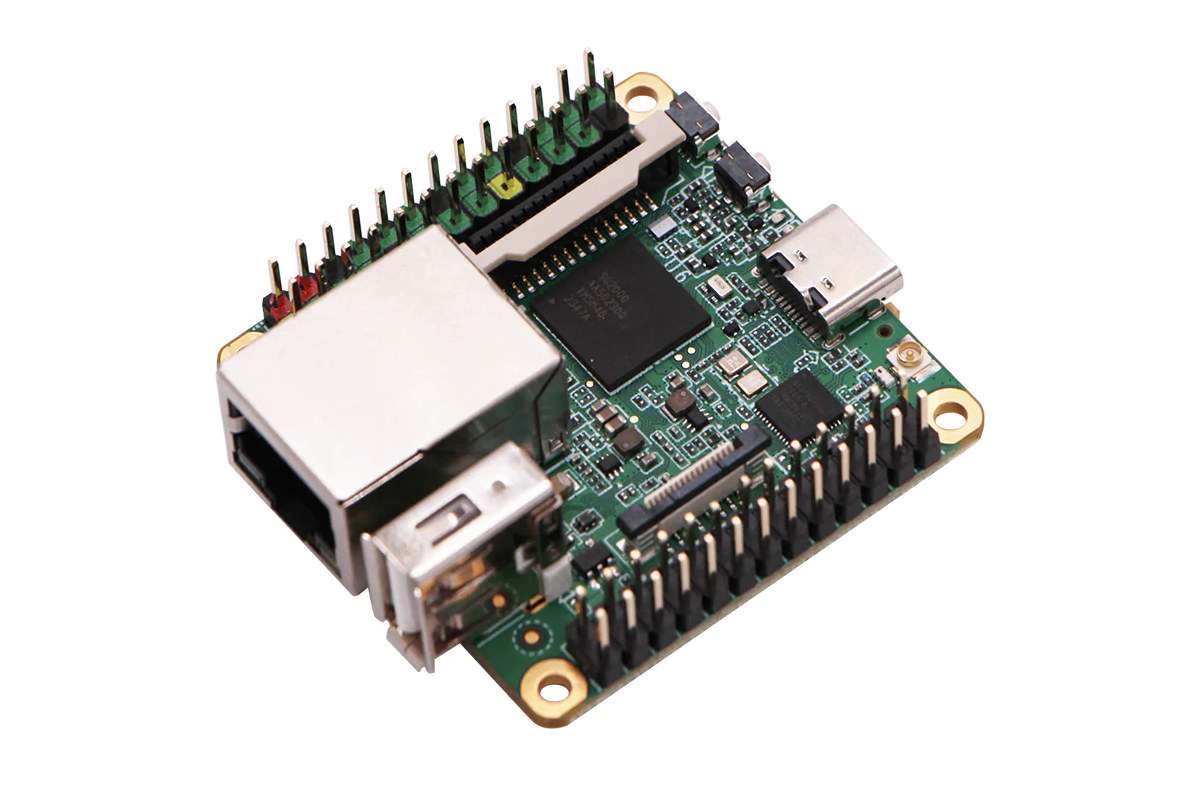

Duo S RISC-V/Arm SBC features Sophgo SG2000 SoC, Ethernet, WiFi 6, and Bluetooth 5 connectivity

Shenzhen MilkV Technology’s Duo S is a tiny SBC based on the 1 GHz Sophgo SG2000 Arm Cortex-A53 and RISC-V SoC with 512MB DDR3 (SiP), Fast Ethernet, WiFi 6, and Bluetooth 5 connectivity, and a switch to select Arm or RISC-V architecture before powering the board. We already had covered SG2002 Arm/RISC-V boards with 256MB RAM, namely the LicheeRV Nano and Duo 256M, but for people needing more memory, the Duo S provides another option that also features two 2-lane MIPI CSI connectors, a USB 2.0 host port, and two 26-pin headers for expansion. Its form factor reminds me of FriendlyELEC’s NanoPi NEO and family powered by Allwinner processors that were introduced a few years ago. Duo S specifications: SoC – SOPHGO SG2000 Main core – 1 GHz 64-bit RISC-V C906 or Arm Cortex-A53 core (selectable) Minor core – 700 MHz 64-bit RISC-V C906 core Low-power core – 25 to […]