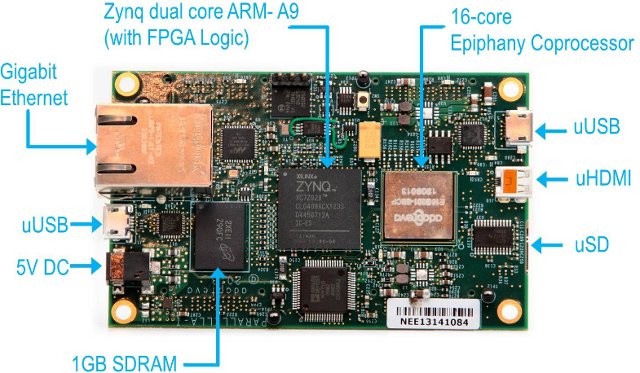

Parallella is a low cost supercomputer designed by Adapteva using Xilinx Zynq-7010/7020 FPGA+2x Cortex A9 SoC combined with Adapteva Ephipany 16 or 64 cores epiphany coprocessor. The project had a successful kickstarter campaign which allowed then to provide the 16-core version for $99, and the 64-core version for $750. The board will soon be shipped to people who pledged on kickstarter, and one of the promise of the campaign was to fully open source the platform, and today, they just fulfilled that. Before going into the details of the open source release, let’s have a look at the specs: SoC – Xilinx Zynq7000 Series (Z-7010 or Z-7020) Dual-Core ARM Cortex A9 with 512KB L2 Shared Cache Coprocessor – Epiphany Multicore Coprocessor. The Parallella-16 board includes the 16-core Epiphany-III processor The Parallella-64 board includes the 64-core Epiphany-IV processor System Memory – 1024MB DDR3L Boot Flash – 128 Mb QSPI Flash Indicators […]

EnSilica eSi-ZM1 System-on-Module Features Xilinx Zynq XC7Z020 SoC

EnSilica has introduced the eSi-ZM1 SoM powered by Zynq ZC7Z020 SoC featuring 2 ARM Cortex A9 core, and an Artix-7 FPGA with 85K logic cells. The module also comes with 1GB RAM, 1GB NAND flash, and 16MB QSPI Boot Flash. ZC7Z020 SoC is notably used in ZedBoard development board, so if you have developed an application around this board, and want to commercialize it, using eSi-ZM1 module with your own custom baseboard could be an option. eSi-ZM1 system-on-module specifications: SoC – Xilinx Zynq XC7Z020 dual-core Cortex A9 processor @ 666 MHz, 85 K logic cells, 560 KB block RAM, and 220 DSP Slices. CLG484 package type System Memory – 1 GB, 1.35 V, 32-bit wide DDR3 SDRAM @ 533 MHz Storage: 1 GB, 1.8 V, 8-bit wide NAND FLASH 16 MB QSPI flash 1 or 2 Kb I2C EEPROM (and not 1MB as mentioned in the block diagram ) uSD card […]

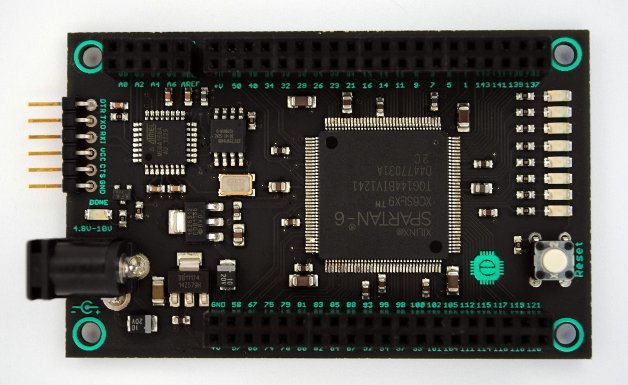

The Mojo – $65 FPGA Development Board Powered By Xilinx Spartan 6

Embedded Micro has started a kickstarter campaign to fund an FPGA board called “the Mojo”, “designed to be user friendly and a great introduction into digital design”. The board is powered by a Xilinx Spartan 6 FPGA that comes with over 9,000 logic cells, and will allow you to design digital circuits composed of a bunch of logic and, or, nor, etc… gates connected together to perform a specific task. Here are the features of “The Mojo”: Spartan 6 XC6SLX9 FPGA – 9,152 logic cells for your largest designs 84 general purpose digital IO pins (3.3V logic level) 8 analog inputs 8 user controlled LEDs A USB connection (new revision) to configure the FPGA and send receive data from your design On board voltage regulation (4.5V – 12V input, 3.3V and 1.2V outputs) 8 MHz on-board clock (can be multiplied internally by the FPGA) A reset button to be used in your designs […]

Zedboard Xilinx Zynq-7000 Community Board is Now Available

Based in March, I wrote about Xilinx Zynq-7000 Extensible Processing Platform (EPP), a SoC comprises of a Dual Cortex A9 and an FPGA, as well as the corresponding development boards and kits: Xilinx Zynq-7000 EPP ZC702 Evaluation Kit based on Zynq-7020 with all the basic components (595 USD). Xilinx Zynq-7000 EPP Video Kit based on Zynq-7020 with all necessary hardware, software and IP components for the development of custom video applications (1195 USD). Zynq-7000 EPP ZedBoard, a low cost development board for the developers community. At the time, the first 2 (expensive) boards were available, but there was little information about the Zedboard. But yesterday evening, I noticed Zedboard website had a lot more information and we now know details about the board and it is even possible to purchase it. Here are the Zedboard specifications: Processor – Xilinx Zynq-7020 Dual ARM Cortex-A9 MPCore @ 677 MHz Memory 512 MB […]

Xilinx Zynq-7000 Extensible Processing Platform (EPP): Dual Cortex A9 + FPGA SoC

The Xilinx Zynq-7000 EPP (Extensible Processing Platform) is a new class of device, offering a mix of a dual-core ARM Cortex-A9 subsystem (including cache, memory controllers, interface, and peripheral functions) with a 28-nm programmable digital FPGA and programmable analog capabilities. This combination opens the door to a range of demanding applications, including automotive (video processing and analytics requirements for driver assistance systems), broadcast (high-bit-rate bandwidth for high-accuracy video processing and analytics), and industrial control systems that combine high-processing demands with tight integration requirements. There are actually 4 models which share the same processing subsystem (CPU core, memory, peripherals, etc…) and only differ by the programmable logic used: Z-7010 – Artix-7 FPGA with 28K logic cells. Z-7020 – Artix-7 FPGA with 85K logic cells. Z-7030 – Kintex-7 FPGA with 125K logic cells. Z-7045 – Kintex-7 FPGA with 350K logic cells. The Zynq-7000 EPP platform allows concurrent software and hardware development: System […]

Linux 3.1 Release

Linux Torvalds announced the release of Linux Kernel 3.1 yesterday: As promised, the kernel summit has started, and Linux-3.1 is out. The (small) shortlog of changes since -rc10 are appended, we have mostly some sparc and networking changes, along with some radeon and intel iommu fixes (mostly for largepages and integrated graphics issues). Most people probably will not notice the changes. One big change from -rc10 is that there are tar-balls and patches, so if you aren’t a git user (why?) you can download it now in a traditional format. On of the things to note is that the files are now signed by my gpg key, and it’s the *uncompressed* version that the signature is for. And of course, this means that the merge window for 3.2 is open. I’ll do some merging during the KS, but probably most when I get back home – but you can still […]

Embedded MasterClass Conference Schedule in Cambridge, UK

Embeded MasterClass will take place in Cambridge on the 5th of October 2011. This conference will give you the chance to meet with embedded systems engineers from many of the world’s leading vendors and you’ll be able to attend presentations and workshops free of charge. Here’s the presentations’ schedule for the event: Time Stream 1 Stream 2 8.30 – 9.30 Tea/Coffee – Meet the Exhibitors 9.30 – 10.15 1: Leveraging the Performance of Intel® Architectures in low power, fan-less solutions with the latest Intel® Atom™ processor-based platform. Regis Cheval CEng MIET, Intel® Atom™ Platform Application Engineer – Intel 10.30 – 11.15 2: Proving your code quality. Barry Lock – Lauterbach 3: Developing reliable embedded systems using COTS and custom processors. Michael Pont, CEO – TTE Systems 11.15 – 11.45 Coffee and Exhibition 11.45 – 12.30 4: Strategic Research Agenda. Helen Finch – Artemis and Infineon 5: Safely from Conception to […]