ESP Open Source Research Platform Enables the Design of RISC-V & Sparc SoC’s with Accelerators

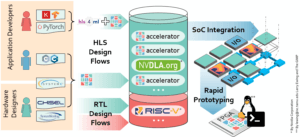

FOSDEM 2020 will take place next week, and there will be several interesting talks about open-source hardware and software development. One of those is entitled “Open ESP – The Heterogeneous Open-Source Platform for Developing RISC-V Systems” with an excerpt of the abstract reading: ESP is an open-source research platform for RISC-V systems-on-chip that integrates many hardware accelerators. ESP provides a vertically integrated design flow from software development and hardware integration to full-system prototyping on FPGA. For application developers, it offers domain-specific automated solutions to synthesize new accelerators for their software and map it onto the heterogeneous SoC architecture. For hardware engineers, it offers automated solutions to integrate their accelerator designs into the complete SoC. If we go to the official website, we can see ESP (Embedded Scalable Platform) actually supports both 32-bit Leon3 (Sparc) and 64-bit Ariane (RISC-V) cores, and various hardware accelerators from the platform or third parties. Highlights: […]