Microchip has recently released the SAMA7D65 MPU, a high-performance Arm Cortex-A7 embedded processor designed for HMI and connectivity applications across industrial, home, medical, and appliance markets. The MPU is available in both System-in-Package (SiP) and System-on-Chip (SoC) variants and features various display interfaces, including MIPI DSI, LVDS, and 8-bit Serial RGB interfaces, along with a 2D GPU for graphical acceleration. Memory and storage options include support for 16-bit DDR2/DDR3/DDR3L and LPDDR2/3 memory, optional 1 Gbit or 2 Gbit DDR3 RAM, NAND Flash, eMMC Flash, and SD card. It features dual Gigabit Ethernet with TSN support, an I3C controller, five CAN-FD interfaces, and three high-speed USB ports. Additionally, it comes with various security features, including physically unclonable function (PUF), secure boot, key storage, and cryptographic accelerators for AES, SHA, RSA, and ECC. Microchip SAMA7D65 SoC/SiP specifications: CPU – Arm Cortex-A7 core up to 1 GHz Arm TrustZone, NEON, FPU 32KB L1 I-cache […]

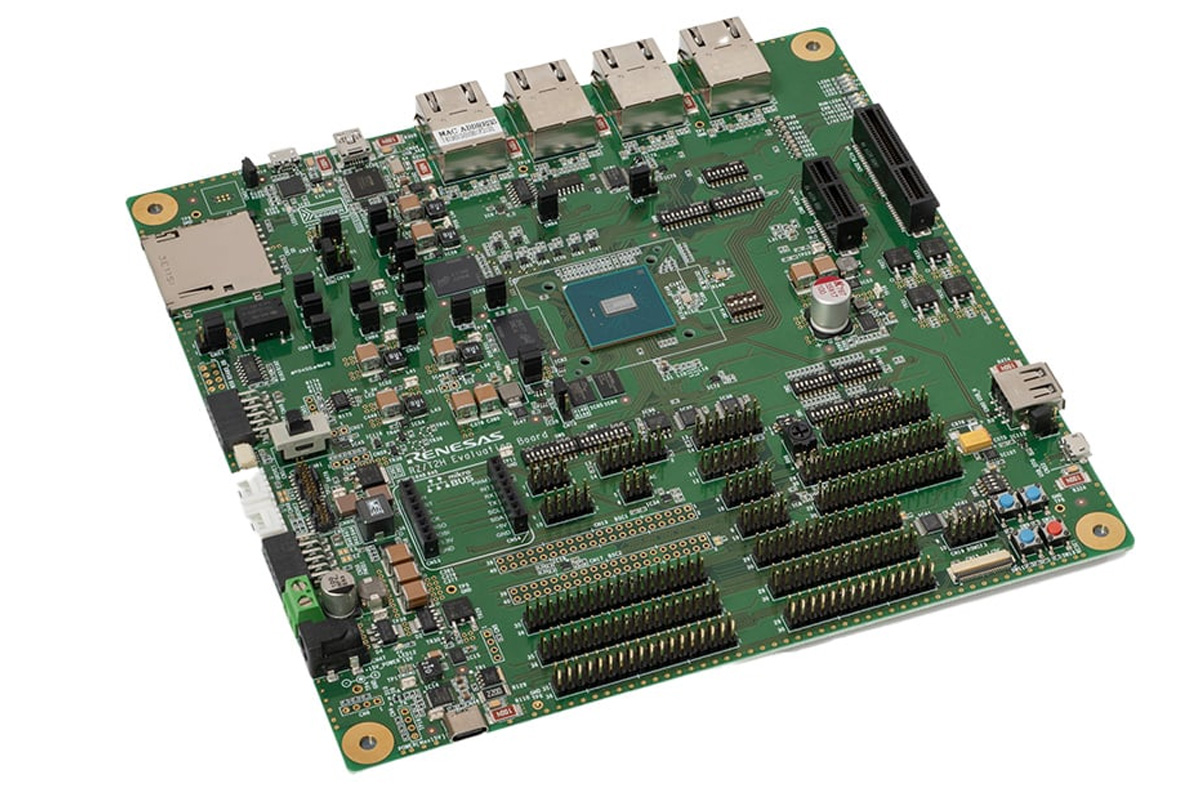

Renesas RZ/T2H Cortex-A55/R52 industrial MPU and Dev Board support EtherCAT, PROFINET, and TSN

Renesas RZ/T2H industrial MPU is the most powerful member of its RZ/T2 series of real-time microprocessors. The MPU features four Arm Cortex-A55 CPUs for application tasks and two Cortex-R52 CPUs for real-time control. It supports 9-axis motor control with 3-phase PWM timers, delta-sigma interfaces, and encoder interfaces. It also supports Industrial Ethernet protocols like EtherCAT, PROFINET, and TSN. These features make it ideal for industrial applications such as industrial robots, PLCs, motion controllers, and CNC machines. Renesas launched the RZ/T2L single-core Arm Cortex-R52 MPU just last year, and before that, in 2022, they launched the RZ/T2M dual Arm Cortex-R52 MPU. The RZ/T2L was just a cost-down version of RZ/T2M with an EtherCAT controller, compared to those old controllers the latest RZ/T2H supports 9-axis motor control and compatibility with various industrial Ethernet protocols. Renesas RZ/T2H specifications: CPU 4x Arm Cortex-A55 (64-bit) clocked at up to 1.2GHz with 32KB L1 I/D cache, 1MB L3 cache 2x […]

Linux 6.7 release – Main changes, Arm, RISC-V, and MIPS architectures

Linus Torvalds has just announced the release of Linux 6.7, following Linux 6.6 LTS a little over two months ago: So we had a little bit more going on last week compared to the holiday week before that, but certainly not enough to make me think we’d want to delay this any further. End result: 6.7 is (in number of commits: over 17k non-merge commits, with 1k+ merges) one of the largest kernel releases we’ve ever had, but the extra rc8 week was purely due to timing with the holidays, not about any difficulties with the larger release. The main changes this last week were a few DRM updates (mainly fixes for new hw enablement in this version – both amd and nouveau), some more bcachefs fixes (and bcachefs is obviously new to 6.7 and one of the reasons for the large number of commits), and then a few random […]

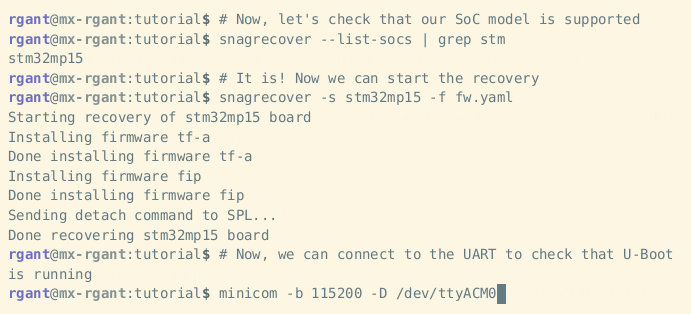

Snagboot is an open-source cross-vendor recovery tool for embedded targets

Bootlin has just released the Snagboot open-source recovery tool for embedded platforms designed to work with multiple vendors, and currently STMicro STM32MP1, Microchip SAMA5, NXP i.MX6/7/8, Texas Instruments AM335x and AM62x, and Allwinner “sunxi” processors are supported. Silicon vendors usually provide firmware flashing tools, some closed-source binaries, that only work with their hardware. So if you work on STM32MP1 you’d use STM32CubeProgrammer, while SAM-BA is the tool for Microchip processors, NXP i.MX SoC relies on UUU, and if you’ve ever worked on Allwinner processors you’re probably family with sunxi-fel. Bootlin aims to replace all those with the Snagboot recovery tool. The Python tool is comprised of two parts: snagrecover using vendor-specific ROM code mechanisms to initialize external RAM and run the bootloader (typically U-Boot) without modifying any non-volatile memories. snagflash communicates with the bootloader over USB to flash system images to non-volatile memories, using either DFU, USB Mass Storage, or […]

Linux 6.1 LTS release – Main changes, Arm, RISC-V and MIPS architectures

Linus Torvalds announced the release of Linux 6.1, likely to be an LTS kernel, last Sunday: So here we are, a week late, but last week was nice and slow, and I’m much happier about the state of 6.1 than I was a couple of weeks ago when things didn’t seem to be slowing down. Of course, that means that now we have the merge window from hell, just before the holidays, with me having some pre-holiday travel coming up too. So while delaying things for a week was the right thing to do, it does make the timing for the 6.2 merge window awkward. That said, I’m happy to report that people seem to have taken that to heart, and I already have two dozen pull requests pending for tomorrow in my inbox. And hopefully I’ll get another batch overnight, so that I can try to really get as […]

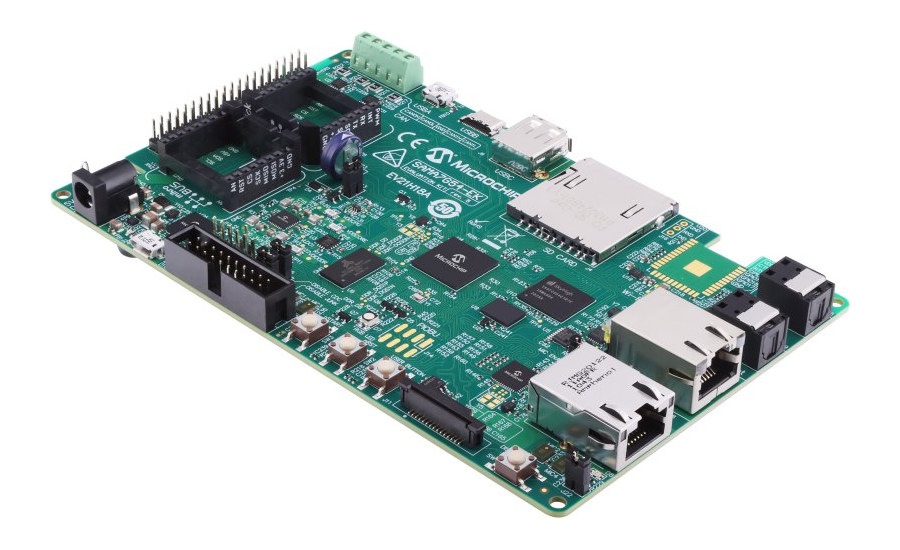

Microchip SAMA7G54 is a single-core Arm Cortex-A7 microprocessor for low power AI camera & audio applications

Microchip has just announced the 1 GHz SAMA7G54 single-core Arm Cortex-A7 microprocessor (MPU) with MIPI CSI-2 and parallel camera interfaces, as well as up to four I2S, one SPDIF transmitter and receiver, and a 4-stereo channel audio sample rate converter. The company specifically launched a single-core processor to offer a lower power solution for AI camera and audio solutions, and the chip is coupled with the MCP16502 power management IC that has been optimized to provide the best power/performance ratio for the SAMA7G54. Microchip SAMA7G54 specifications: CPU – Arm Cortex-A7 based MPU @ up to 1GHz with 256KB L2 cache Memory – DDR2/DDR3/DDR3L/LPDDR2/LPDDR3 up to 533MHz Storage – Quad SPI, Octal SPI, 3x SD/eMMC Camera I/F – MIPI CSI-2 (2-lane up to 1.5 Gbps each) and 12-bit parallel camera Up to 8 Mpixel @ 30 fps Audio – Up to 4x I2S, PDM, SPDIF (Rx/Tx), 4 stereo channel ASRC Networking […]

Linux 5.17 release – Main changes, Arm, RISC-V, and MIPS architectures

Linus Torvalds has just released Linux 5.17: So we had an extra week of at the end of this release cycle, and I’m happy to report that it was very calm indeed. We could probably have skipped it with not a lot of downside, but we did get a few last-minute reverts and fixes in and avoid some brown-paper bugs that would otherwise have been stable fodder, so it’s all good. And that calm last week can very much be seen from the appended shortlog – there really aren’t a lot of commits in here, and it’s all pretty small. Most of it is in drivers (net, usb, drm), with some core networking, and some tooling updates too. It really is small enough that you can just scroll through the details below, and the one-liner summaries will give a good flavor of what happened last week. Of course, this means […]

Linux 5.15 LTS release – Main Changes, Arm, RISC-V and MIPS architectures

Linus Torvalds released Linux 5.15, an LTS version, this past Sunday: It’s been calm, and I have no excuse to add an extra rc, so here we are, with v5.15 pushed out, and the merge window starting tomorrow. Which is going to be a bit inconvenient for me, since I also have some conference travel coming up. But it’s only a couple of days and I’ll have my laptop with me. Sometimes the release timing works out, and sometimes it doesn’t.. Anyway, the last week of 5.15 was mainly networking and gpu fixes, with some random sprinkling of other things (a few btrfs reverts, some kvm updates, minor other fixes here and there – a few architecture fixes, couple of tracing, small driver fixes etc). Full shortlog appended. This release may have started out with some -Werror pain, but it calmed down fairly quickly and on the whole 5.15 was […]