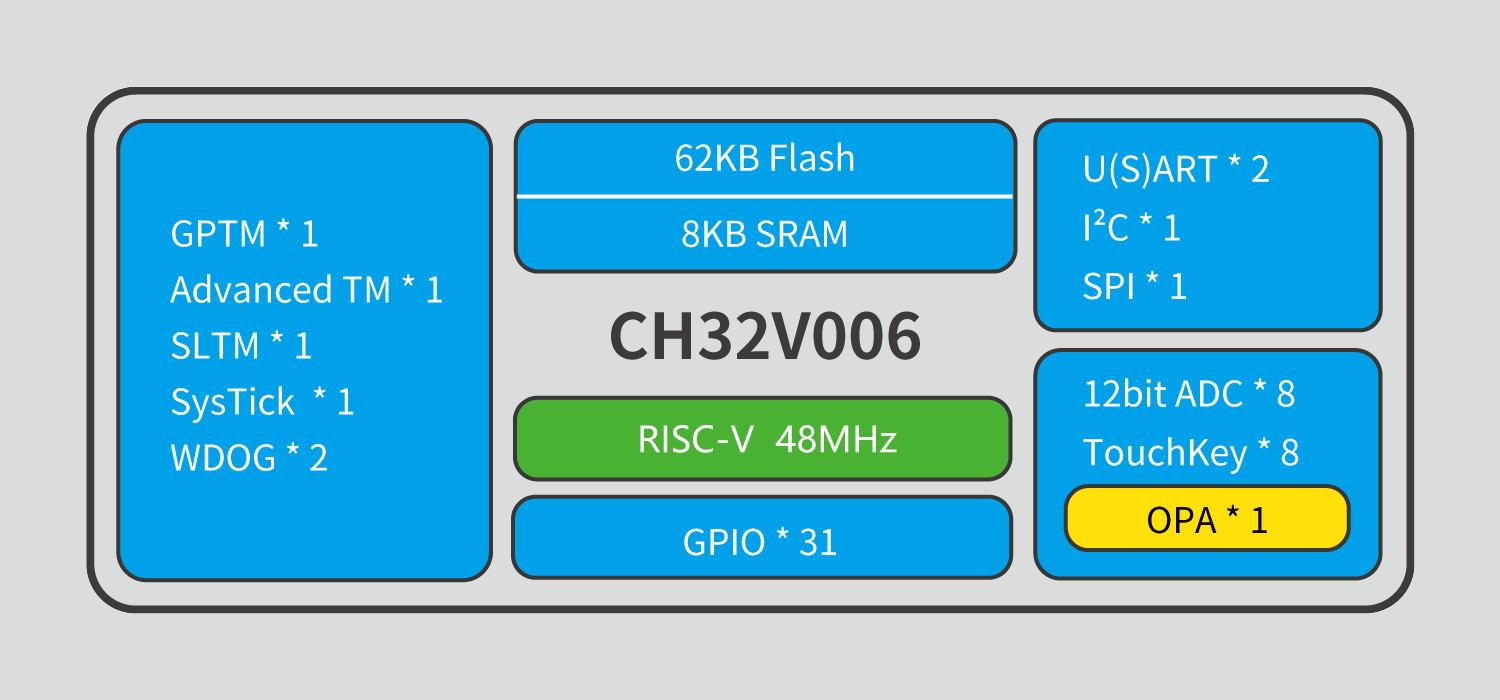

WCH CH32V006 RISC-V microcontroller is an upgrade to the 10-cent CH32V003 microcontroller with more I/Os, up to four times the memory, storage, a wider supply voltage range, the addition of a TouchKey interface, as well as a new 32-bit V2C RISC-V core instead of the V2A core found in the CH32V003. More specifically that means we went from the CH32V003 with 2KB SRAM and 8KB flash, up to 8KB SRAM and 62KB for the CH32V006, and 6KB SRAM and 32KB flash for the CH32V005, a smaller sibling of the new RISC-V microcontroller. WCH CH32V005 & CH32V006 specifications (with highlights in bold to show differences against CH32V003): CPU – 32-bit “RISC-V2C” core up to 48 MHz Memory – 6KB SRAM (CH32V005) or 8KB SRAM (CH32V006) Storage – 32KB flash (CH32V005) or 62KB flash (CH32V006) Peripherals Up to 31x GPIO with interrupt support (CH32V003 had up to 18x GPIO) 2x USART interfaces […]

QEMU 9.0 released with Raspberry Pi 4 support and LoongArch KVM acceleration

QEMU 9.0 open-source emulator just came out the other day, and it brings on board major updates and improvements to Arm, RISC-V, HPPA, LoongArch, and s390x emulation. But the most notable updates are in Arm and LoongArch emulation. The QEMU 9.0 emulator now supports the Raspberry Pi 4 Model B, meaning you can run the 64-bit Raspberry Pi OS for testing applications without owning the hardware. However, QEMU 9.0 has some limitations since Ethernet and PCIe are not supported for the Raspberry Pi board. According to the developers, these features will come on board in a future release. For now, the emulator supports SPI and I2C (BSC) controllers. Still on ARM, QEMU 9.0 provides board support for the mp3-an536 (MPS3 dev board + AN536 firmware) and B-L475E-IOT01A IoT node, plus architectural feature support for Nested Virtualization, Enhanced Counter Virtualization, and Enhanced Nested Virtualization. If you develop applications for the LoongArch […]

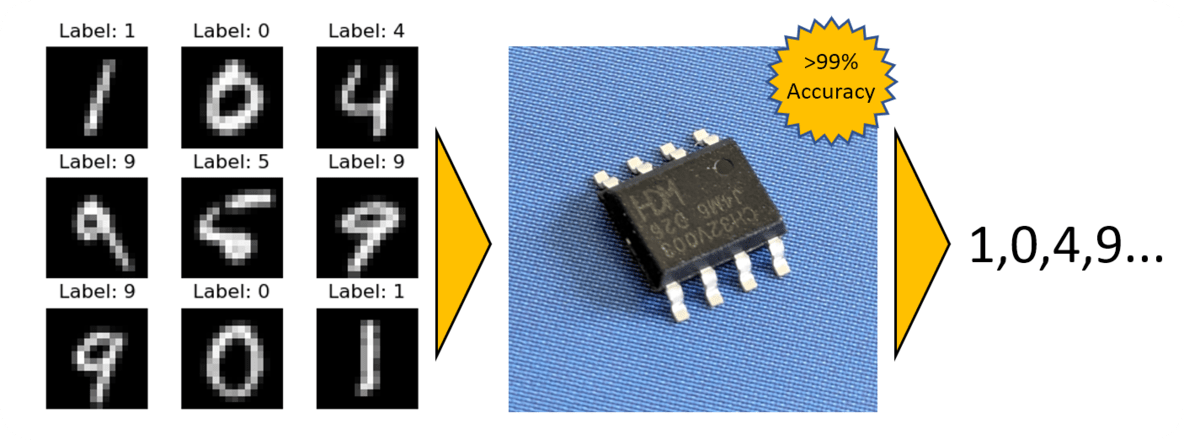

BitNetMCU project enables Machine Learning on CH32V003 RISC-V MCU

Neural networks and other machine learning processes are often associated with powerful processors and GPUs. However, as we’ve seen on the page, AI is also moving to the very edge, and the BitNetMCU open-source project further showcases that it is possible to run low-bit quantized neural networks on low-end RISC-V microcontrollers such as the inexpensive CH32V003. As a reminder, the CH32V003 is based on the QingKe 32-bit RISC-V2A processor, which supports two levels of interrupt nesting. It is a compact, low-power, general-purpose 48MHz microcontroller that has 2KB SRAM with 16KB flash. The chip comes in a TSSOP20, QFN20, SOP16, or SOP8 package. To run machine learning on the CH32V003 microcontroller, the BitNetMCU project does Quantization Aware Training (QAT) and fine-tunes the inference code and model structure, which makes it possible to surpass 99% test accuracy on a 16×16 MNIST dataset without using any multiplication instructions. This performance is impressive, considering […]

Android no longer supports RISC-V, for now…

Google dropped RISC-V support from the Android’s Generic Kernel Image in recently merged patches. Filed under the name “Remove ACK’s support for riscv64,” the patches with the description “support for risc64 GKI kernels is discontinued” on the AOSP tracker removed RISC-V kernel support, RISC-V kernel build support, and RISC-V emulator support. In simple terms, the next Android OS implementation that will use the latest GKI release won’t work on devices powered by RISC-V chips. Therefore, companies wanting to compile a RISC-V Android build will have to create and maintain their own branch from the Linux kernel (ACK RISC-V patches). These abbreviations can be confusing, so let’s focus on them starting with ACK. There’s the official Linux kernel, and Google does not certify Android devices that ship with this mainline Linux kernel. Google only maintains and certifies the ACK (Android Common Kernel), which are downstream branches from the official Linux kernel. One of the main ACK branches is the android-mainline […]

Yocto Project 5.0 “Scarthgap” released with Linux 6.6 and plenty of changes

The Yocto Project 5.0 codenamed “Scarthgap” has just been released with Linux 6.6, glibc 2.39, LLVM 18.1, and over 300 other recipe upgrades. As a result of the release, the developers have made it available for download (bz2 tarball). The Yocto Project, or Yocto for shorts, is a popular framework used to create custom embedded Linux distributions, and we’ve played with it over the year showing how to create a minimal image for the Raspberry Pi, and last year, we used it again when reviewing two industrial development boards, namely the VOIPAC IMX8M and ADLINK i-Pi SMARC 1200. Yocto is quite a powerful framework/build system with plenty of options that make it highly customizable, but the learning curve is fairly steep. Some other changes in Yocto Project 5.0 include: New variables: CVE_DB_INCR_UPDATE_AGE_THRES: Configure the maximum age of the internal CVE database for incremental update (instead of a full redownload). RPMBUILD_EXTRA_PARAMS: […]

Muse Book laptop features SpacemiT K1 octa-core RISC-V AI processor, up to 16GB RAM

SpacemiT, a chip design company from China with RISC-V as its core technology, recently unveiled the Muse Book laptop based on the K1 octa-core RISC-V chip. Unlike our daily laptops, it has many interesting unique features and is mainly sold to hardware engineers and DIY enthusiasts. This Muse Book runs the Bianbu OS operating system based on the Debian distribution and optimized to run on the SpacemiT K1 octa-core RISC-V SoC. Let’s first take a look at its external interfaces. On the left side of the laptop, there are two USB Type-C interfaces, a USB 3.0 Type-A port, a 3.5mm headphone jack, a microSD card slot, and a reset pinhole. The 8-pin header on the right side of the laptop is quite interesting, and SpacemiT hopes the Muse Book can become one of the most convenient hardware development platforms for RISC-V. In addition to the power pins, users will find […]

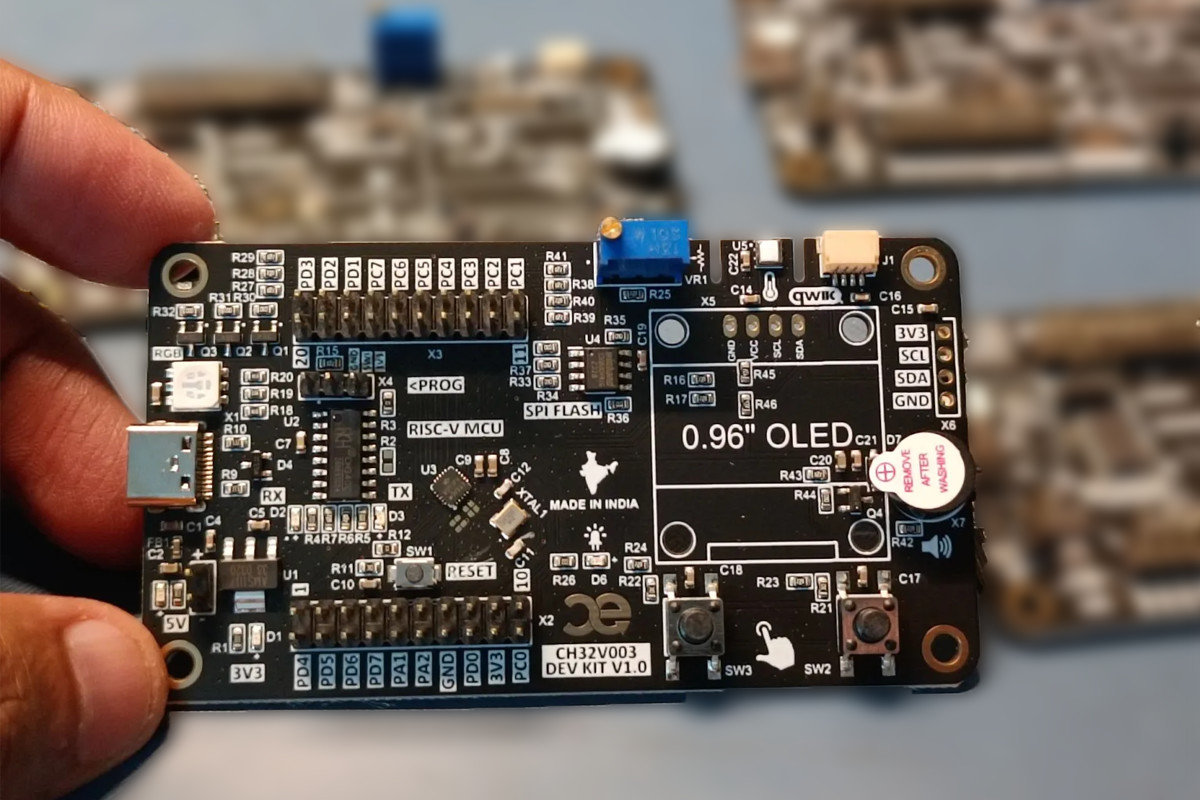

CAPUF Embedded CH32V003 RISC-V Dev Kit features USB-C, temperature/humidity monitoring, OLED & more

CAPUF Embedded CH32V003 Dev Kit is an all-in-one development board with a USB-C interface, onboard sensors (temperature/humidity), an OLED display, SPI NOR Flash, and ample I/O options. Additionally, it features a Qwicc connector, an RGB LED, and a 3-pin header to connect the WCH-link programmer providing further flexibility for your projects. After the initial release of this “10 cents” CH32V003 RISC-V microcontroller, we have seen $1.5 development boards and an open-source GGC toolchain, as well as Arduino support for the WCH RISC-V microcontrollers. Very recently, CNLohr even managed to transmit LoRa packets with this MCU. CAPUF Embedded CH32V003 Dev Kit Specifications: MCU – WCH CH32V003F4U6 32-bit RISC-V2A microcontroller up to 48 MHz with 2KB SRAM, 16KB flash (QFN20 package) USB – 1x USB-C Port for Power (5V) and Serial Interface with onboard USB to UART converter I/Os – 20 Pin MCU IOs with USART, I2C, SPI, ADC Program & Debugging – […]

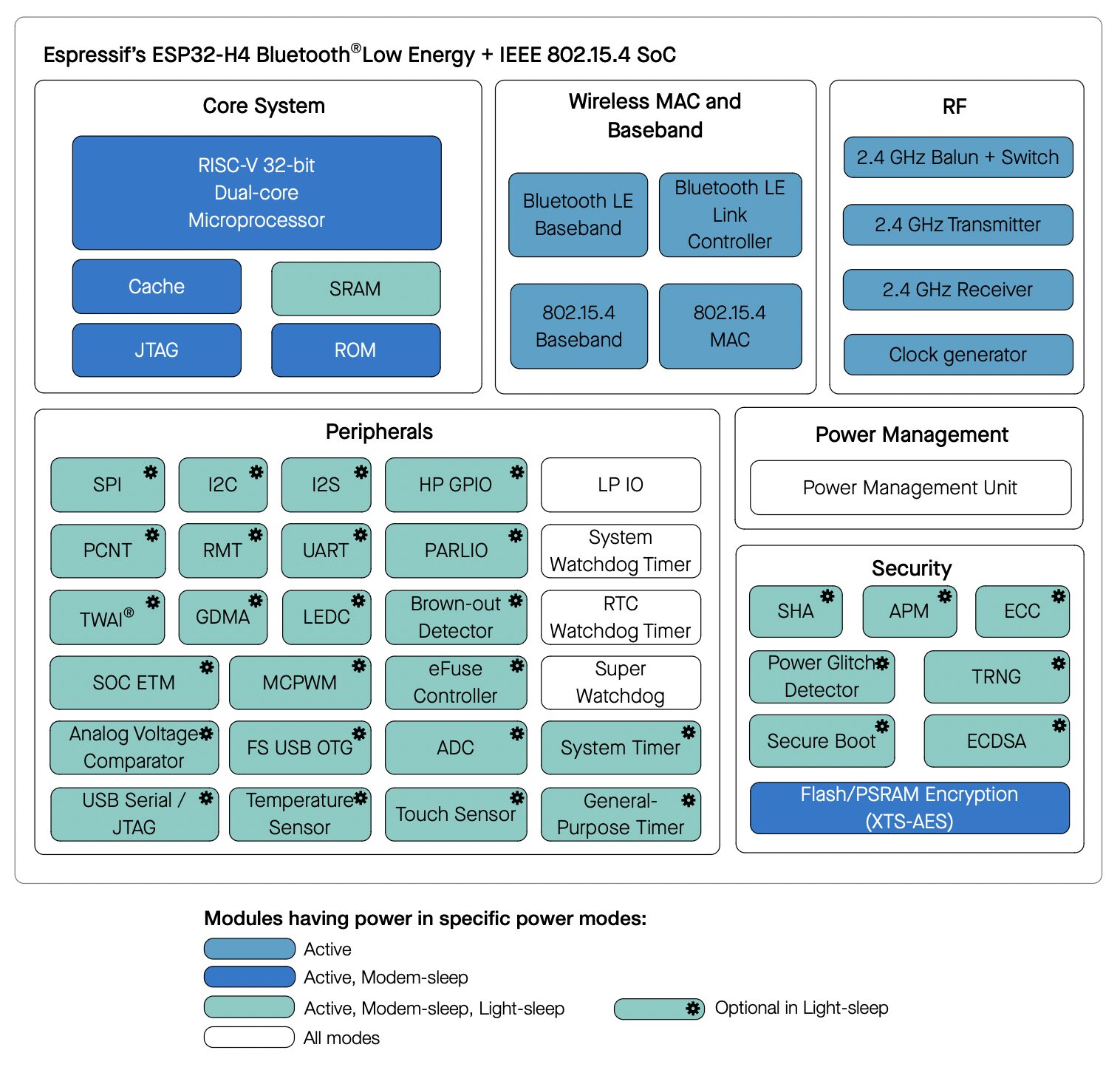

ESP32-H4 low-power dual-core RISC-V SoC supports 802.15.4 and Bluetooth 5.4 LE

Espressif Systems has formally announced the ESP32-H4 low-power dual-core 32-bit RISC-V wireless microcontroller with support for 802.15.4 and Bluetooth 5.4 LE portfolio after having unveiled it at CES 2024. It’s the first Espressif chip to support Bluetooth 5.4 LE with previous models such as ESP32-H2 or ESP32-C6 only supporting Bluetooth 5.0/5.2. Besides BLE 5.4 support, the new ESP32-H4 dual-core RISC-V WiSoC is an evolution of the ESP32-H2 single-core chip with PSRAM support (up to 4MB built-in), additional GPIOs (36 vs 24), touch sensing GPIOs, and some extra security features such as a power glitch detector also found in the recently announced ESP32-C61. ESP32-H4 specifications: CPU – Dual-core 32-bit RISC-V core (at up to 96 MHz) RAM – 320KB KB SRAM, optional PSRAM up to 4MB Storage – 128KB ROM, External flash support Wireless connectivity IEEE 802.15.4 radio with Zigbee and Thread support, Matter protocol Bluetooth 5.4 (LE) radio designed in-house, […]