The Allwinner H135 is a 64-bit RISC-V multimedia SoC officially designed for low-cost projectors. However, support for HDMI Rx and MJPEG 1080p60 video encoding also makes it suitable for entry-level KVM (Keyboard, Video, and Mouse) solutions. The H135 is based on the XuanTie C906 core, supports up to 256MB DDR2/DDR3/DDR3L, integrates a 1080p60 H.265/H.264 video decoder, MIPI DSI, dual-channel LVDS, and RGB888 display interfaces, and plenty of peripherals such as USB, SDIO, UART, SPI, PWM, GPIO, and more. Allwinner H135 specifications: CPU – XuanTie C906 RISC-V CPU with 64 KB I-cache + 64 KB D-cache Display Engine Allwinner Awonder1.1 Lite post processing Keystone correction in online mode and [-360°,360°] rotation in offline mode De-interlace (DI) up to 1920×1080 @ 60fps G2D hardware accelerator with rotate and mixer functions VPU Video decoding – H.265, H.264, H.263, MPEG-1/2/4, and VC-1 up to 1080p60 Image decoding – JPEG up to 1080p60 Video encoding […]

XIAO Vision AI Camera combines ESP32-C3 and WiseEye2 HX6538 AI MCU with 5MP camera, supports SenseCraft no-code platform

Seeed Studio has recently released the XIAO Vision AI Camera, a compact, open-source smart ESP32-C3 AI Camera that integrates the Grove Vision AI Module V2, a XIAO ESP32C3 module, and an OV5647 5MP camera in a custom 3D-printed PLA case. One of the key components of the camera module is the WiseEye2 HX6538 chip, which features dual-core Arm Cortex-M55 processors and an Ethos-U55 NPU for edge AI computing. It also comes with Wi-Fi connectivity, turning it into an intelligent IP camera that easily integrates with Home Assistant for closed-loop automation (e.g., object detection triggering lights or alerts). Its 5MP OV5647 camera can record 1080p@30fps video and has adjustable focus. These features make this camera useful for industrial automation, smart cities, transportation monitoring, intelligent agriculture, and mobile IoT devices. XIAO Vision AI Camera Specifications Main MCU module – XIAO ESP32C3 SoC – Expressif Systems ESP32-C3 CPU – Single-core RISC-V microcontroller @ […]

Sipeed Tang Console – A GOWIN GW5AST/GW5AT board with 60K or 138K LUT for FPGA development and retro gaming

Sipeed Tang Console is an FPGA development based on GOWIN GW5AST SoC FPGA with 138K LUTs and a hard RISC-V core or GW5AT FPGA with 60K LUTs, designed as a generic FPGA development and retro gaming platform. The Tange Console offers HDMI and RGB LCD display connectors, two USB ports for joystick or other peripherals, and plenty of expansion options with two 40-pin headers for SDRAM, GBA, and custom expansion, two PMOD connectors for joysticks or custom modules, and a 16-pin Raspberry Pi PCIe FFC connector. The “Tang Console” is also integrated into the “Tang Retro Console” as a complete gaming console kit with enclosure, joysticks, and accessories. Sipeed Tang Console specifications: SoM(one or the other) Sipeed Tang Mega 138K SoC FPGA – GOWIN GW5AST-LV138FPG484A with 138,240 LUT4 1,080 Kb Shadow SRAM (SSRAM) 6,120 Kb Block SRAM (BSRAM) Number of BSRAM – 340 298x DSP slices 12x PLLs 16x global […]

Linux 6.15 Release – Main changes, Arm, RISC-V and MIPS architectures

Linus Torvalds has just announced the release of Linux 6.15: So this was delayed by a couple of hours because of a last-minute bug report resulting in one new feature being disabled at the eleventh hour, but 6.15 is out there now. Apart from that final scramble, things looked pretty normal last week. Various random small fixes all over, with drivers as usual accounting for most of it. But we’ve got some bcachefs fixes, some core networking, and some mm fixes in there too. Nothing looks particularly scary. And this obviously means that the merge window opens tomorrow as usual, and I see the usual people being proactive and having sent me their pull requests. It’s memorial day tomorrow here in the US, but like the USPS, “neither snow nor rain nor heat nor gloom of night” – nor memorial day – stops the merge window. [ Actually, thinking back […]

Jupiter NX SoM – An NVIDIA Jetson Nano/NX alternative powered by SpacemiT K1 octa-core RISC-V SoC

The Jupiter NX is a system-on-module (SoM) powered by a SpacemIT octa-core 64-bit RISC-V SoC that follows NVIDIA’s Jetson Nano / Xavier NX form factor for compatibility with existing carrier boards. Designed by Shenzhen Milk-V Technology, the module supports up to 16GB LPDDR4x memory and 32GB eMMC flash, and integrates two gigabit Ethernet PHYs and a WiFi 6 & Bluetooth 5.2 wireless module. Jupiter NX specifications: SoC – SpacemIT K1/M1 CPU – 8-core X60 RISC-V (RV64GCVB) processor @ 1.6 GHz GPU – Imagination IMG BXE-2-32 @ 819 MHz with support for OpenGL ES3.2, Vulkan 1.3, OpenCL 3.0; 20 GFLOPS VPU H.265, H.264, VP8, VP9, MPEG4, MPEG2 decoder up to 4K @ 60fps H.265, H.264, VP8, VP9 encoder up to 4K @ 30fps Support simultaneous processing 1080p60 encoding + 1080p60 decoding 1080p30 H.264/H.265 encoding + 4Kp30 H.264/H.265 decoding AI performance – 2.0 TOPS (INT8) through “CPU core fusion” RVA 22 Profile […]

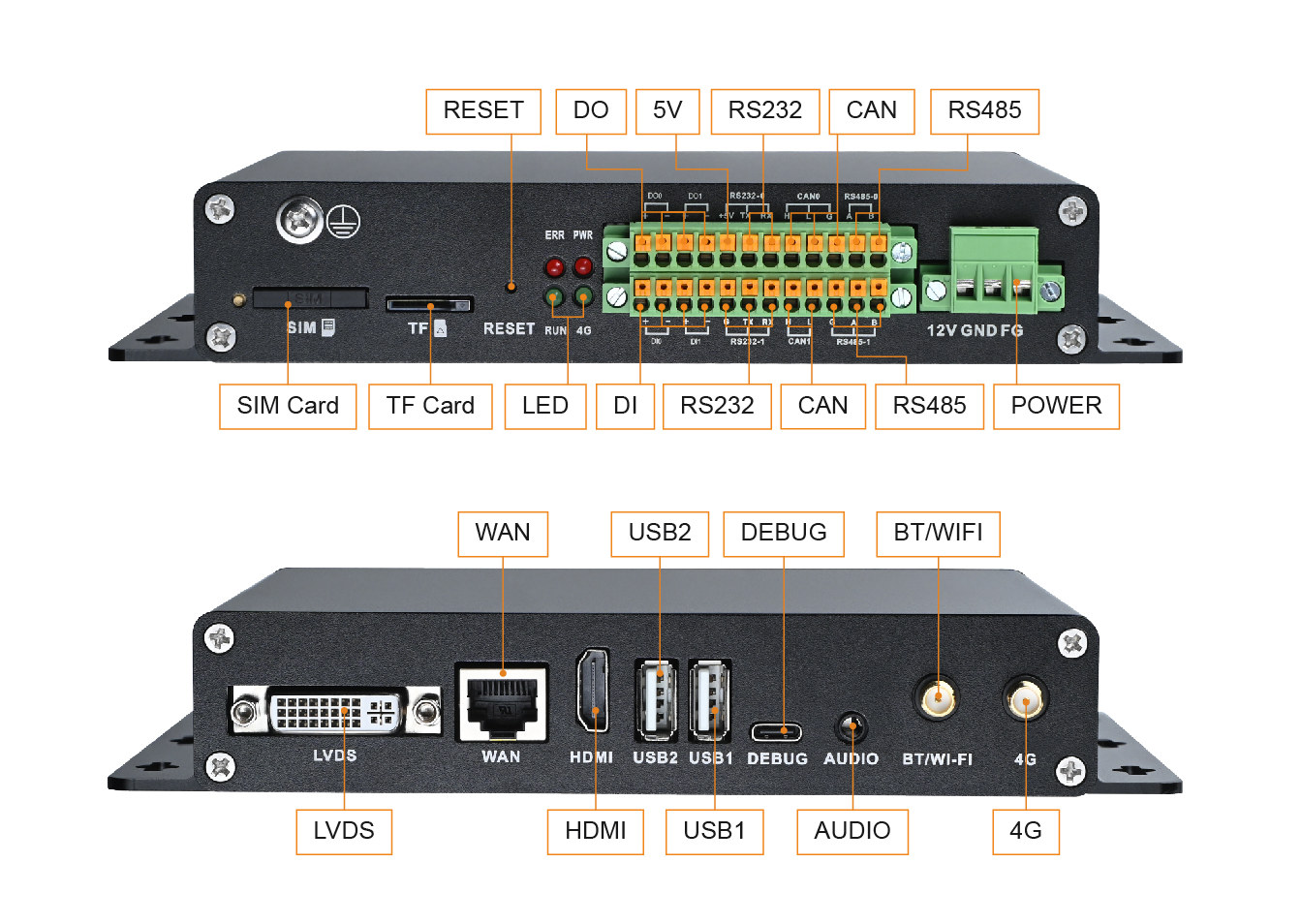

Allwinner T113-i industrial gateway supports Ethernet, WiFi, Bluetooth, 4G LTE, offers RS232, RS485, CAN Bus, DI/DO interfaces

MYiR Tech’s MY-EVC700S-V2 is an industrial gateway powered by Allwinner T113-i dual-core Cortex-A7 microprocessor (MPU), and equipped with up to 512MB DDR3, 4GB eMMC flash, and 32KB EEPROM. The fanless industrial-grade gateway offers RS232, RS485, CAN Bus, DO, and DI through terminal blocks, Fast Ethernet, WiFi, Bluetooth, and 4GB LTE connectivity, HDMI and LVDS display interfaces, a few USB ports, and more. MY-EVC700S-V2 specifications: SoC – Allwinner T113-i CPU Dual-core Arm Cortex-A7 clocked at up to 1.2 GHz 64-bit XuanTie C906 RISC-V real-time core DSP – HiFi4 VPU Video decoder – H.265 up to 4K @ 30 FPS, H.264 up to 4K @ 24 FPS, MPEG-1/2/4, JPEG, Xvid, Sorenson Spark up to 1080p60 Video encoder – JPEG/MJPEG up to 1080p60 Package – LFBGA 337 balls, 13 x 13 mm System Memory – 512MB DDR3 Storage 4GB eMMC flash 32KB EEPROM MicroSD card slot Display Interfaces LVDS-to-HDMI interface (optional) LVDS connector […]

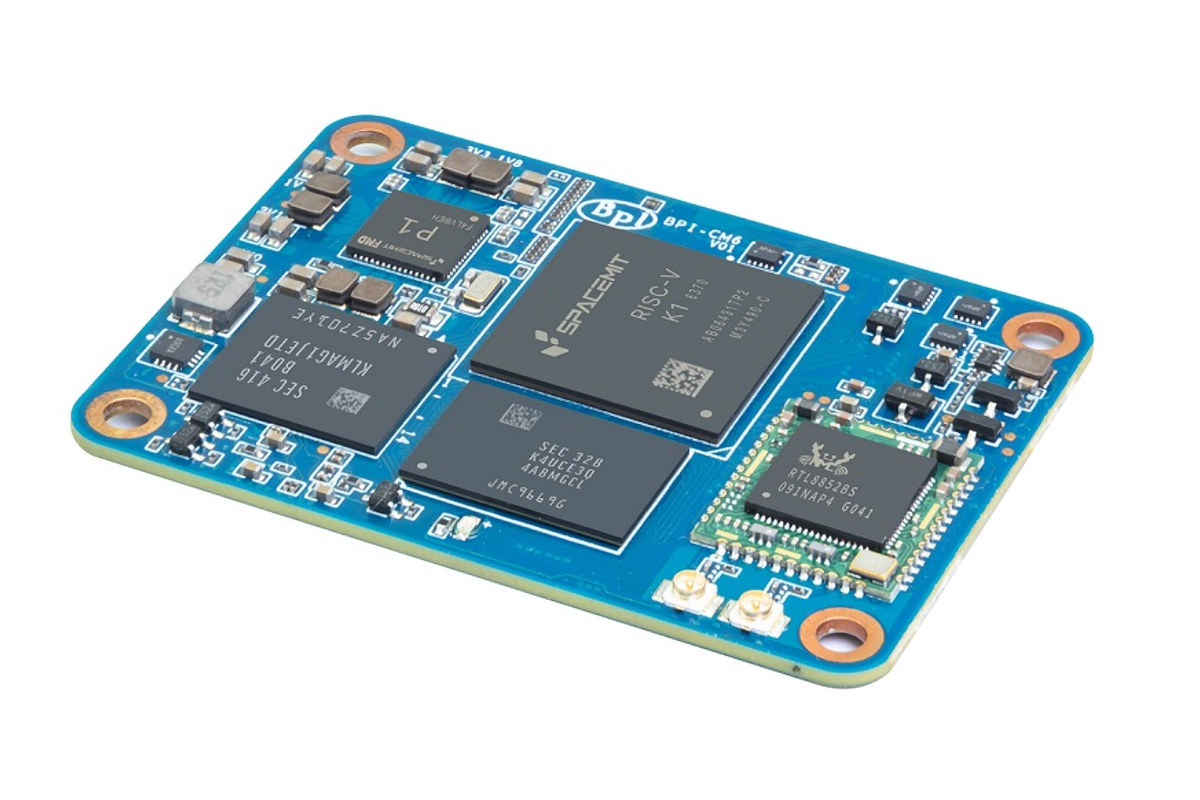

Banana Pi BPI-CM6 is an octa-core RISC-V system-on-module compatible with Raspberry Pi CM5 carrier boards

Banana Pi BPI-CM6 is a SpacemIT K1 octa-core RISC-V system-on-module that follows the design of the Raspberry Pi CM5, and offers up to 16GB LPDDR4 RAM, up to 128GB eMMC flash, a gigabit Ethernet controller, and a WiFi 6 + Bluetooth 5.2 module. While it remains (mostly) compatible with the Raspberry Pi CM5, the BPI-CM6 exposes some additional I/Os from the K1 SoC through an additional 100-pin B2B connector. The company also offers a credit card-sized carrier board for the RISC-V SoM with HDMI, dual GbE, two M.2 PCIe x2 sockets, a few USB ports, and more. Banana Pi BPI-CM6 specifications: SoC – SpacemIT K1 CPU – 8-core X60 RISC-V processor @ 1.6 GHz GPU – Imagination IMG BXE-2-32 @ 819 MHz with support for OpenGL ES3.2, Vulkan 1.3, OpenCL 3.0; 20 GFLOPS VPU – H.265 and H.264 1080p60 decoding/encoding NPU – None, but the RISC-V cores can deliver up […]

Felix86 is an x86-64 emulator for RISC-V hardware

Some programs and most games are designed for x86 hardware, and we’ve already seen projects like box86 x86 emulator for 32-bit Arm targets and Box64 x86-64 emulator for 64-bit Arm hardware to run games on Arm hardware. The Felix86 x86-64 emulator is similar to Box64, except it targets specifically RISC-V hardware. The project is very new, but it can already run some Linux games like World of Goo 2, SuperTuxKart, and Quake OpenArena, while the Wine emulator can currently handle simple Windows games like Solitaire. You’ll find the full compatibility list on the project’s website. Felix86 features: Just-in-Time (JIT) recompiler Uses the RISC-V Vector Extension for SSE instructions Utilizes the B extension, if available, for bit manipulation instructions like bsr Supports a variety of optional extensions, such as XThead custom extensions You’ll find the source code on GitHub. Testing has mostly been done on a Banana Pi BPI-F3 SBC powered […]