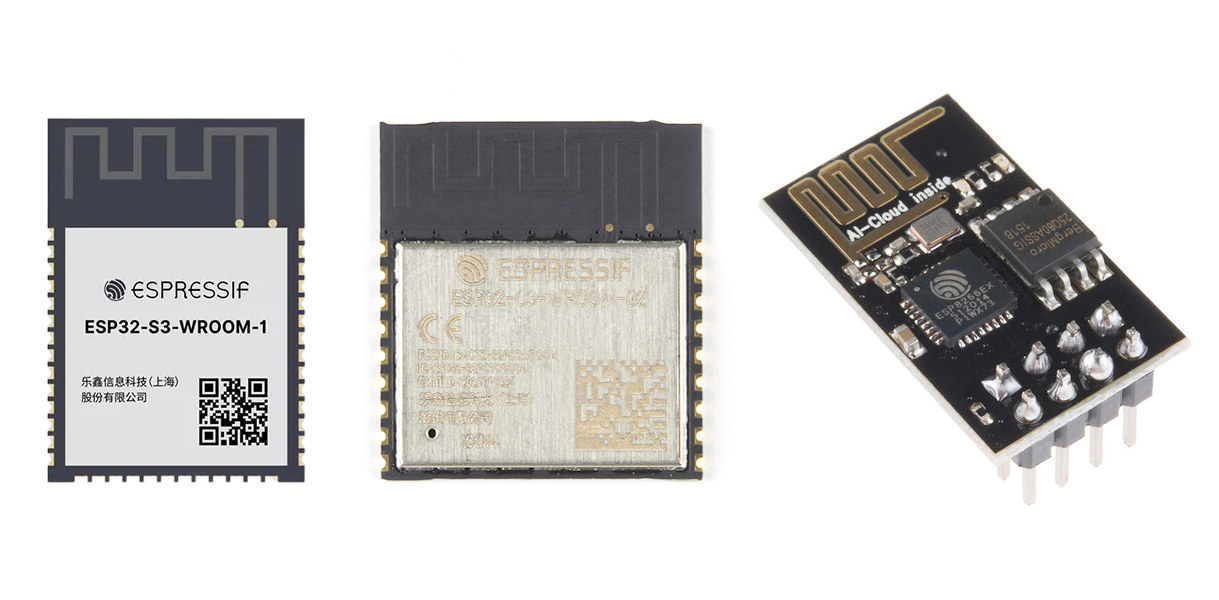

The ESP32-S3 chip is equipped with an Xtensa 32-bit LX7 dual-core processor clocked at up to 240 MHz, supports 2.4 GHz Wi-Fi and Bluetooth 5 LE, and boasts AI instructions, as well as a reliable security encryption engine, specially built for the AIoT market. Modules based on the ESP32-S3 processor bring many benefits to designers with support for Bluetooth Long Range mode, plenty of resources with 512 KB SRAM (TCM), 45 programmable GPIO pins, and rich communication interfaces. They can also handle high-speed Octal SPI flash with higher capacities, as well as off-chip PSRAM. So, what are the differences between the new ESP32-S3 modules, and typical ESP32-C3 and ESP8266 modules? Let’s find out. Jean-Luc Aufranc (CNXSoft)Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011. www.cnx-software.com

Linux 5.16 Release – Main Changes, Arm, RISC-V and MIPS architectures

Linus Torvalds has just announced the release of Linux 5.16: Not a lot here since -rc8, which is not unexpected. We had that extra week due to the holidays, and it’s not like we had lots of last-minute things that needed to be sorted out. So this mainly contains some driver fixes (mainly networking and rdma), a cgroup credential use fix, a few core networking fixes, a couple of last-minute reverts, and some other random noise. The appended shortlog is so small that you might as well scroll through it. This obviously means that the merge window for 5.17 opens tomorrow, and I’m happy to say I already have several pending early pull requests. I wish I had even more, because this merge window is going to be somewhat painful due to unfortunate travel for family reasons. So I’ll be doing most of it on the road on a laptop […]

Intel Mobileye EyeQ Ultra RISC-V processor targets Level 4 autonomous driving

Let’s carry on with Intel’s CES 2022 news, but with a twist as Mobileye EyeQ Ultra does not include any x86 cores, but instead, the automotive processor features 12 RISC-V cores, Arm GPU and DSP, and aims to bring Level 4 autonomous driving to cars thanks notably to a 176 TOPS AI accelerator. The company says EyeQ Ultra packs the performance of 10 EyeQ5s in a single package, with the single chip solution avoiding the power consumption and costs related to integrating multiple SoCs together. Intel Mobileye EyeQ Ultra specifications highlights: CPU – 12 RISC-V CPU cores (24 threads) GPU – Unnamed Arm GPU DSP – Unnamed Arm DSP SIMD cores VLIW cores Coarse grained reconfigurable array (CGRA) cores CNN accelerator clusters Two sensing subsystems One camera-only system Radar and Lidar combined system 5-nanometer process technology Mobileye provides both the chip and software with for instance high-definition map and […]

Year 2021 in review – Top 10 posts and statistics

As per tradition, we’ll look back at what happened during the year in the last post, and see what 2022 may have in store, plus the usual statistics from CNX Software website. The biggest story of 2021 has to be the worsening of semiconductors shortages with extremely long lead times, prices of some components going up multiple folds, constant complaints on Twitter about availability and prices. I think I even saw a website, hopefully misconfigured, showing an estimated availability of a specific STM32 MCU in 2037. This also gave rise to opportunities and board redesigns, with MotorComm Ethernet chips replacing some Realtek chips in SBCs such as NanoPi R2C and Orange Pi R1S Plus LTS, and CH9102F showing up as a replacement for CP2104 in some IoT boards. We also got some interesting Arm processors, but sadly the high-expected Rockchip RK3588 got delayed by another year, although it’s getting really […]

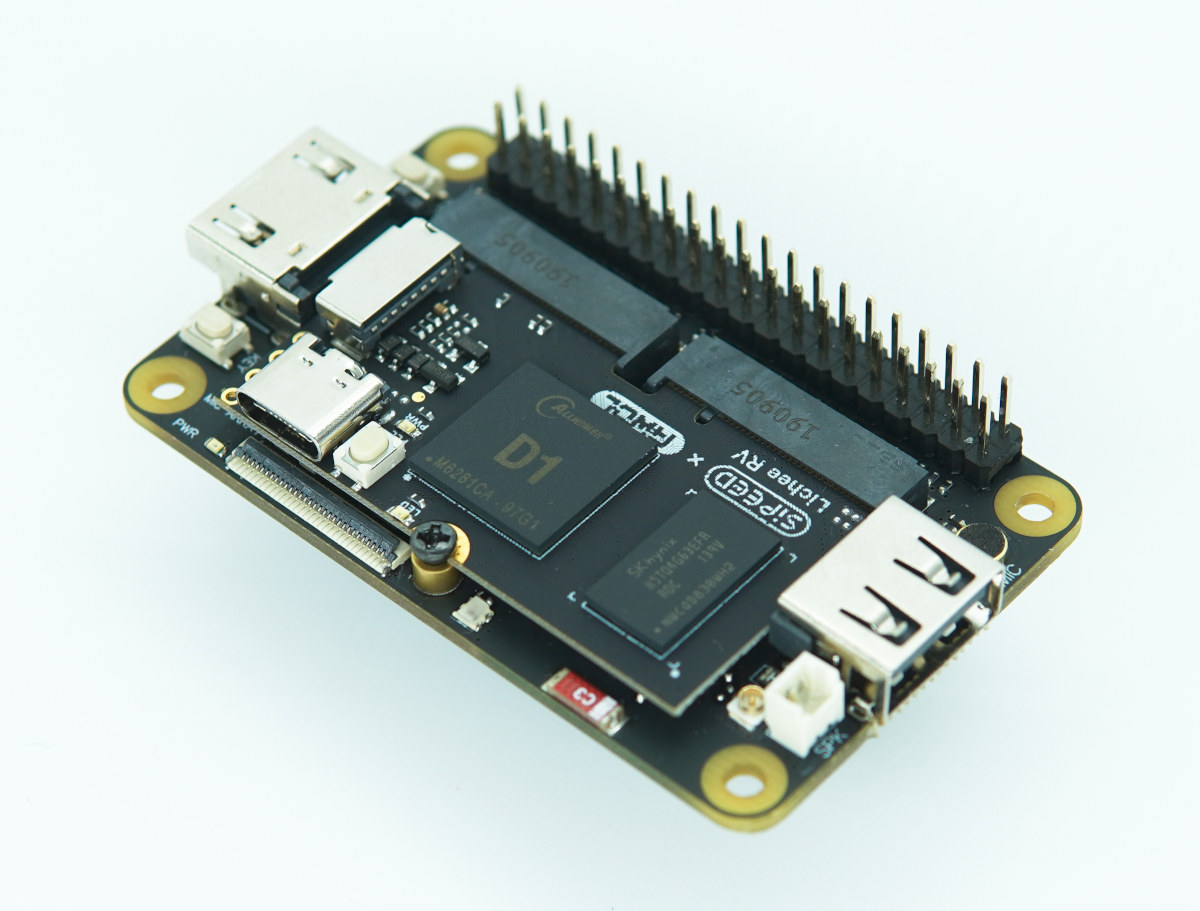

Sipeed Lichee RV RISC-V module gets $5+ carrier board with HDMI and USB ports, optional WiFi

Sipeed introduced the Lichee RV Allwinner D1 Linux RISC-V board going for just $17 with 512MB RAM last month. While with a USB-C port it could be used as a standalone part, its dual M.2 connector makes it more like a module and we noted a tiny carrier board was in the works at the time. The baseboard is now available and known as the Lichee RV Dock adding HDMI and USB ports, as well as a 40-pin GPIO header for just $5, or $8 if you’d like to get Wi-Fi 4 and Bluetooth 4.2 connectivity through a Realtek RTL8723DS module. Sipeed Lichee RV Dock specifications: Supported system-on-module (SoM) – Lichee RV module with Allwinner D1 RISC-V processor @ 1 GHz, 512MB DDR3, MicroSD card slot, and USB Type-C OTG port Storage – Optional SPI flash Display interfaces HDMI port up to 4Kp30 Optional RGB interface for up to 720p30 […]

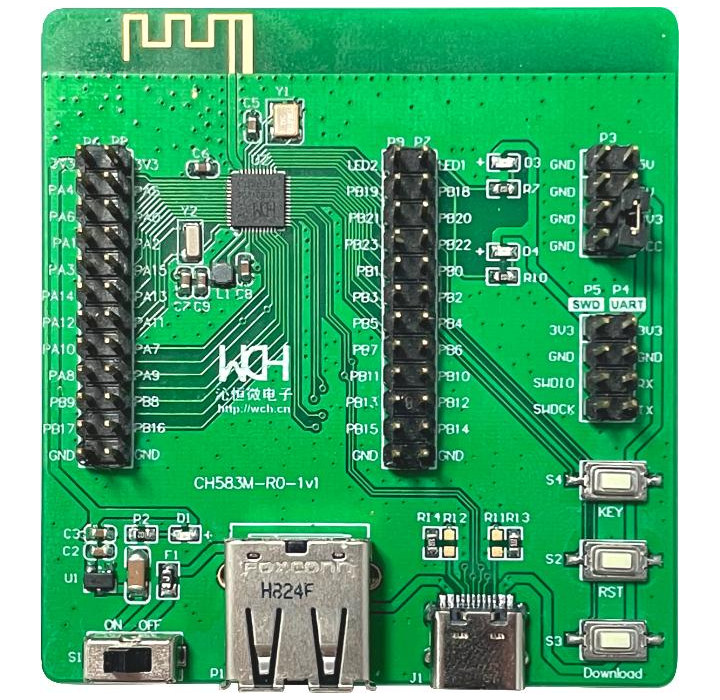

CH583 RISC-V microcontroller supports Bluetooth 5.3 LE

Following up on the CH572 RISC-V BLE microcontroller with 10KB SRAM, WCH has now introduced the CH583 RISC-V microcontroller with 32KB SRAM, 1 MB flash, and support for the latest Bluetooth 5.3 LE standard. The new microcontroller also offers a wide range of peripherals with two USB host/device interfaces, up to 40 GPIOs, four UART, two SPI, one I2C, up to 14 ADC interfaces, and more. WCH also offers CH581 and CH582 microcontrollers with a different minimum input voltage, less storage (256KB for CH581) and/or peripherals. CH581, CH582, CH583 specifications: MCU core – 32-bit RISC processor WCH RISC-V4A with RV32IMAC instruction set Memory – 32 KB SRAM Storage – 512KB non-volatile storage FlashROM: 448KB user application program memory area CodeFlash 32KB user non-volatile data memory area DataFlash 24KB system boot program memory area BootLoader 8KB system non-volatile configuration information memory area InfoFlash BLE Connectivity Bluetooth Low Energy (BLE) v5.3 Integrated […]

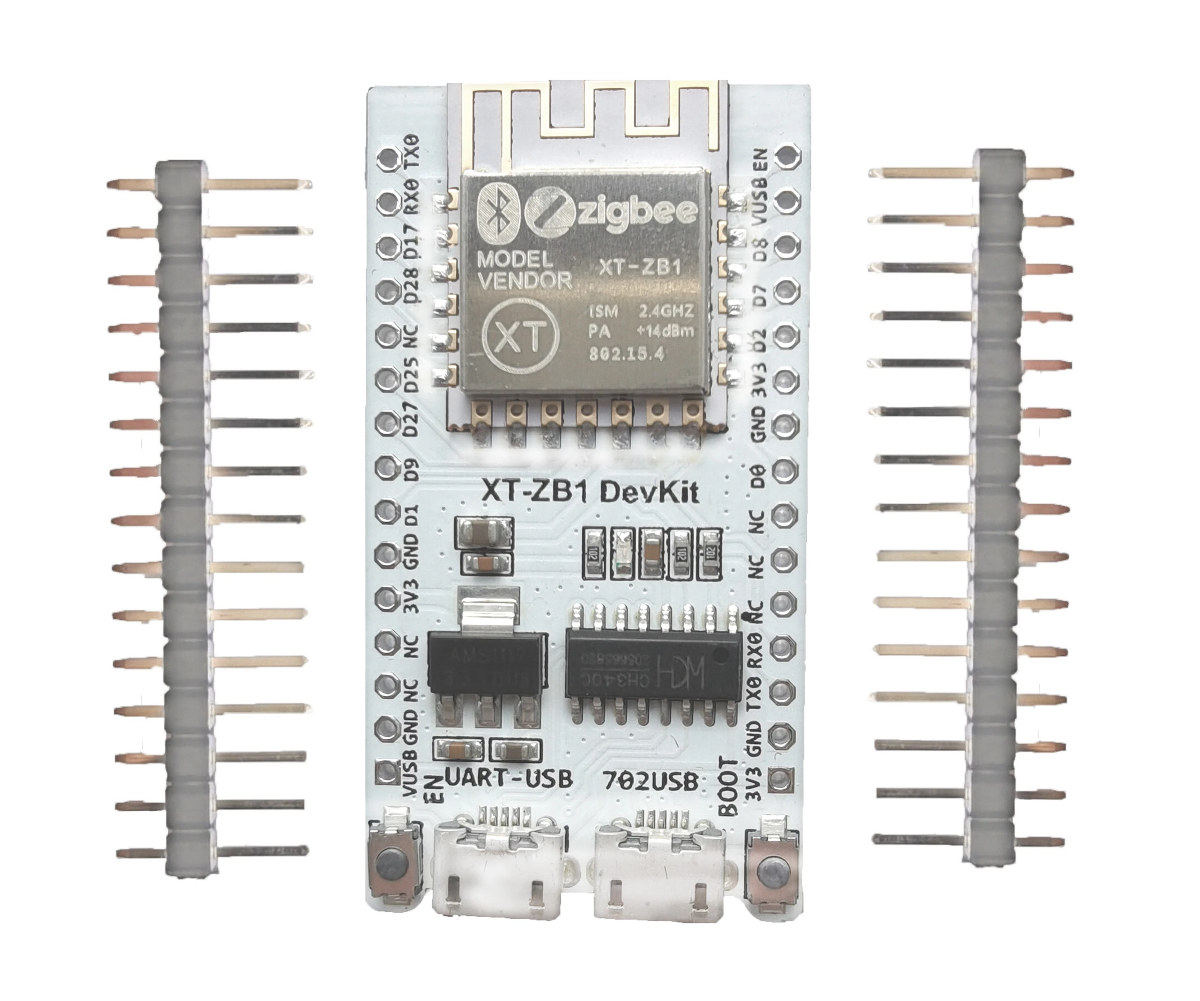

$1.8 XT-ZB1 Zigbee & BLE devkit features BL702 RISC-V module

Bouffalo Labs BL702 is a 32-bit RISC-V microcontroller with a 2.4 GHz radio for Zigbee 3.0 and Bluetooth 5.0 LE connectivity that we first found in the Sipeed RV-Debugger Plus UART & JTAG debug board that did not make use of the radio at all. But a BL702 development kit was brought to my attention, with the XT-ZB1 devkit equipped with a Zigbee & BLE module of the same name, and sold for just $1.80 per unit on Aliexpress. Shipping adds $4.63 where I live, but they also offer packs of 5 or 10 with the same shipping fee, meaning if you buy 10 the total cost should be around $22 including shipping, or around $2.2 per board. Alternatively, the module alone goes for $1. XT-ZB1 devkit specifications: XT-ZB1 wireless module with MCU – BL702C 32-bit RISC-V microcontroller @ 144 MHz with FPU, 132KB RAM, 192KB ROM, 1Kbit eFuse Storage […]

HUENIT modular robot arm takes 3D printer, laser engraver, suction, AI camera modules (Crowdfunding)

Most robot arms are designed to carry and manipulate payloads, but HUENIT modular robot arm is much more versatile as besides a traditional suction module, the robot supports modules such as a 3D printer, laser engraver, pen holder for drawings, and a creator module for let people designed their own. The robot arm can hold payloads of up to 750 grams, have a reach of up to 39 cm without module, supports WiFi and Bluetooth connectivity, and can also optionally be fitted with a 2MP AI camera module based on Kendryte K210 RISC-V processor with built-in AI accelerators. HUENIT specifications: Robot arm 4-axis Payload up to 750 grams Reach – 390mm without module Repeatability – 0.05mm Precision – 0.1mm Speed – Up to 500mm/s Storage – MicroSD card slot USB – 1x USB-C port Wireless – WiFI and Bluetooth Misc – UART, external stepper Power Supply – 24V DC input, […]