Microchip recently unveiled the PIC64HX1000 64-bit RISC-V AI microprocessor (MPU) family designed for mission-critical intelligent edge applications in the aerospace, defense, industrial, and medical sectors thanks to a quantum-resistant design. These new MPUs feature eight SiFive’s Intelligence X280 cores, each clocked at 1 GHz. The MPUs are engineered with a decoupled vector pipeline enabling 512-bit operations enabling the PIC64HX1000 to achieve up to 2 TOPS for AI/ML processing and come equipped with integrated Time-Sensitive Networking (TSN) Ethernet connectivity. This new microprocessor includes a dedicated system controller for runtime monitoring and fault management, WorldGuard architecture for workload isolation, and post-quantum defense-grade cryptography, which includes the NIST-standardized FIPS 203 and FIPS 204 cryptographic algorithms, ensuring protection against future quantum computing threats. PIC64HX1000 64-bit AI MPU specification MPU variants PIC64HX1000 – IN (Industrial) PIC64HX1000 – AV (Aviation) PIC64HX1000 – MI (Military) CPU – 8x 64-bit RISC-V cores (SiFive X280), up to 1 GHz, […]

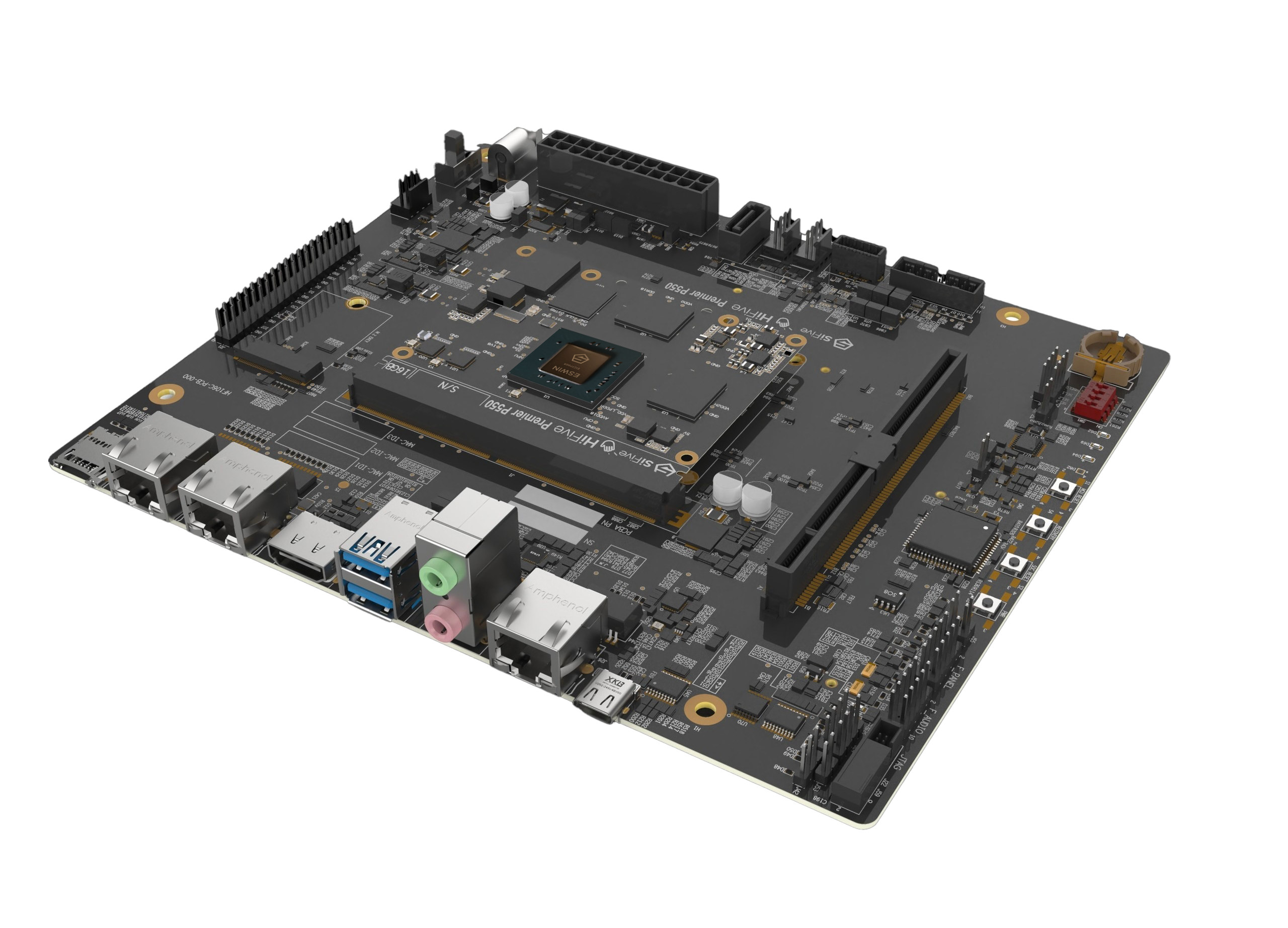

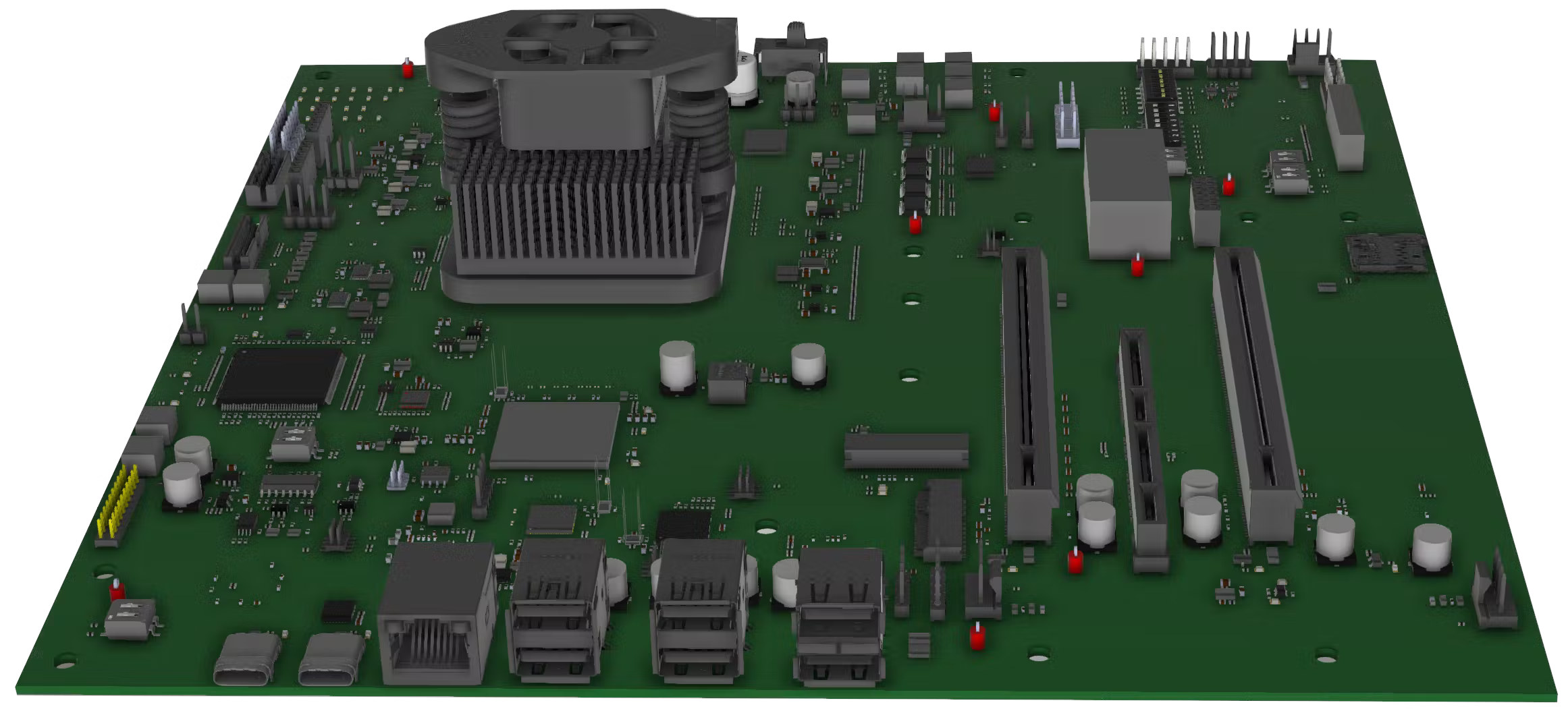

HiFive Premier P550 mini-DTX motherboard features ESWIN EIC7700X RISC-V AI SoC, up to 32GB DDR5, a PCIe x16 slot

SiFive HiFive Premier P550 is a mini-DTX (203 x 170mm) motherboard powered by a 1.4 GHz ESWIN EIC7700X quad-core RISC-V SiFive P550 SoC with up to 19.95 TOPS of AI performance, and equipped with up to 32GB LPDDR5 memory and a 128GB eMMC flash all soldered on a system-on-module. The motherboard itself features a SATA III connector for data storage, includes an HDMI 2.0 port for 4K video output, a PCIe Gen3 x16 slot (working at x4), two gigabit Ethernet ports, an M.2 Key-E socket to add a WiFi/Bluetooth card, up to five USB interfaces, and more. HiFive Premier P550 specifications: SoC – ESWIN EIC7700X CPU 4x SiFive Performance P550 RV64GC RISC-V cores @ 1.4GHz (up to 1.8GHz when overclocked) with Cortex-A75-class performance 32KB(I) + 32KB(D) L1 Cache 256KB L2 Cache 4MB shared L3 Cache Cache supports ECC (support SECDED) NPU (Not currently supported in software) – Up to 19.95 […]

Microchip PIC64GX is a quad-core 64-bit RISC-V microprocessor for real-time processing

Microchip has introduced its first 64-bit RISC-V microprocessor family with the PIC64GX pin-to-pin compatible with the company’s PolarFire SoC FPGA devices and designed for edge designs for the industrial, automotive, communications, IoT, aerospace, and defense segments. The PIC6GX MPU supports asymmetric multiprocessing (AMP) to run Linux, real-time operating systems, and bare metal in a single processor cluster with secure boot capabilities. The company further claims the PIC64GX MPU is “the first RISC-V multi-core solution that is AMP capable for mixed-criticality systems”. The first member of the PIC64GX RISC-V family is the PIC64GX1000 microprocessor. Microchip PIC64GX1000 specifications: CPU Quad-core SiFive U54 64-bit five-stage, single-issue, in-order pipeline RISC-V (RV64GC) processor at up to 625 MHz with AMP and deterministic latencies, PMP and MMU units Single-core SiFive E51 64-bit RISC-V (RV64IMAC) monitor processor core at up to 625 MHZ with PMP unit Cache L1 memory subsystem with Single-Error Correct, Double-Error Detect (SECDED) Flexible […]

SiFive announces Essential Gen4 RISC-V CPUs for embedded applications

As the RISC-V Summit Europe 2024 is underway, SiFive has announced the fourth generation of its “Essential” RISC-V CPUs (Essential Gen4) with improved power efficiency and more flexible interfaces for SoCs used in embedded devices. The update covers 32-bit and 64-bit RISC-V cores including the U6 and U7-series 64-bit application processors, the S2, S6, and S7 64-bit real-time embedded processors, and the E2, E6, and E7 32-bit real-time embedded processors. Essential Gen4 IP keys features: Up to 40% runtime power reduction 8x different baseline embedded 32-bit and 64-bit cores From 2-stage single-issue to 8-stage superscalar Improved L2 cache and enhanced L1 memory Configuration and integration options CPU type, profile, and options On-chip memories selection System, peripheral, and front ports Advanced power management and security Debug and trace Software support includes embedded Linux and FreeRTOS operating systems and Eclipse-based IDE for C/C++ development. That’s another low-quality, light-on technical details announcement from […]

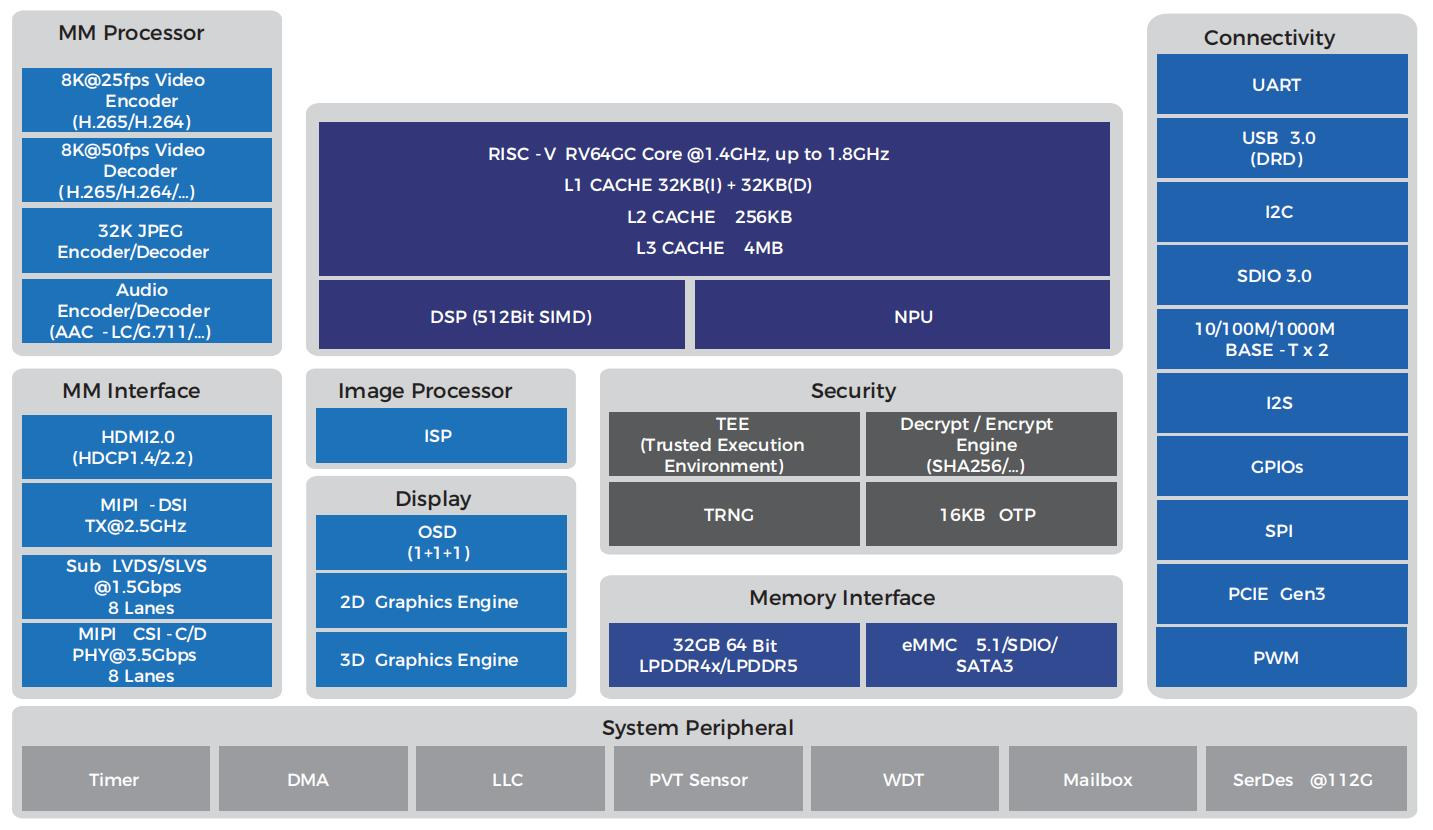

ESWIN EIC7700X quad-core RISC-V SoC embeds 19.95 TOPS NPU for Edge AI vision applications

Yesterday we noted Sipeed was working on the LM5A system-on-module powered by ESWIN EIC7700X quad-core RISC-V processor with a ~20 TOPS AI accelerator in order to integrate it into its Lichee Book laptop and other carrier boards. So today, I’ve decided to look into the EIC7700X SoC designed by “BEIJING ESWIN COMPUTING TECHNOLOGY CO., LTD”, or ESWIN for shorts. The EIC770X features four 64-bit RISC-V (RV64GC) cores clocked up to 1.8 GHz, an Imagination AXM-8-256 3D GPU, a 19.95 TOPS NPU, H.265/H.264 video encoder/decoder capable of handling up to 32x 1080p30 videos, various video output (HDMI + DSI) and input interfaces, dual GbE, 4-lane PCIe Gen 3, and more. ESWIN EIC7700X specifications: CPU 4x SiFive Performance P550 RV64GC RISC-V cores @ 1.4GHz (up to 1.8GHz) with Cortex-A75-class performance 32KB(I) + 32KB(D) L1 Cache 256KB L2 Cache 4MB shared L3 Cache Cache supports ECC (support SECDED) DNN Accelerator – 19.95 TOPS […]

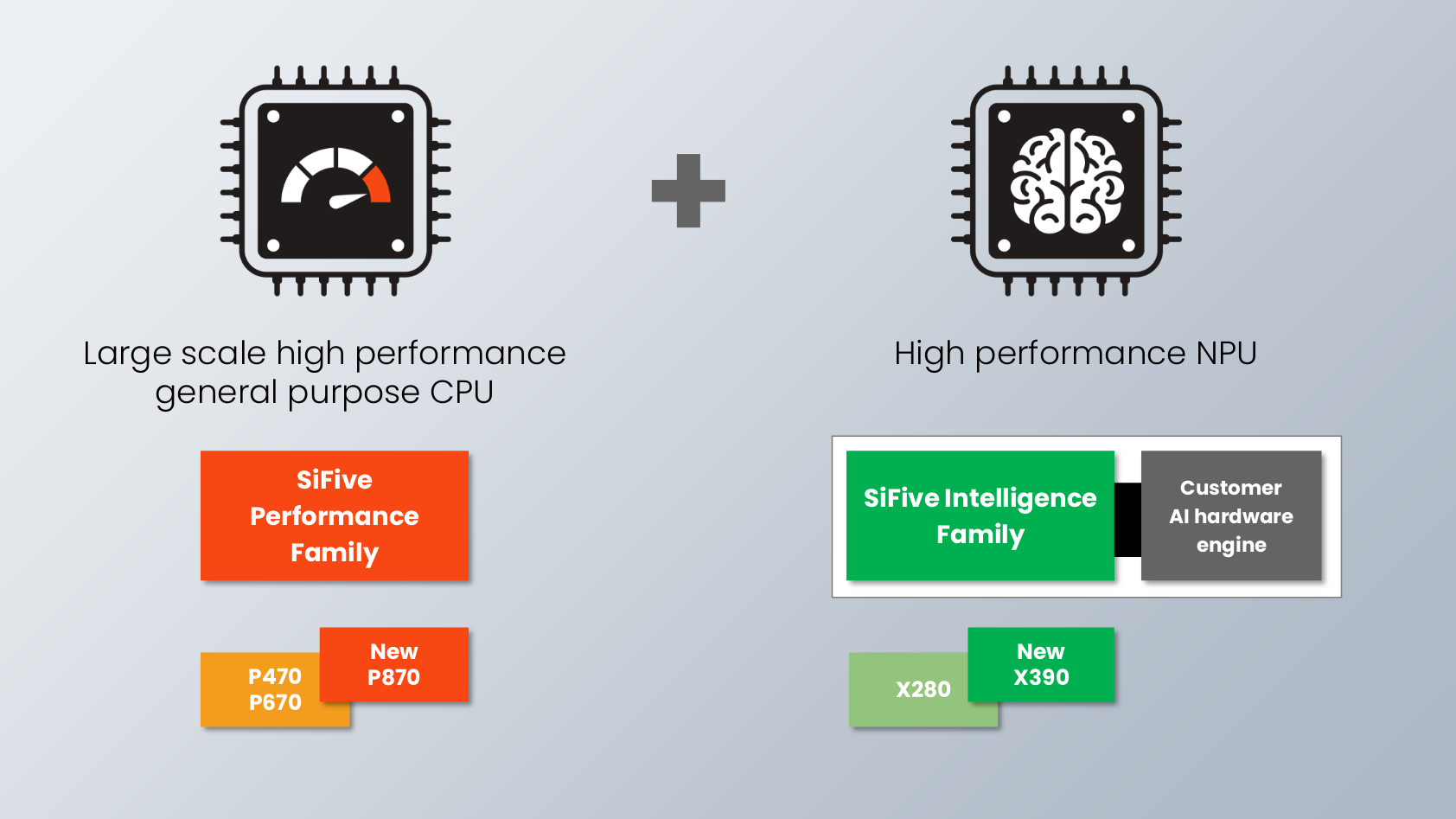

SiFive announces Intelligence X390 NPU, Performance P870 RISC-V core

SiFive has announced two new high-performance IP blocks with the Intelligence X390 NPU and the Performance P870 RISC-V core that should find their way into SoC designed for Generative AI and ML applications. We had already covered the Performance P870 and its automotive sibling – the P870-A – from information in an earlier presentation, but the SiFive Intelligence X390 NPU is new to me and appears to be aimed at generative AI in data centers, although we will very soon be seeing companies implement generative AI at the edge in pretty powerful embedded devices. SiFive Performance P870 highlights: Full support for the RVA23 RISC-V profile specification and Vector 1.0 and Vector Crypto Six-wide, out-of-order 64-bit core Up to a 32-core cluster >12 SpecINT2k6/GHz, or a 50% peak single thread performance upgrade over the previous generation SiFive Performance P670 SiFive Features 2x 128b VLEN RVV Vector crypto and hypervisor extensions IOMMU […]

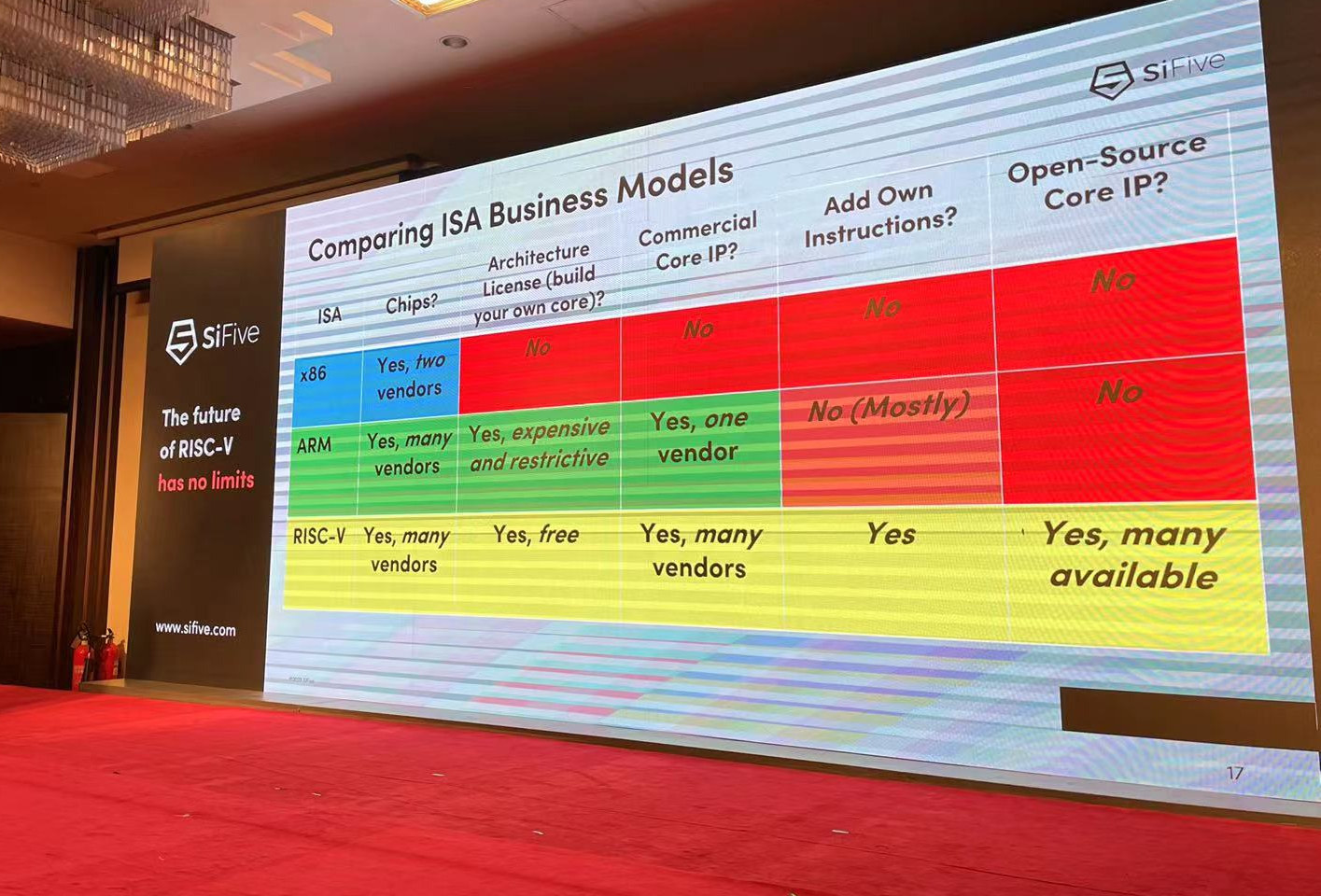

SiFive unveils P870 high-performance core, discusses future of RISC-V

SiFive has just given a presentation at Hot Chips 2023 introducing the new high-performance P870 RISC-V core and its automotive equivalent the P870-A core, plus discussing RISC-V in general, its previous generation RISC-V cores, and what to expect going forward. SiFive has not officially announced the P870 and P870-A cores just yet, so most of the information we have from the English-speaking Internet is from ServeTheHome who managed to get some presentation slides, but this is also corroborated by various Chinese sources on Baidu and Guokr. SiFive P870 and P870-A The P870 and P870-A RISC-V cores are new cores from the SiFive Performance family compatible with the RISC-V RVA23 profile and succeeding the SiFive P670 core. The SpecINT2k6 benchmark reports 17 points per GHz on the P870 compared to 13.2 points per GHz for the P670 (comparable to the Arm Cortex-A78) or about a 29% higher performance at the same […]

HiFive Pro P550 “Horse Creek” RISC-V motherboard with 16GB RAM to launch this summer

SiFive HiFive Pro P550 RISC-V motherboard based on Intel “Horse Creek” quad-core SiFive Performance P550 processor will launch this summer with 16GB DDR5 memory, two PCIe expansion slots, Gigabit Ethernet networking, USB 3.x ports, and on-board graphics. Intel Horse Creek platform was first revealed when SiFive unveiled the SiFive Performance P550 64-bit RISC-core with Cortex-A75 class performance in June 2021. The companies then demonstrated an internal Intel Horse Creek board with 8GB DDR5 and PCIe Gen5 at the Intel Innovation 2022 Developer Conference last October, and it looks like the 7nm RISC-V processor, manufactured with an Intel 4 process, will finally be available to developers this summer with the launch of the HiFive Pro P550 motherboard/development system. HiFive Pro P550 preliminary specifications: SoC – Intel-SiFive Horse Creek SoC equipped with 4x SiFive Performance P550 RV64GBC RISC-V cores with a 13-stage, 3-issue, out-of-order (OoO) pipeline GPU – “On-board graphics” [Update: […]