If you have been working on open standard RISC-V ISA CPU cores, there is a high chance that you have come across WARP-V. For newbies, WARP-V is a RISC-V CPU core generator written in TL-Verilog (Transaction-Level Verilog) that supports not only RISC-V but also MIPS ISA. WARP-V has been in discussion for a while due to its unparalleled architectural scalability in a small amount of code.

The famous proverb “Necessity is the mother of invention” applies to the invention of TL-Verilog and with that this WARP-V CPU core generator. For decades, hundreds of engineers have been working on designing a single CPU core that was more complex in the race to achieve higher single-core performance. But with recent developments in the semiconductor industry, developer and engineer Steve Hoover, with decades of experience in designing CPU cores, has come up with the idea of developing a WARP-V core in just 1.5 weeks with no advanced CPU microarchitectural techniques used.

One important question that comes to our mind is why another HDL, TL-Verilog, when we have Verilog and VHDL. (Spoiler: TL-Verilog is not a Hardware Description Language). There are several reasons for it, like designing the CPU to be concise, flexible, and explicit. With TL-Verilog, the code size is reduced by almost half for 1-to-7 cycles pipeline depth compared to the one cycle design in SystemVerilog. This happens because the TL-Verilog models are half the size of their Verilog equivalent. When we look at other HDLs, they operate more into the description of the static designs, but this was not the concept behind TL-Verilog as it is built for the design process, hence a Hardware Design Language.

What is a WARP-V CPU Core Generator?

Coming back to the WARP-V core, in terms of flexibility of the core, it can implement a single-stage CPU like a microcontroller or even a seven-stage general-purpose processor. Being an open-source project, you can now use small source code to make it suitable for your application. The WARP-V CPU core features only CPU core implementations without virtual memory, cache, and I/Os. With customizable ISA, you can now add on optional RISC-V extensions, like the base integer instruction set (E), standard extension for integer multiplication and division (M), single-precision floating-point (F), and bit manipulation (B).

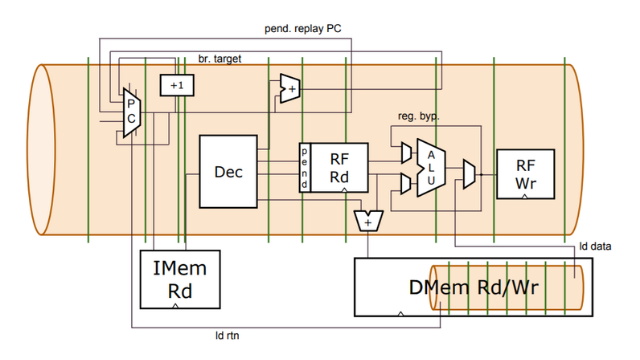

When we look at the CPU design microarchitecture of WARP-V, we can note that each vertical green line separates the virtual pipeline stages. All these virtual pipeline stages can be mapped to a single physical stage or different physical stages. Since it is a RISC-V implementation, the decode, branch target calculation, and register are mapped to the same physical stage. The code is developed through the use of a macro preprocessor M4, with which you can take the generated code as the source code and tweak the microarchitecture.

But when we talk about the flexibility of the core, to satisfy this, there also has to be flexible verification modeling. As an open-source project, it gives a chance to many contributors to work and understand the level of integration in designing the core. At GSoC (Google Summer of Code) 2018, a master’s student at TU Delft, Ákos Hadnagy, along with Steve Hoover, presented TL-Verilog’s use and flexibility benefits for verification modeling.

What’s next with WARP-V?

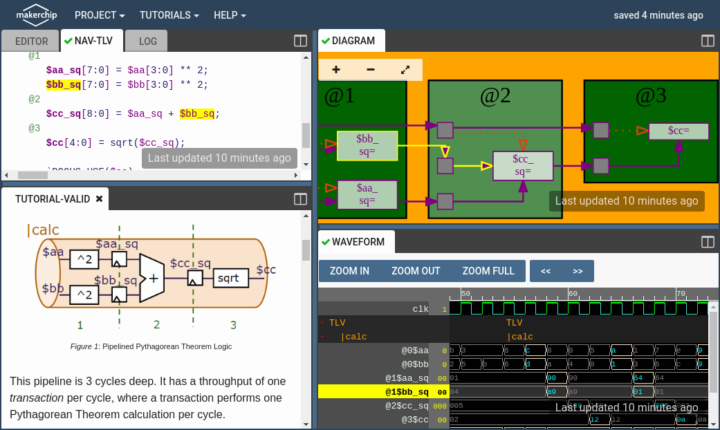

Before we talk about the future developments with WARP-V, let us first understand how to get started with this CPU core generator. To configure WARP-V, you can modify the parameter with the command line while compiling and debugging using the IDE in Makerchip. Assuming you have gone through the tutorials on TL-Verilog and Makerchip, you choose, compile, and work on the model in the “NAV-TLV” window. More details on getting started can be found on the official GitHub repository.

Even if WARP-V is not necessarily the best option, it is a way towards democratizing the CPUs. There may not be a lot that can be done around WARP-V, but you can surely work on other associated workloads like making it multicore to show the transaction flow or maybe even work on TL-Chisel. The designer, Steve Hoover quotes, “RISC-V has liberated the ISA. Now it’s time to liberate CPUs and other components. Save the patents for bigger things.”

Abhishek Jadhav is an engineering student, RISC-V Ambassador, freelance tech writer, and leader of the Open Hardware Developer Community.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress