Intel has recently launched the Intel Xeon D (Ice Lake-D) processor family with the D-2700 and the D-1700 models designed for software-defined network and edge applications with integrated AI and crypto acceleration, built-in Ethernet, support for Intel Time Coordinated Computing (TCC) and Time-Sensitive Networking (TSN), plus high reliability. The new processors are bringing data center-class hardware to the edge, and at least two embedded systems companies, namely ADLINK Technology and Congatec, have already launched COM-HPC server modules and COM Express Type 7 module based on the new Intel Xeon D family. Intel Xeon D processors Intel Xeon D-2700 and Intel Xeon D-1700 are designed for space- and power-constrained ruggedized environments, feature industrial-class reliability, hardware-based security, and up to 56 high-speed PCIe lanes to support networks with up to 100Gbps Ethernet. While the Intel Xeon D-1700 sub-family is scalable from 2 to 10 cores, the Intel Xeon D-2700 family goes up […]

Allwinner T113-S3 dual-core Cortex-A7 SoC features 128MB DDR3, targets automotive and industrial applications

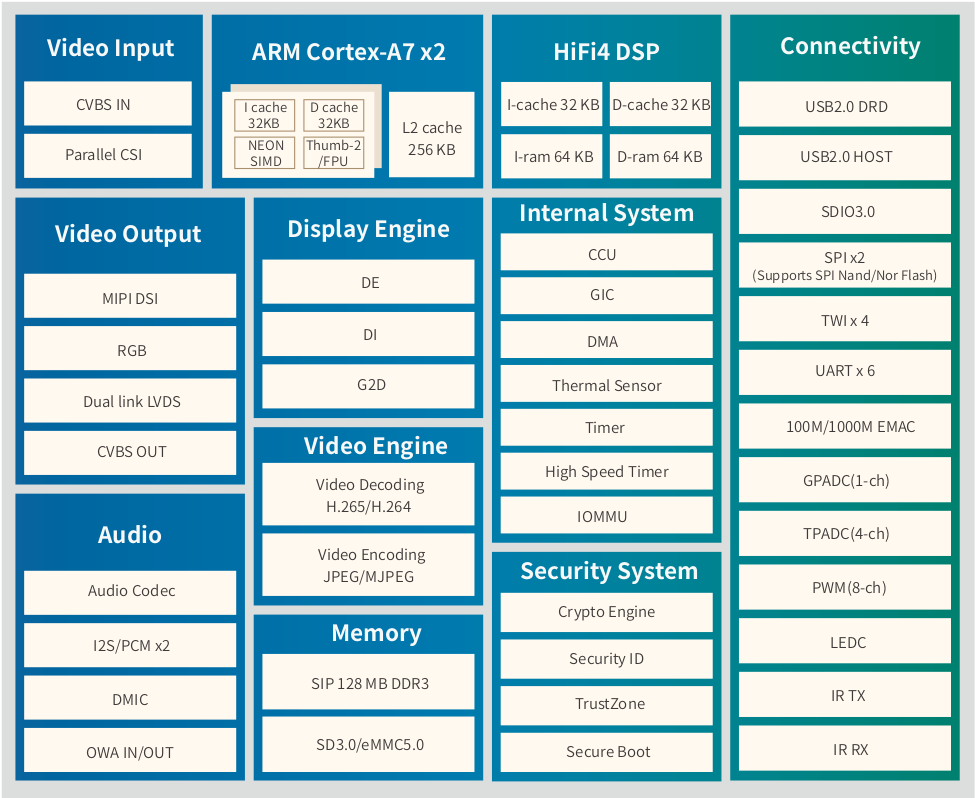

Allwinner T113-S3 is a dual-core Cortex-A7 processor with 128MB DDR3 on-chip memory that is designed for smart control and HMI applications in the automotive and industrial sectors. At first glance, the new processor looks quite similar to Allwinner S3, but with twice the number of cores. However there’s more to it, as a a HiFi4 DSP has been added for smart audio applications, the H.264 encoder is gone replaced by an MPJEG encoder, and the company claims support for “industrial level working temperature”, plus a 10-year life cycle. among other differences. Allwinner T113-S3 specifications: CPU – Dual-core Arm Cortex-A7 with 32 KB L1 I-cache + 32 KB L1 D-cache per core, and 256 KB L2 cache DSP – Single-core HiFi4 Memory – 128 MB DDR3 Storage I/F – SD3.0/eMMC 5.0, SPI Nor/NAND Flash Video Decoding – H.264, H.265, MPEG-1/2/4, (M)JPEG, VC1 up to 1080p60 Encoding – JPEG/MJPEG up to 1080p60 […]

MIPI CSI-2 v4.0 adds features for always-on, low power machine vision applications

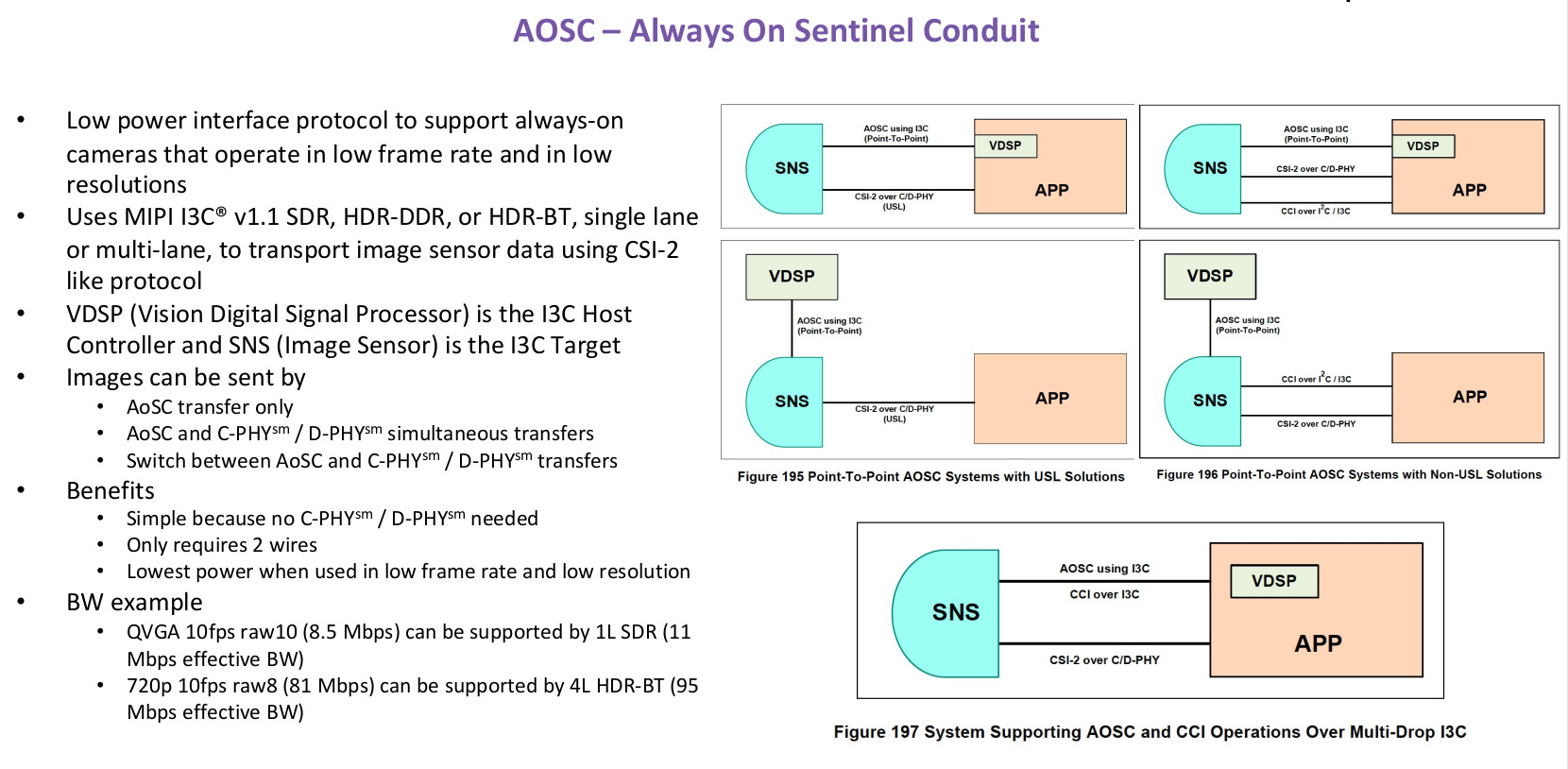

While MIPI CSI-2 standard was first introduced in 2005 as a high-speed protocol for the transmission of still and video images from image sensors to application processors, the standard has evolved over the years, and the latest MIPI CSI-2 v4.0 introduces features to better support always-on, low power machine vision applications, high-resolution sensors, and high-dynamic-range automotive image sensors. The main changes for v4.0 include support for a two-wire interface (MIPI I3C) to lower cost and complexity, multi-pixel compression for the latest generation of advanced image sensors, and RAW28 color depth for better image quality and an improved signal-to-noise (SNR) ratio. MIPI CSI-2 v4.0 highlights: Always-On Sentinel Conduit (AOSC) – Enables always-on machine vision systems with ultra-low-power image sensors and video signal processors (VSPs) continuously monitoring their surrounding environments and having the ability to wake up their more powerful host CPUs when specific events happen. Some use cases include laptop/tablet-based face […]

Lantronix G520 cellular gateways target industrial communication, cybersecurity, and transportation

Lantronix G520-series 4G LTE Cat 4 and 5G cellular gateways are designed to address challenges in Industry 4.0, security, and transportation markets with three/four separate gateways all based on an unnamed ARM926EJ-S-based CPU running at 600 MHz that’s most likely Microchip SAM9X60 processor introduced in 2020. All gateways are from the same base with variation for specific markets: G526 Industrial Gateway with LTE Cat 4 Ethernet, Serial, I/O, Fieldbus conversion, and other industrial protocols G527/G528 Security Gateway with LTE Cat 13 or 5G, built-in cryptographic secure element and PSE-PoE G528 Transportation Gateway (coming soon) with LTE Cat 4, GNSS, accelerometer, CAN Bus reading, and other tracking features Lantronix G520-series specifications: SoC – ARM926EJ-S-based processor running at 600 MHz with 32 KB instruction cache and 32KB data cache System Memory – 256MB DDR2 SDRAM Storage – 8MB SPI flash for OS, 256MB parallel NAND flash, MicroSD slot, or USB flash drive […]

FOSDEM 2022 schedule with embedded Linux, IoT, automotive… sessions

While typically taking place in Brussels, Belgium, FOSDEM 2022 will take place online just like FOSDEM 2021 due to COVID-19 restrictions. The good news is that it means anybody can attend it live from anywhere in the world, and makes it more like “FOSDIM”, replacing European with International, in “Free and Open Source Developers’ European Meeting”. FOSDEM 2022 will take place on February 5-6 with 637 speakers, 718 events, and 103 tracks. I’ve made my own little virtual schedule below mostly with sessions from the Embedded, Mobile and Automotive devroom, but also other devrooms including “Computer Aided Modeling and Design”, “FOSS on Mobile Devices”, “Libre-Open VLSI and FPGA”, and others. Saturday, February 5, 2022 12:30 – 13:00 – Five mysteries in Embedded Linux by Josef Holzmayr Once you start out in embedded Linux, there is a lot to do. Some things are obvious, some less so. First and foremost, […]

Linux 5.16 Release – Main Changes, Arm, RISC-V and MIPS architectures

Linus Torvalds has just announced the release of Linux 5.16: Not a lot here since -rc8, which is not unexpected. We had that extra week due to the holidays, and it’s not like we had lots of last-minute things that needed to be sorted out. So this mainly contains some driver fixes (mainly networking and rdma), a cgroup credential use fix, a few core networking fixes, a couple of last-minute reverts, and some other random noise. The appended shortlog is so small that you might as well scroll through it. This obviously means that the merge window for 5.17 opens tomorrow, and I’m happy to say I already have several pending early pull requests. I wish I had even more, because this merge window is going to be somewhat painful due to unfortunate travel for family reasons. So I’ll be doing most of it on the road on a laptop […]

Horizon X3 AI development board is powered by Sunrise 3 AI Edge Arm processor

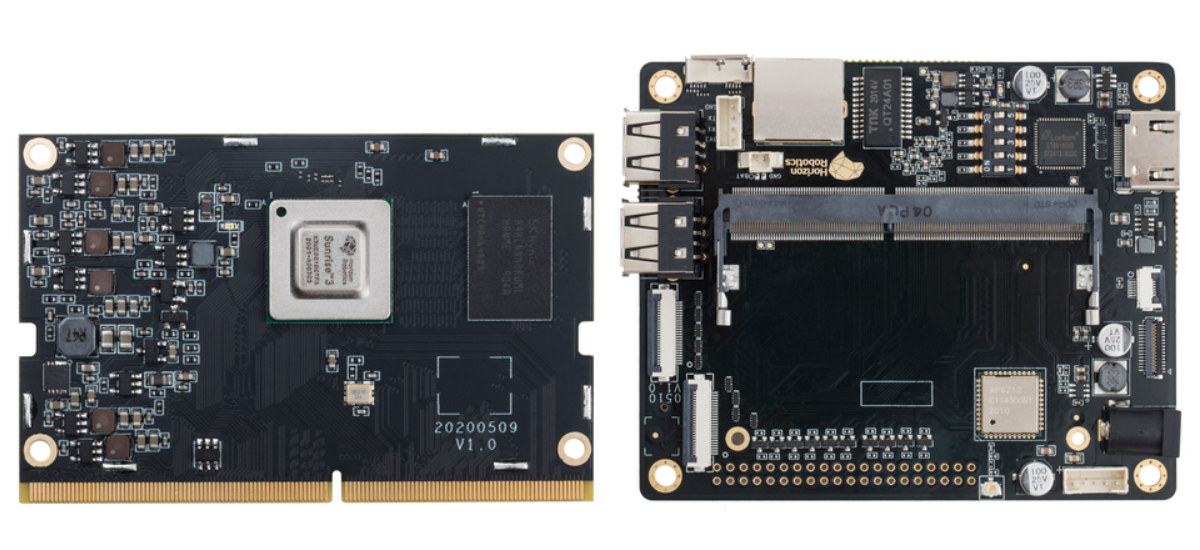

Horizon X3 AI development board is powered by Horizon Robotics Sunrise 3 (aka X3) quad-core Cortex-A53 processor with a 5 TOPS NPU, and multiple camera support with the chip apparently designed for the automotive industry. [Update January 25, 2022: A third-party company, Finsbury Glover Hering, claiming to represent Horizon Robotics informed CNX Software the chip is not designed for the automotive market, and that Horizon’s AIoT business is actually limited to the domestic China market and not overseas.] The devkit is comprised of a Sunrise 3 system-on-module with 1GB LPDDR4 & 16GB EMMC memory, as well as a baseboard with Gigabit Ethernet and WiFi, HDMI up to 1080p60 and MIPI DSI interface, a camera interface, and a 40-pin header for expansion. Horizon X3 AI development board specifications: SoC – Horizon Robotics Sunrise 3 quad-core Cortex-A53 processor @ 1.2 GHz, one Cortex-R5 core, a 5 TOPS NPU (2x “Bernoulli” BPU) System […]

Intel Mobileye EyeQ Ultra RISC-V processor targets Level 4 autonomous driving

Let’s carry on with Intel’s CES 2022 news, but with a twist as Mobileye EyeQ Ultra does not include any x86 cores, but instead, the automotive processor features 12 RISC-V cores, Arm GPU and DSP, and aims to bring Level 4 autonomous driving to cars thanks notably to a 176 TOPS AI accelerator. The company says EyeQ Ultra packs the performance of 10 EyeQ5s in a single package, with the single chip solution avoiding the power consumption and costs related to integrating multiple SoCs together. Intel Mobileye EyeQ Ultra specifications highlights: CPU – 12 RISC-V CPU cores (24 threads) GPU – Unnamed Arm GPU DSP – Unnamed Arm DSP SIMD cores VLIW cores Coarse grained reconfigurable array (CGRA) cores CNN accelerator clusters Two sensing subsystems One camera-only system Radar and Lidar combined system 5-nanometer process technology Mobileye provides both the chip and software with for instance high-definition map and […]