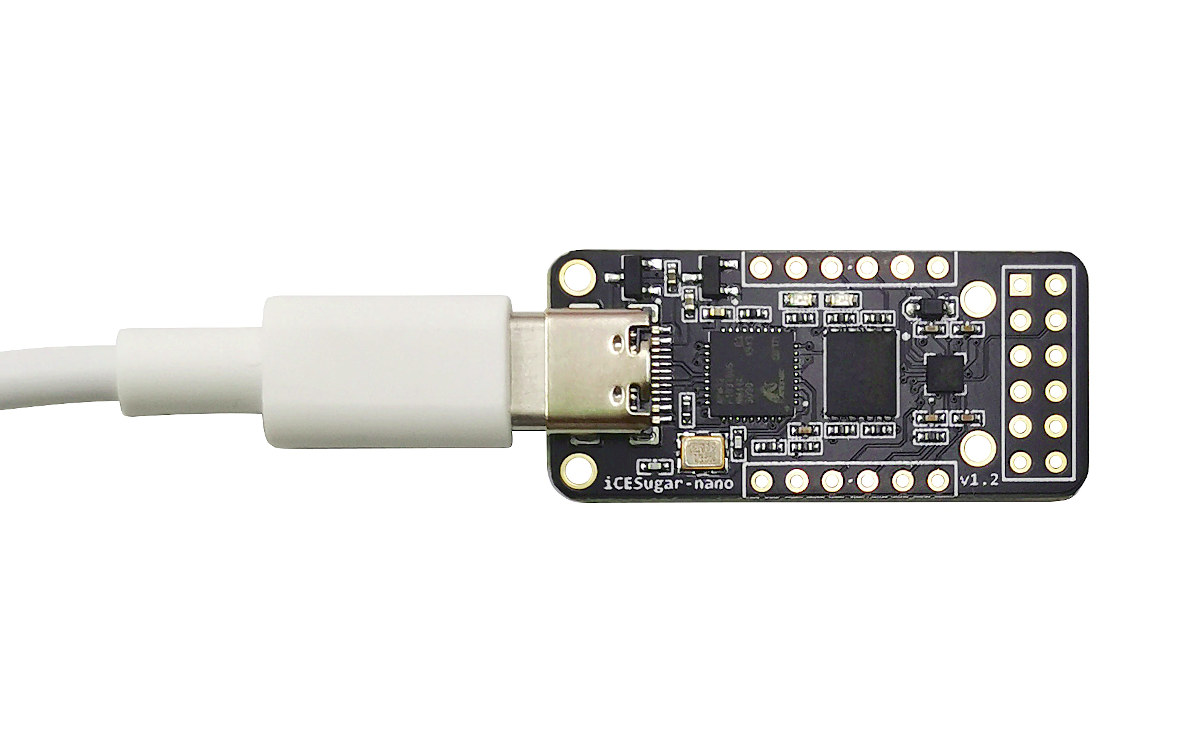

Muse Lab’s iCESugar-nano is a tiny FPGA board based on Lattice Semi iCE40LP1K-CM36 programmable via its USB-C port through on-board iCELink debugger, and exposing I/Os for three standard PMOD connectors. The board is fully supported by Yosys open-source toolchain ( Yosys+ nextpnr + IceStorm), and the onboard debugger supports drag-and-drop programming so that you can just drag the FPGA bitstream into the virtual disk to program it through a USB Type-C cable. iCESugar-nano specifications: FPGA – Lattice Semi iCE40LP1k FPGA with 1280 LUT/8KB SRAM/PLL Storage – 2MB SPI flash (W25Q16) USB – 1x USB Type-C port for power and programming Expansion – 14x usable IOs with 1x 12-pin PMOD connectors and 2x 6-pin PMOD connectors Debugging – On-board iCELink debugger based on Arm Mbed DAPLink Misc – Adjustable clock (8/12/36/72MHz), LED Power Supply – 5V via USB-C port Dimensions – 3.9 x 1.8 cm Documentation, schematic PDF, links to tools, […]

ZUBoard 1CG – A low-cost AMD Xilinx Zynq UltraScale+ ZU1CG MPSoC FPGA development board

Avnet ZUBoard 1CG is a development board featuring the new entry-level AMD Xilinx Zynq UltraScale+ ZU1CG dual-core Cortex-A53 MPSoC with 81K FPGA system logic cells, equipped with 1GB LPDDR4 RAM, as well as SYZYGY connectors and mikroBus expansion for Click boards. Priced at $159, the board may offer a good opportunity to get started with Zynq UltraScale+ MPSoC, as it’s quite cheaper than boards based on ZU3 devices such as Ultra96-V2 or MYD-CZU3EG. Avnet says the board is suitable for artificial intelligence, machine learning, embedded vision, embedded processing, and robotics applications. ZUBoard 1CG specifications: SoC – AMD/Xilinx ZU+ MPSoC ZU1CG with Dual Cortex-A53 APU @ up to 1.3 GHz and dual Cortex-R5 RPU @ up to 533 MHz 256KB On-chip Memory 81,900 FPGA Logic Cells System Memory – 1GB LPDDR4 with on-chip ECC Storage – 256Mbit QSPI flash, microSD card, both bootable Networking – 10/100/1000M Gigabit Ethernet RJ45 port USB […]

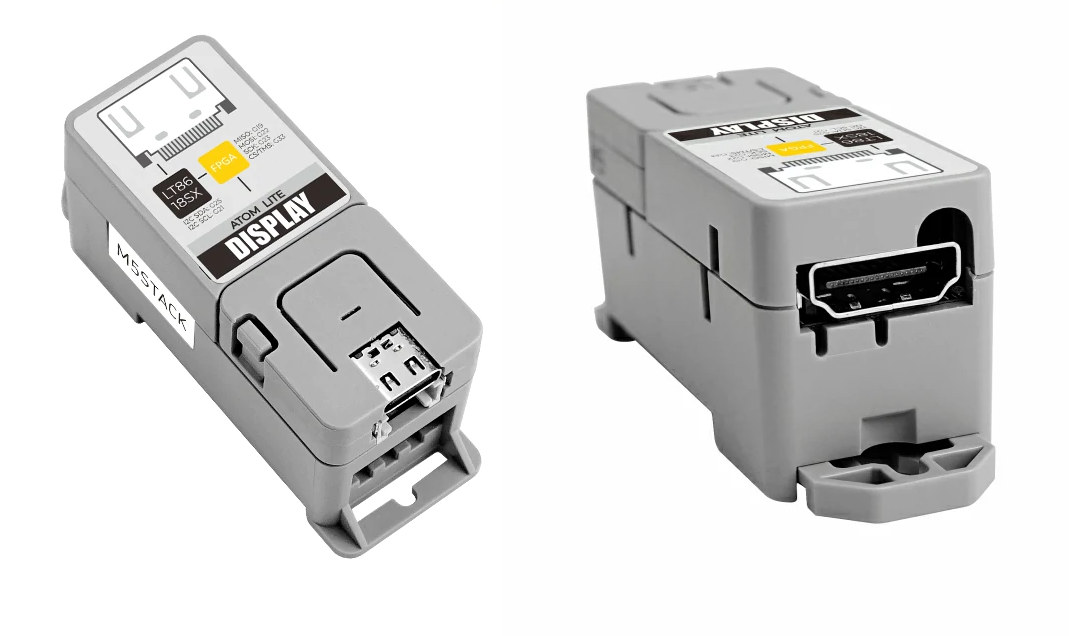

M5Stack ATOM Display Lite adds HDMI output to ESP32 module

M5Stack ATOM Display Lite is a kit based on GOWIN Gowin GW1NR-9C FPGA and LT8618SX RGB to HDMI chip designed to add HDMI output up to 720p to the company’s ESP32-based M5Stack ATOM Lite module. The ATOM Lite sees the ATOM Display Lite kit as an SPI display, but the solution outputs the data to an HDMI monitor or TV with up to 1280×720 resolution and can be used for information display, menu board, and more. ATOM Display Lite specifications: Wireless IoT modules – M5Stack ATOM Lite ESP32-PICO-D4 based module with 240MHz dual-core CPU, 520KB SRAM, 4MB flash, Wi-Fi 4 and Bluetooth connectivity FPGA – Gowin GW1NR-9C (PDF datasheet) FPGA with 8,640 LUTs used to simulate SPI TFT-LCD data output, HDMI bridge – Lontium Semi LT8618SX RGB to HDMI chip with 24-bit color depth up to 1280×720 output @ 60 fps (optimized frame rate up to 12 ~ 16FPS) Misc- […]

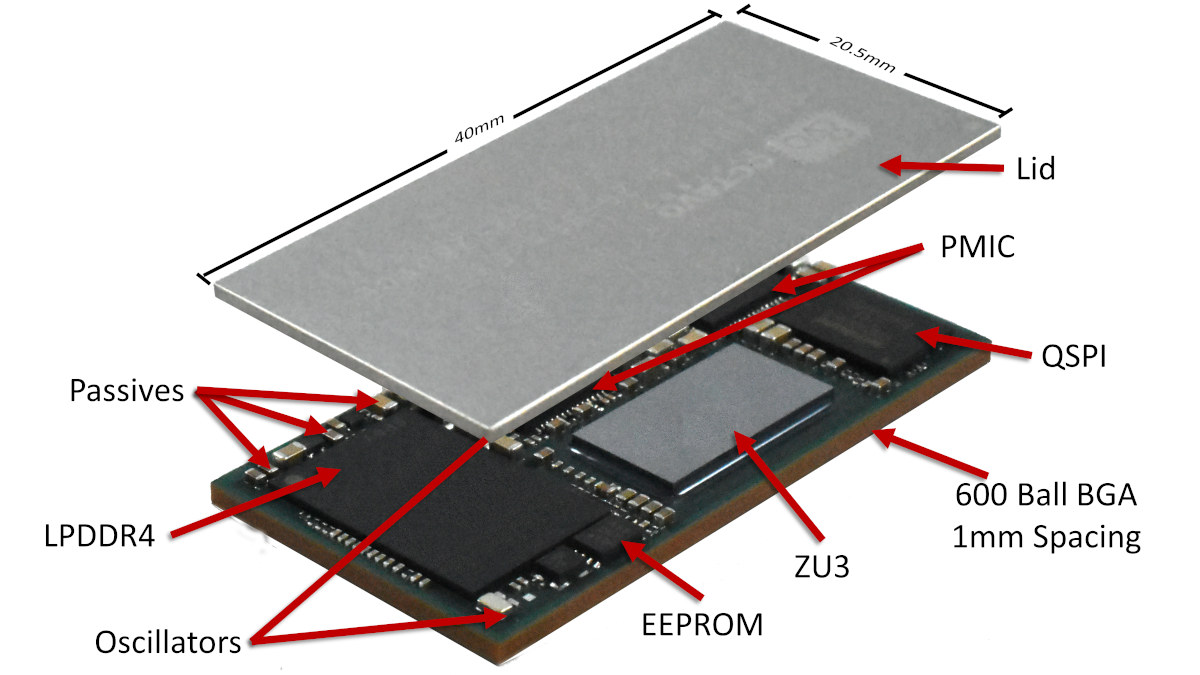

OSZU3 System-in-Package (SiP) combines AMD Xilinx Zynq UltraScale+ MPSoC with 2GB RAM, PMIC, passive components

Octavo Systems has collaborated with AMD Xilinx for the OSZU3 system-in-package (SiP) that combines Zynq UltraScale+ MPSoC ZU3 with up to 2GB RAM, power management circuitry, and other components into a compact (40×20.5mm) 600-ball BGA package. We’ve already written about other Octavo Systems SiPs in the past with solutions like OSD3358x (TI Sitara AM3358) and OSD32MP15x (STMicro STM32MP1), but the OSZU3 packs a much more powerful and flexible chip with the AMD Xilinx Zynq UltraScale+ MPSoC offering both Cortex-A53 & Cortex-R5F cores, Arm Mali-400 GPU, and FPGA fabric. Octavo Systems OSZU3 SiP specifications: SoC – AMD Xilinx Zynq UltraScale+ MPSoC ZU3 with CPU – 4x Arm Cortex-A53 up to 1.2GHz, 2x Arm Cortex-R5F up to 500MHz GPU – Arm Mali-400 FPGA 154K System Logic Cells 141K Flip-Flops 71K CLB LUTs 360 DSP Slices 7.6 Mb Block RAM System Memory – 2GB LPDDR4 Storage – 128MB SQPI, and 4K EEPROM (by […]

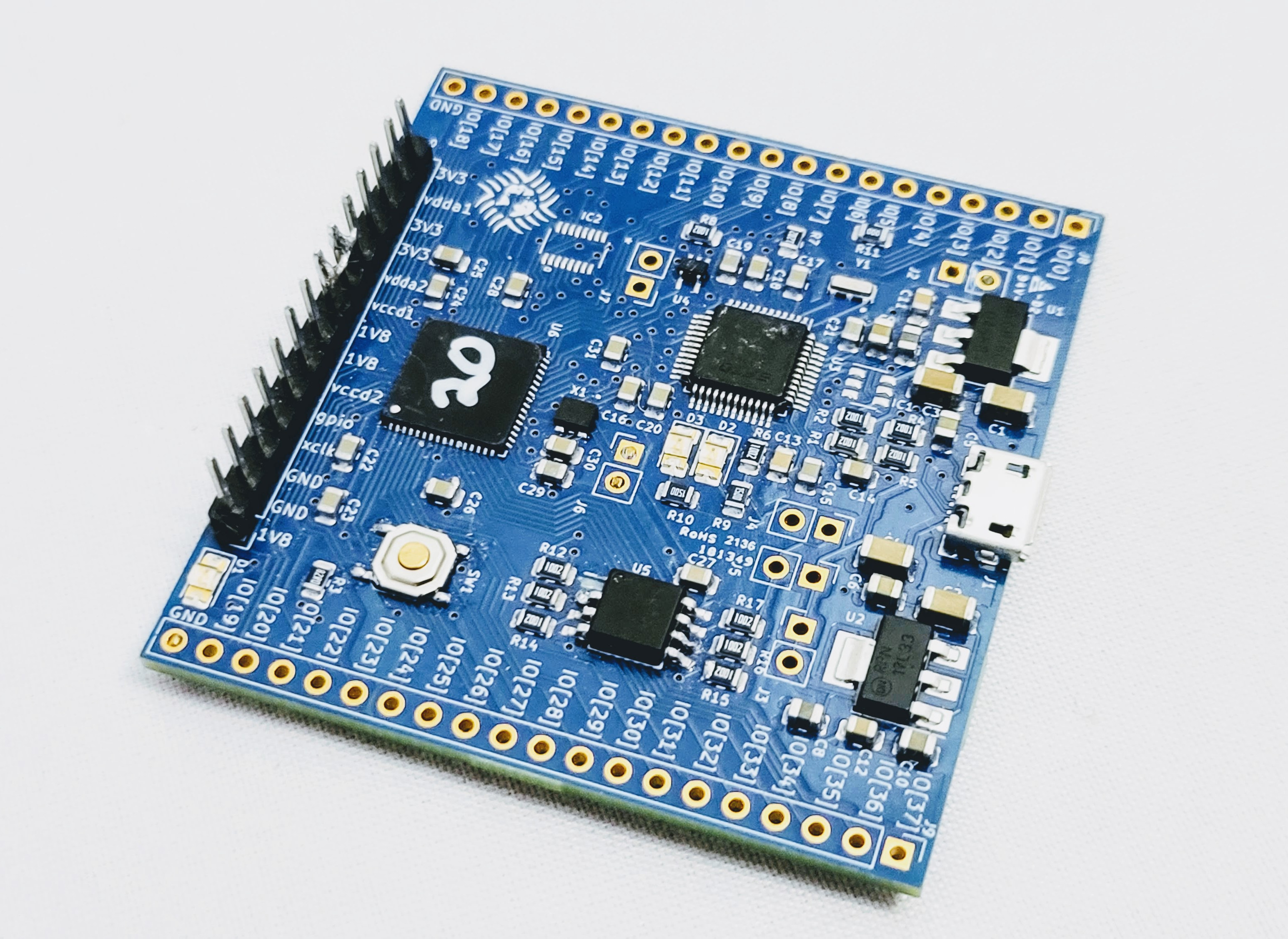

Silicon Witchery S1 module combines nRF52811 Bluetooth SoC with Lattice iCE40 FPGA

Sweden-based Silicon Witchery S1 is a tiny module combining Nordic Semi nRF52811 Bluetooth LE SoC with Lattice Semi iCE40 FPGA designed for battery-powered applications leveraging DSP and machine learning (ML) at the edge. The S1 module features just four key components in a tiny 11.5 x 6 mm form factor and targets applications requiring “demanding” algorithms while consuming as little energy as possible. Silicon Witchery S1 module specifications: MCU – Nordic Semi nRF52811 Arm Cortex-M4 MCU @ 64 MHz with Bluetooth 5.2 support including Long Range, Thread support. FPGA – Lattice Semi iCE40 FPGA with 5k LUT and DSP blocks. Storage – 32 Mbit flash storage. Integrated antenna, passives, and crystals. I/Os – 20x castellated holes with 8x FPGA IO include I3C, I2C, SPI, and USB. 2x nRF GPIO pins with ADC and low power wake. SWD pins for debugging Power Supply Lithium battery charging and monitoring. 3x adjustable Vout […]

CLEAR is an open-source FPGA ASIC provided by Efabless’ chipIgnite

Open-source SoC designs are available to run on FPGA hardware, but few make it to silicon due to the costs involved. That’s why a couple of years ago the Google SkyWater PDK (process design kit) was released together with an offer to manufacture up to 100 pieces for free to selected designs in collaboration with Efabless. Efabless chipIgnite is an evolution of that offer with $9,750 being enough funds to manufacture 100 QFN or 300 WCSP parts, or alternatively 1,000 parts for $20 each ($20,000). Based on the company’s Caravel template SoC and the openFPGA generator framework, CLEAR open-source FPGA ASIC design is meant to promote and demonstrate the chipIgnite “paid IC creation” solution. You can participate by joining a group buying campaign on GroupGets to get a development board based on CLEAR for $74.99 plus shipping. CLEAR open-source FPGA ASIC features: FPGA – Small 8×8 (64) CLB eFPGA CPU […]

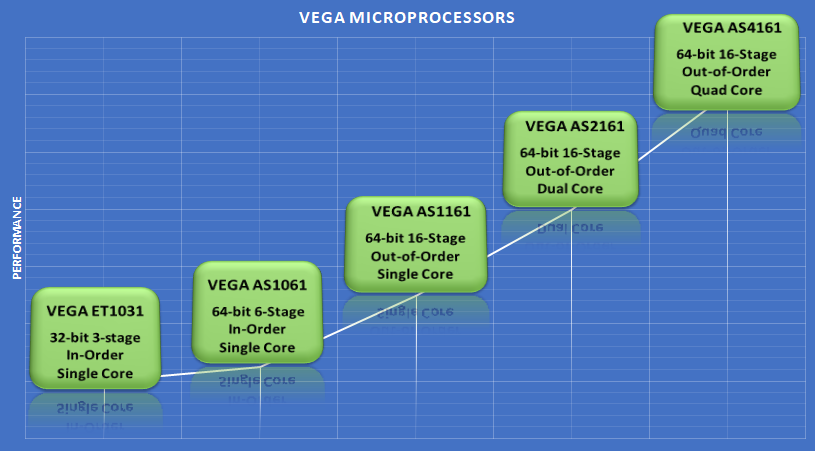

India goes RISC-V with VEGA processors

One of the main advantages of RISC-V architecture is that it is open, so any organization with the right skills can develop its own cores, and India’s government has taken up this opportunity with the Microprocessor Development Programme (MDP) helping develop VEGA RISC-V cores locally. Thanks to funding by the Ministry of Electronics and Information Technology (MeitY), the Centre for Development of Advanced Computing (C-DAC) managed to design five RISC-V processors ranging from a single-core 32-bit RISC-V microcontroller-class processor to a Linux capable quad-core 64-bit out-of-order processor. Key features of the five VEGA cores developed by the C-DAC: VEGA ET1031 – 32-bit single-core 3-stage in-order RV32IM processor with AHB/AXI4.bus, optional MMU, optional Debug VEGA AS1061 – 64-bit single-core 6-stage in-order RV64IMAFDC processor with 8KB D-cache, 8KB I-cache, FPU, AHB/AXI4 bus VEGA AS1161 – 64-bit single-core 16-stage pipeline out-of-order RV64IMAFDC processor with 32KB D-cache, 32KB I-cache, FPU, AHB/AXI4/ACE bus VEGA AS2161 […]

FOSDEM 2022 schedule with embedded Linux, IoT, automotive… sessions

While typically taking place in Brussels, Belgium, FOSDEM 2022 will take place online just like FOSDEM 2021 due to COVID-19 restrictions. The good news is that it means anybody can attend it live from anywhere in the world, and makes it more like “FOSDIM”, replacing European with International, in “Free and Open Source Developers’ European Meeting”. FOSDEM 2022 will take place on February 5-6 with 637 speakers, 718 events, and 103 tracks. I’ve made my own little virtual schedule below mostly with sessions from the Embedded, Mobile and Automotive devroom, but also other devrooms including “Computer Aided Modeling and Design”, “FOSS on Mobile Devices”, “Libre-Open VLSI and FPGA”, and others. Saturday, February 5, 2022 12:30 – 13:00 – Five mysteries in Embedded Linux by Josef Holzmayr Once you start out in embedded Linux, there is a lot to do. Some things are obvious, some less so. First and foremost, […]