QEMU 9.0 open-source emulator just came out the other day, and it brings on board major updates and improvements to Arm, RISC-V, HPPA, LoongArch, and s390x emulation. But the most notable updates are in Arm and LoongArch emulation. The QEMU 9.0 emulator now supports the Raspberry Pi 4 Model B, meaning you can run the 64-bit Raspberry Pi OS for testing applications without owning the hardware. However, QEMU 9.0 has some limitations since Ethernet and PCIe are not supported for the Raspberry Pi board. According to the developers, these features will come on board in a future release. For now, the emulator supports SPI and I2C (BSC) controllers. Still on ARM, QEMU 9.0 provides board support for the mp3-an536 (MPS3 dev board + AN536 firmware) and B-L475E-IOT01A IoT node, plus architectural feature support for Nested Virtualization, Enhanced Counter Virtualization, and Enhanced Nested Virtualization. If you develop applications for the LoongArch […]

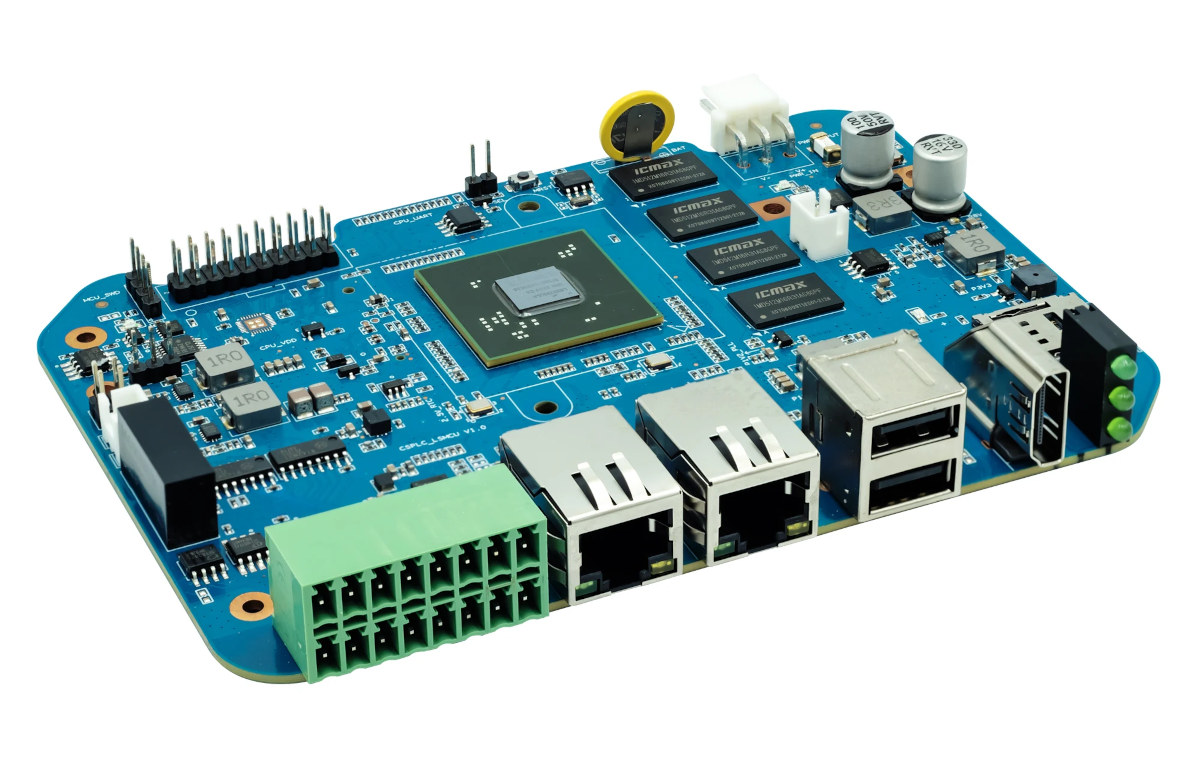

Loongson 2K1000LA dual-core LoongArch processor powers industrial SBCs and IoT gateways

Loongson 2K1000LA is a 1GHz dual-core 64-bit LoongArch processor designed for industrial applications with gigabit Ethernet, SATA, two PCIe interfaces, two digital video outputs, audio interfaces, USB 2.0, and others all in a 1 to 5W power envelop. It is found in Loongson’s own development board and Banana Pi BPI-5020 2K1000LA SBC. The LoongArch architecture was first introduced in 2021 as an alternative to Arm, x86, and RISC-V, and heavily inspired by MIPS with extra instructions. Some of the first LoongArch processors were the Loongson 3A5000 and 3C5000 SoCs for desktop computers and servers respectively, and now, the company has launched a lower-power processor for industrial applications, such as IoT gateways, with the 2K1000LA. Loongson 2K1000LA specifications We only have some basic specifications from the product page on Loongson’s website.; CPU – 2x 64-bit LoongArch cores clocked at 1GHz FPU – 128-bit vector unit Cache 32KB L1 instruction cache 32KB […]

Linux 6.7 release – Main changes, Arm, RISC-V, and MIPS architectures

Linus Torvalds has just announced the release of Linux 6.7, following Linux 6.6 LTS a little over two months ago: So we had a little bit more going on last week compared to the holiday week before that, but certainly not enough to make me think we’d want to delay this any further. End result: 6.7 is (in number of commits: over 17k non-merge commits, with 1k+ merges) one of the largest kernel releases we’ve ever had, but the extra rc8 week was purely due to timing with the holidays, not about any difficulties with the larger release. The main changes this last week were a few DRM updates (mainly fixes for new hw enablement in this version – both amd and nouveau), some more bcachefs fixes (and bcachefs is obviously new to 6.7 and one of the reasons for the large number of commits), and then a few random […]

Linux 6.5 release – Notable changes, Arm, RISC-V and MIPS architectures

Linus Torvalds has just announced the release of Linux 6.5 on the Linux Kernel Mailing List (LKML): So nothing particularly odd or scary happened this last week, so there is no excuse to delay the 6.5 release. I still have this nagging feeling that a lot of people are on vacation and that things have been quiet partly due to that. But this release has been going smoothly, so that’s probably just me being paranoid. The biggest patches this last week were literally just to our selftests. The shortlog below is obviously not the 6.5 release log, it’s purely just the last week since rc7. Anyway, this obviously means that the merge window for 6.6 starts tomorrow. I already have ~20 pull requests pending and ready to go, but before we start the next merge frenzy, please give this final release one last round of testing, ok? Linus The earlier […]

Linux 5.19 Release – Main changes, Arm, RISC-V and MIPS architectures

Linus Torvalds has just announced the release of Linux 5.19. It should be the last 5.xx version, with Linux 6.0 coming for the next cycle: So here we are, one week late, and 5.19 is tagged and pushed out. The full shortlog (just from rc8, obviously not all of 5.19) is below, but I can happily report that there is nothing really interesting in there. A lot of random small stuff. In the diffstat, the loongarch updates stand out, as does another batch of the networking sysctl READ_ONCE() annotations to make some of the data race checker code happy. Other than that it’s really just a mixed bag of various odds and ends. On a personal note, the most interesting part here is that I did the release (and am writing this) on an arm64 laptop. It’s something I’ve been waiting for for a _loong_ time, and it’s finally reality, […]

Loongson’s first LoongArch processors – 3A5000 for computers, 3C5000L for servers

Loongson has officially launched the first processors based on LoongArch CPU instruction set architecture designed for made-in-China SoCs without the need to license technology made outside of China. Loongsoon LS3C5000L (3C5000L) 16-core server processor clocked at up to 2.5 GHz is now official and is apparently comprised of four LS3A5000 (3A5000) LoongArch processors designed for desktop computers and laptops. Loongson 3A5000 CnTechPost reports Loongson 3A5000 quad-core 64-bit GS464V processor runs at 2.3GHz-2.5GHz. GS464V microarchitecture comes with four fixed-point units, two 256-bit vector operations units, and two access memory units. The processor also includes two 64-bit DDR4-3200 controllers with ECC checksum support, as well as four HyperTransport 3.0 controllers with multi-processor data consistency support. Performance-wise, Loongson 3A5000 is said to achieve 26+ points in the single-core and floating-point SPEC CPU2006 benchmarks, and over 80 in the multi-core version of the benchmarks. That’s about 50 percent higher performance than the previous pin-compatible […]

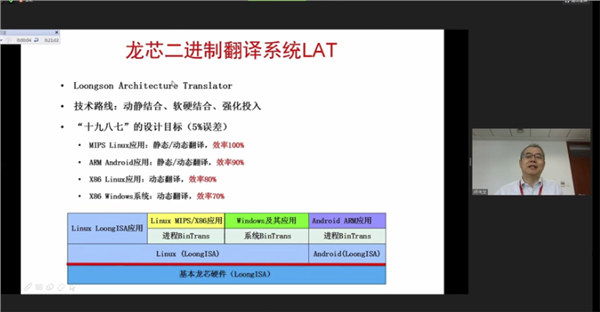

Loongson unveils LoongArch CPU instruction set architecture for processors made in China

Loongson is a Chinese company better known for its MIPS processors, and we often see the company being mentioned in mainline Linux changelogs with regards to updated to Loongson MIPS SoC’s. But with the MIPS architecture fading away, the company has decided to create its own CPU instruction set architecture (ISA) called LoongArch, short for Loongson Architecture, that is independent of x86, Arm, and even RISC-V architecture. The reason for the move is that foreign CPU manufacturers use the instruction system as a means to control the ecology, and manufacturers like Loongsoon need to obtain “authorization” to develop compatible CPUs, meaning it’s impossible to develop an independent industrial ecosystem. Loongsoon further illustrates the point by saying “Chinese people can write novels in English, but it is impossible to form Chinese national culture based on English”. That makes sense considering the trade sanctions regularly imposed by the United States that make […]

Linux 4.9 Release – Main Changes, ARM and MIPS Architectures

Linus Torvalds released Linux 4.9 on Sunday: So Linux 4.9 is out, and the merge window for 4.10 is thus open. With the extra week for 4.9, the timing for the merge window is obviously a bit awkward, and it technically closes in two weeks on Christmas Day. But that is a pure technicality, because I will certainly stop pulling on the 23rd at the latest, and if I get roped into Xmas food prep, even that date might be questionable. I could extend the merge window rather than cut it short, but I’m not going to. I suspect we all want a nice calm winter break, so if your stuff isn’t ready to be merged early, the solution is to just not merge it yet at all, and wait for 4.11. Just so you all know (I already bcc’d the main merge window suspects in a separate mailing last […]