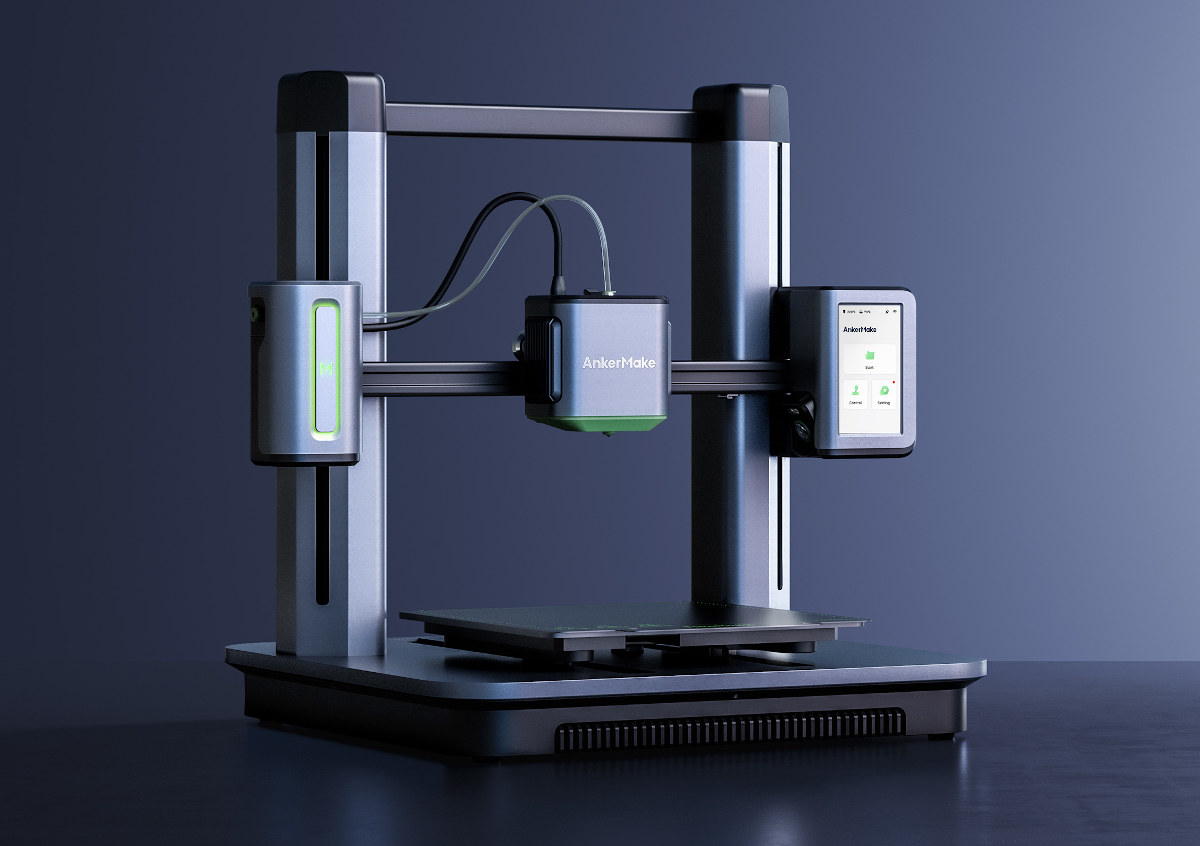

Anker is better known for its charger and power banks, but the company has now entered the 3D printer market with the AnkerMake M5 3D printer which is said to print five times faster and comes with an AI camera for monitoring the prints. Besides the up to 300mm/s printing speed, other highlights of the 3D printer include Google Assistant & Amazon Alexa voice assistant compatibility, and easy assembly that requires 3 steps done in about 15 minutes. AnkerMake M5 3D printer specifications: SoC – Ingenic X2000 tri-core MIPS processor with 2x XBurst cores @ 1.2 GHz plus one XBurst0 core @ 240 MHz running Linux MCU – STM32F407 running Marlin firmware Print volume (L x W x H) – 235 × 235 × 250 mm Standard speed – 250 mm/s Speed range – 50 – 300 mm/s Acceleration speed – 2500 mm/s² X-axis movement – 42 – 40 stepper […]

Linux 5.17 release – Main changes, Arm, RISC-V, and MIPS architectures

Linus Torvalds has just released Linux 5.17: So we had an extra week of at the end of this release cycle, and I’m happy to report that it was very calm indeed. We could probably have skipped it with not a lot of downside, but we did get a few last-minute reverts and fixes in and avoid some brown-paper bugs that would otherwise have been stable fodder, so it’s all good. And that calm last week can very much be seen from the appended shortlog – there really aren’t a lot of commits in here, and it’s all pretty small. Most of it is in drivers (net, usb, drm), with some core networking, and some tooling updates too. It really is small enough that you can just scroll through the details below, and the one-liner summaries will give a good flavor of what happened last week. Of course, this means […]

Linux 5.16 Release – Main Changes, Arm, RISC-V and MIPS architectures

Linus Torvalds has just announced the release of Linux 5.16: Not a lot here since -rc8, which is not unexpected. We had that extra week due to the holidays, and it’s not like we had lots of last-minute things that needed to be sorted out. So this mainly contains some driver fixes (mainly networking and rdma), a cgroup credential use fix, a few core networking fixes, a couple of last-minute reverts, and some other random noise. The appended shortlog is so small that you might as well scroll through it. This obviously means that the merge window for 5.17 opens tomorrow, and I’m happy to say I already have several pending early pull requests. I wish I had even more, because this merge window is going to be somewhat painful due to unfortunate travel for family reasons. So I’ll be doing most of it on the road on a laptop […]

Linux 5.15 LTS release – Main Changes, Arm, RISC-V and MIPS architectures

Linus Torvalds released Linux 5.15, an LTS version, this past Sunday: It’s been calm, and I have no excuse to add an extra rc, so here we are, with v5.15 pushed out, and the merge window starting tomorrow. Which is going to be a bit inconvenient for me, since I also have some conference travel coming up. But it’s only a couple of days and I’ll have my laptop with me. Sometimes the release timing works out, and sometimes it doesn’t.. Anyway, the last week of 5.15 was mainly networking and gpu fixes, with some random sprinkling of other things (a few btrfs reverts, some kvm updates, minor other fixes here and there – a few architecture fixes, couple of tracing, small driver fixes etc). Full shortlog appended. This release may have started out with some -Werror pain, but it calmed down fairly quickly and on the whole 5.15 was […]

Linux 5.14 Release – Main changes, Arm, MIPS, and RISC-V architectures

Linus Torvalds has just announced Linux 5.14 release which happens to almost coincide with the anniversary of the initial announcement of the “small” project on August 25, 1991, about 30 years ago. Here’s Linux 5.14’s announcement: So I realize you must all still be busy with all the galas and fancy balls and all the other 30th anniversary events, but at some point you must be getting tired of the constant glitz, the fireworks, and the champagne. That ball gown or tailcoat isn’t the most comfortable thing, either. The celebrations will go on for a few more weeks yet, but you all may just need a breather from them. And when that happens, I have just the thing for you – a new kernel release to test and enjoy. Because 5.14 is out there, just waiting for you to kick the tires and remind yourself what all the festivities are […]

Debian 11 “BullsEye” released with Panfrost & Lima GPU drivers, exFAT support, driverless printing

Debian 11 “BullsEye” has been released with Panfrost & Lima open-source drivers for Arm GPUs, in-kernel exFAT file system, driverless printing, and many more updates, plus a 5-year support window. Debian’s release is significant as the Linux operating system serves as the base for Ubuntu and derivatives, Raspberry Pi OS, and together with Ubuntu, is one of the operating systems supported by Armbian which offers images for a range of Arm-based single board computers. Arm Mali GPU support in Debian 11 I remember a few years ago 3D graphics acceleration on Arm boards was news, as it was quite a challenge to get it working due to binary blobs. But Debian 11 now comes with Mesa 20.3 framework which includes Panfrost and Lima open-source Mali GPU drivers by default, as well as the Vulkan 1.0 conformant V3DV driver for Raspberry Pi 4. As noted in the documentation that means the […]

WARP-V: A RISC-V CPU Core Generator Supporting MIPS ISA

If you have been working on open standard RISC-V ISA CPU cores, there is a high chance that you have come across WARP-V. For newbies, WARP-V is a RISC-V CPU core generator written in TL-Verilog (Transaction-Level Verilog) that supports not only RISC-V but also MIPS ISA. WARP-V has been in discussion for a while due to its unparalleled architectural scalability in a small amount of code. The famous proverb “Necessity is the mother of invention” applies to the invention of TL-Verilog and with that this WARP-V CPU core generator. For decades, hundreds of engineers have been working on designing a single CPU core that was more complex in the race to achieve higher single-core performance. But with recent developments in the semiconductor industry, developer and engineer Steve Hoover, with decades of experience in designing CPU cores, has come up with the idea of developing a WARP-V core in just 1.5 […]

Linux 5.13 Release – Notable changes, Arm, MIPS and RISC-V architectures

Linus Torvalds has just announced the release of Linux 5.13: So we had quite the calm week since rc7, and I see no reason to delay 5.13. The shortlog for the week is tiny, with just 88 non-merge commits (and a few of those are just reverts). It’s a fairly random mix of fixes, and being so small I’d just suggest people scan the appended shortlog for what happened. Of course, if the last week was small and calm, 5.13 overall is actually fairly large. In fact, it’s one of the bigger 5.x releases, with over 16k commits (over 17k if you count merges), from over 2k developers. But it’s a “big all over” kind of thing, not something particular that stands out as particularly unusual. Some of the extra size might just be because 5.12 had that extra rc week. And with 5.13 out the door, that obviously means […]