AMD Versal Premium Series Gen 2 SoC FPGA combines dual-core Cortex-A72 and dual-core Cortex-R5F processors with high-end FPGA fabric with up to 3.2 million logic cells and CXL 3.1 (Compute Express Link), PCIe Gen6, and DDR5/LPDDR5X high-bandwidth interfaces for data center, communication equipment, test & measurement, and aerospace & defense data-intensive applications. AMD Versal Premium Gen2 specifications: CPU cores Dual-core Arm Cortex-A72 application core, 48 KB/32 KB L1 Cache w/ parity & ECC; 1 MB L2 Cache w/ ECC Dual-core Arm Cortex R5F, 32 KB/32 KB L1 Cache, and 256 KB TCM w/ECC Memory – 256MB on-chip with ECC FPGA fabric System Logic Cells – Up to 3,273,480 LUTs – Up to 1,496,448 DSP Engines – Up to 7,616 Interfaces connected to CPU cores 2x Ethernet 2x UART, 2x SPI, 2x I2C 2x CAN-FD 1x USB 2.0 FPGA memory, interfaces, I/Os, and transceivers Up to 327 Mbit memory @ 273 […]

Axiomtek CEM710 COM Express module features Intel Xeon D-1700 SoC with up to 100Gbps Ethernet support

In 2022, we covered Intel’s Xeon D (Ice Lake-D) processor family, which includes the D-2700 and D-1700 models. These processors are designed for software-defined networking and edge applications, providing data center-grade capabilities at the edge. Key features include integrated AI and crypto acceleration, built-in Ethernet, and support for Intel Time Coordinated Computing (TCC) and Time-Sensitive Networking (TSN) to ensure high reliability. Leveraging these advanced capabilities, companies like ADLINK Technology and Congatec have introduced COM-HPC server modules and COM Express Type 7 modules based on the new Xeon D lineup. Axiomtek’s CEM710 is a COM Express Type 7 Basic Module powered by Intel Xeon D-1700 Series processors, designed for edge computing, industrial automation, and data-intensive applications. It offers up to 10 cores, 100Gbps Ethernet, and 64GB of DDR4 ECC memory, along with PCIe Gen3 slots for expandability. With rugged features and TPM 2.0 for security, it ensures reliable performance in demanding […]

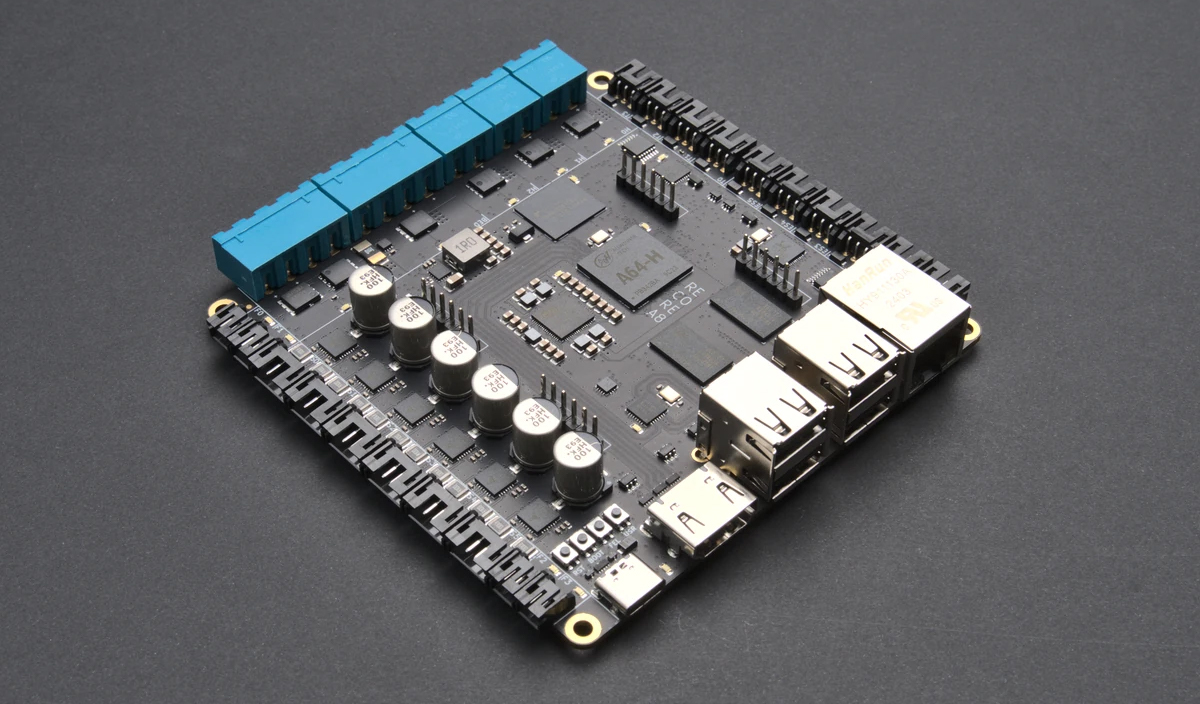

Recore A8 – An Allwinner A64-powered 3D printer control board with TMC2209 stepper drivers

The Recore A8 is an all-in-one 3D printer control board built around the Allwinner A64 SoC. The board includes six soldered TMC2209 stepper motor drivers, cooled by an 8-layer PCB for durability. To make the connection better the board features industry-standard JST PH connectors for secure cable connections. Most of the connectors are flexible and support end-stops, Neopixels, servos, inductive probes, and BLTouch. Two Expansion headers on the board allow for two additional stepper motor drivers. Additionally, the board supports various temperature sensors, including regular thermistors, thermocouples, and PT100/PT1000 sensors (PT100 requires an extra board). Elias Bakken has been working on this board since 2019 and in our post about the earlier Recore A5, we have seen how Elias leverages Allwinner A64’s 300 MHz AR100 core to control real-time I/Os. Recore A8 specifications: SoC – Allwinner A64 quad-core Cortex-A53 processor running at 1 GHz, with AR100 32-bit core @ 300 MHz, Mali-400MP2 […]

Microchip PIC64GX is a quad-core 64-bit RISC-V microprocessor for real-time processing

Microchip has introduced its first 64-bit RISC-V microprocessor family with the PIC64GX pin-to-pin compatible with the company’s PolarFire SoC FPGA devices and designed for edge designs for the industrial, automotive, communications, IoT, aerospace, and defense segments. The PIC6GX MPU supports asymmetric multiprocessing (AMP) to run Linux, real-time operating systems, and bare metal in a single processor cluster with secure boot capabilities. The company further claims the PIC64GX MPU is “the first RISC-V multi-core solution that is AMP capable for mixed-criticality systems”. The first member of the PIC64GX RISC-V family is the PIC64GX1000 microprocessor. Microchip PIC64GX1000 specifications: CPU Quad-core SiFive U54 64-bit five-stage, single-issue, in-order pipeline RISC-V (RV64GC) processor at up to 625 MHz with AMP and deterministic latencies, PMP and MMU units Single-core SiFive E51 64-bit RISC-V (RV64IMAC) monitor processor core at up to 625 MHZ with PMP unit Cache L1 memory subsystem with Single-Error Correct, Double-Error Detect (SECDED) Flexible […]

Embedded Open Source Summit 2024 schedule – Embedded Linux, Zephyr OS, and Real-time Linux

The Embedded Open Source Summit 2024 (EOSS 2024) will take place on April 16-18 and the Linux Foundation has already announced the schedule with conference sessions, lightning talks, and birds of a feather (BoF) sessions covering embedded Linux, Zephyr OS, and real-time (RT) Linux. While I won’t be attending in person, I still find it interesting to check out the schedule as we may learn more about the current status of embedded Linux. So I’ve created my own little virtual schedule out of the available talks. Tuesday, April 16 – Day 1, Embedded Open Source Summit 2024 9:05 – 9:45 – No, It’s (Still) Never Too Late to Upstream Your Legacy Linux-Based Platforms by Neil Armstrong, Linaro Nearly 7 years ago, Neil already spoke about this subject in Berlin, and it’s still very true. Do you maintain or used to maintain a Linux-based board or SoC off-tree? Then there are […]

Microchip PIC18-Q20 low-pin count MCU comes with up to two I3C interfaces

Microchip PIC18-Q20 is a new family of microcontrollers (MCUs) with a low-pin count (14 and 20-pin packages) that integrates up to two I3C interfaces as well as multi-voltage I/O (MVIO) interfaces. MIPI I3C was first teased in 2014, then officially announced in 2017, and the first MIPI I3C specification was released the following year, as a backward compatible update to I2C with lower power consumption, and higher bitrate allowing it to compete against SPI. We’ve seen it used in a few application processors and microcontrollers, but it’s the first time I3C can be found in a lower-cost, low-pin count microcontroller. Microchip PIC18-Q20 specifications: Core – PIC18 8-bit RISC microcontroller core @ 64 MHz Memory – 1KB to 4KB RAM Storage – 16KB to 64KB with Memory Access Partition (MAP) support, 256B EEPROM Peripherals Up to 2x I3C device interfaces Adhere to MIPI I3C Basic Specification 1.0 Support Target Reset Action […]

EPIC-ADS7-PUC Alder Lake-S embedded system is made for robotics, automation, healthcare imaging

AAEON EPIC-ADS7-PUC is an embedded system based on an up to 12th Gen Intel Core i7-12700E Alder Lake-S processor and designed for robotics, automation, and healthcare imaging applications. The embedded computer supports up to 32GB DDR5 and two SATA III storage devices, offers three 4K video outputs via HDMI and DisplayPort connectors, one 2.5GbE and three Gigabit Ethernet ports, along with Intel TCC support, up to six USB 3.2 Gen 2 ports, two RS232/422/4485 COM ports, and some SKUs support Intel Time Coordinated Computing (TCC) for real-time control. Key Features: SoC – Intel Core Alder Lake-S processor, up to the 12-core (8P+4E) Core i7-12700E processor clocked at up to 4.8 GHz with Intel UHD Graphics 770; TDP: 65W Chipset – Intel 600 Series Desktop Chipset (R680E/Q670E/H610E) System Memory – Up to 32GB DDR5 4800 via 2x SODIMM socket (16GB max each) Storage – 2x SATA 3 with +5V onboard SATA […]

Imagination unveils IMG RTXM-2200 32-bit RISC-V real-time “Catapult” CPU

Imagination IMG RTXM-2200 32-bit RISC-V real-time CPU core is the first member of the company’s Catapult family comprised of four distinct RISC-V families for dynamic microcontrollers, real-time embedded CPUs, high-performance application CPUs, and functionally safe automotive CPUs. The company says it’s a highly scalable real-time, deterministic, 32-bit embedded CPU, that is feature-rich and flexible in design for mainstream devices, but, excuse the pun, leaves most of the details to your imagination… The new core will mostly be used as a helper core (aka co-processor) in more complex SoCs for 5G modems, cellular base stations, networking solutions for data transfer, packet management, and storage controllers, but may also find its way into smart meters. In all fairness, we do have some limited technical details with L1 cache sizes up to 128KB, I/D TCM sizes up to 128KB, and PMA regions. The real-time core will also include optional features such as single-point […]