Alibaba introduces a range of RISC-V processors in the last few years with the Xuantie family ranging from the E902 micro-controller class core to the C910 core for servers in data centers. This also includes the XuanTie C906 core found in the Allwinner D1 single-core RISC-V processor. While RISC-V is an open standard and there’s a fair share of open-source RISC-V cores available, many commercial RISC-V cores are closed source, but Zhang Jianfeng, President of Alibaba Cloud Intelligence speaking at the 2021 Apsara Conference, announced that T-Head had open-sourced four RISC-V-based Xuantie series processor cores, namely Xuantie E902, E906, C906, and C910, as well as related software and tools. Those are not empty words as we can find the RTL for the four cores released on T-Head Semiconductor’s Github account with the first commits having taken place yesterday. Each repository contains the code and instructions to get started, all under […]

HarmonyOS development board shows up for $11

Last year, we noted the Hisilicon Hi3861 based HiSpark WiFi IoT development board with supports LiteOS and HarmonyOS that was available in China for just under $10, or as part of a devkit with baseboard and modules for around $60. Although not very practical, buying from Taobao was possible, but there’s now what appears to be a new revision of the Hi3861V100 based HarmonyOS development board in a wider form factor on Banggood for $10.99. Hi3861 development board specifications: MCU – Hisilicon Hi3861V100 32-bit RISC-V microcontroller @ up to 160 MHz with 352 KB SRAM and 288 KB ROM, 2 MB flash memory, and WiFI 4 connectivity; QFN-32 5x5mm package WiFi 802.11b/g/n standard up to 72.2 Mbps @ HT20 2.4 GHz frequency band (ch1-ch14). Station (STA) and access point (AP) modes with up to 6 clients for the latter WiFi mesh with up to 256 nodes Security – WPA, WPA2 […]

OpenBSD 7.0 adds 64-bit RISC-V, improves Apple Arm silicon support

OpenBSD 7.0, the 51st release of the UNIX-like operating system, was outed on October 14, 2021, with the introduction of 64-bit RISC-V support for HiFive Unmatched and PolarFire SoC Icicle Kit boards, as well as further improvements to ARM64 targets, notably for Apple Silicon Macs, although it’s not quite ready for general use yet. You’ll find the complete list of new features and updates on the OpenBSD website, but here are some of the highlights: New platforms – OpenBSD 7.0 add 64-bit RISC-V support Extended platforms arm64 Improvements to Apple Silicon Macs support USB 3, NVMe storage, GPIO driver, power management, etc… Enabled LEDs for the LAN7800 chip as found on the Raspberry Pi 3 Model B+. Added Type-C PHY controller found on the Rockchip RK3399. Implemented multicast support to Marvell ARMADA chips Various other changes to mips64, amd64, armv7, powerpc64 Kernel improvements Enabled dynamic tracker (dt) for GENERIC kernels […]

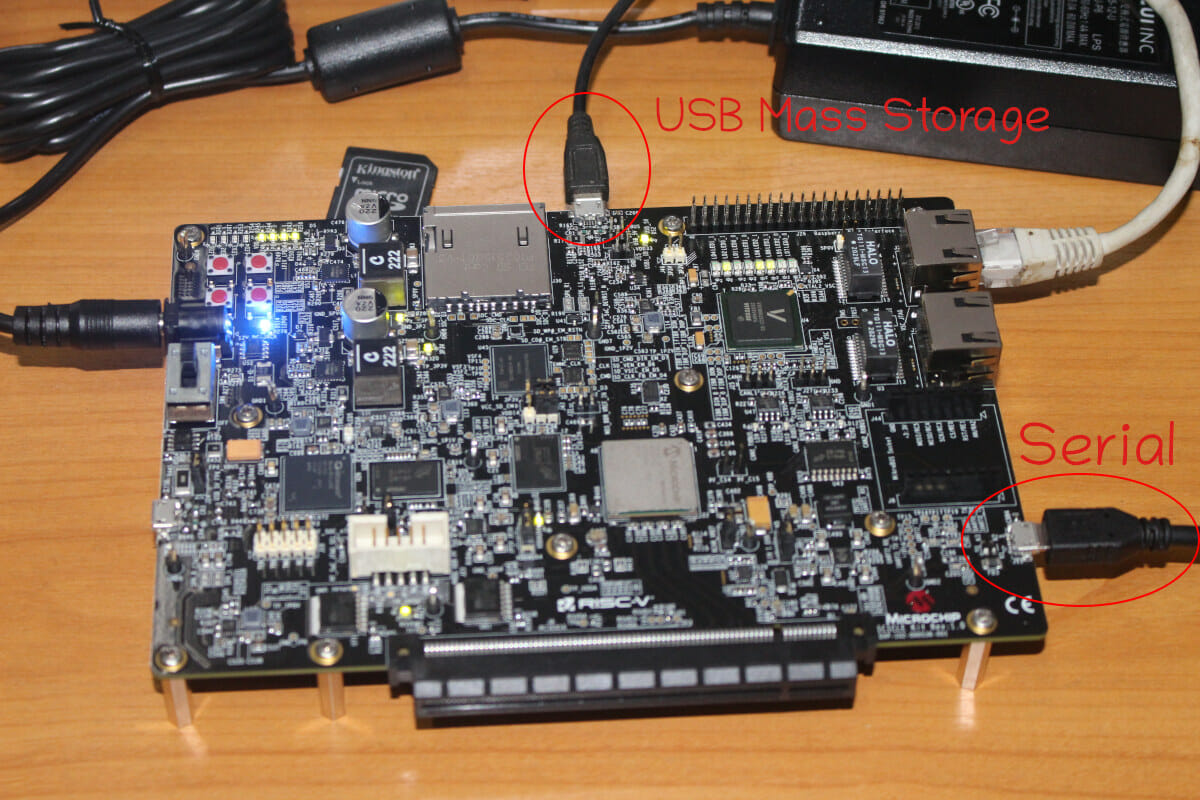

Getting Started with the Yocto Linux BSP for Polarfire SoC FPGA Icicle Kit

Last month I received Microchip PolarFire SoC FPGA Icicle development kit that features PolarFire SoC FPGA with a Penta–core 64-bit RISC-V CPU subsystem and an FPGA with 254K LE, and booted it into the pre-installed Linux operating systems based on OpenEmbedded. Today, I’ll show how to get started with the Yocto BSP and run the EEMBC CoreMark benchmark, and I’ll check out the FPGA with Libero SoC Design Suite in a couple of weeks. Operating Systems supported by PolarFire SoC FPGA My initial idea was to focus this part of the review on Linux on RISC-V status, checking some system information, running some benchmarks (e.g. SBC-Bench), compiling the Linux kernel, and installing services like a LEMP stack (Linux, Nginx (pronounced Engine-X), MySQL, PHP) which could be used for WordPress hosting for instance. But then I looked at the operating systems supported with Microchip PolarFire SoC FPGA. There’s a Yocto Linux […]

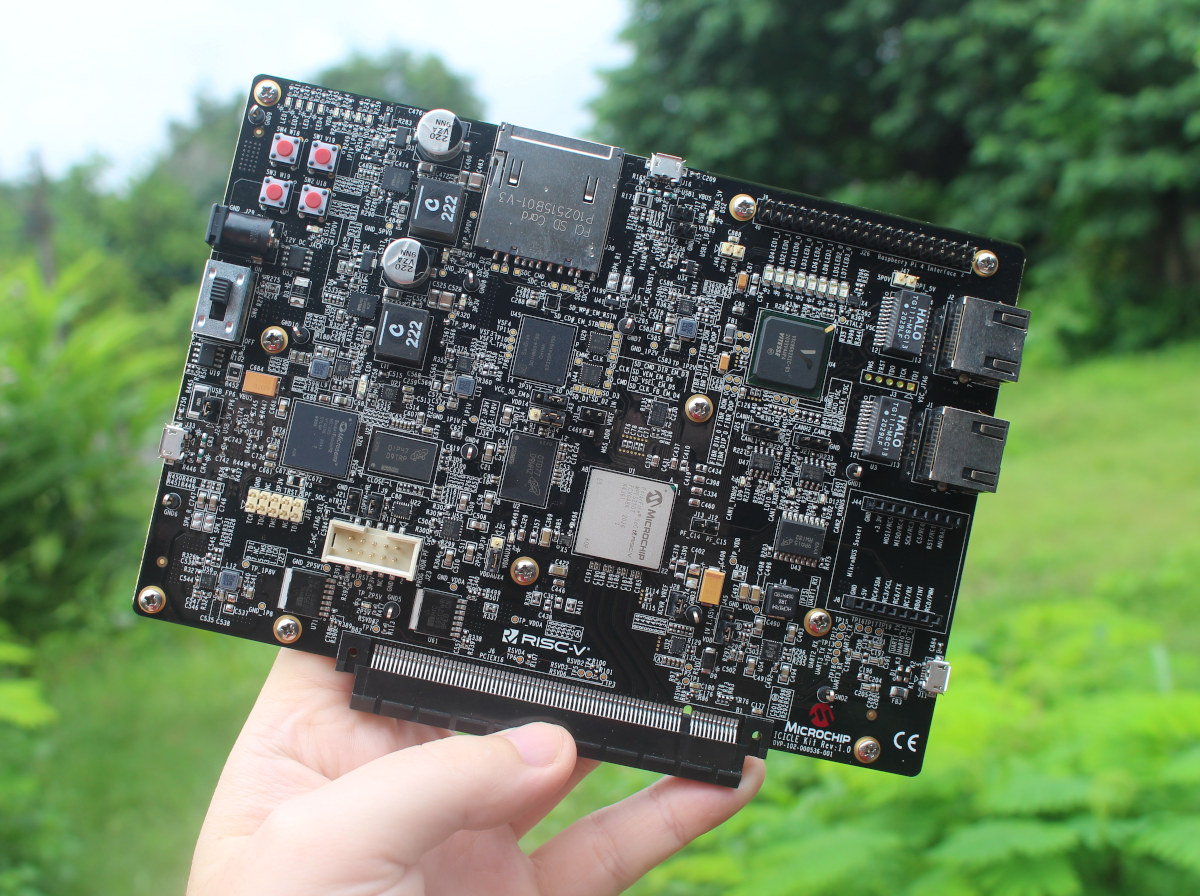

A first look at Microchip PolarFire SoC FPGA Icicle RISC-V development board

Formally launched on Crowd Supply a little over a year ago, Microchip PolarFire SoC FPGA Icicle (codenamed MPFS-ICICLE-KIT-ES) was one of the first Linux & FreeBSD capable RISC-V development boards. The system is equipped with PolarFire SoC FPGA comprised a RISC-V CPU subsystem with four 64-bit RISC-V (RV64GC) application cores, one 64-bit RISC-V real-time core (RV64IMAC), as well as FPGA fabric. Backers of the board have been able to play with it for several months ago, but Microchip is now sending the board to more people for evaluation/review, and I got one of my own to experiment with. That’s good to have a higher-end development board instead of the usual hobbyist-grade board. Today, I’ll just have a look at the kit content and main components on the board before playing with Linux and FPGA development tools in an upcoming or two posts. Microchip PolarFire SoC FPGA Icicle Unboxing The board […]

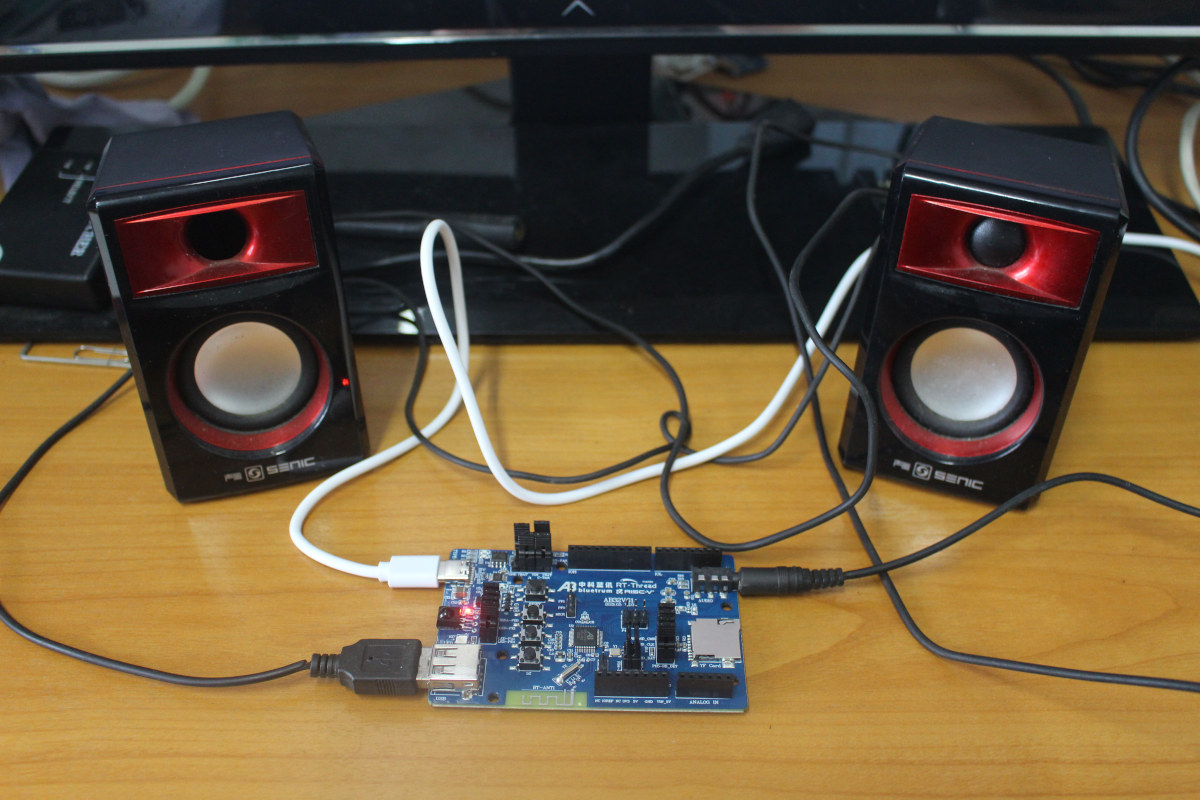

Getting started with Bluetrum AB32VG1 RISC-V Bluetooth audio board using RT-Thread

Bluetrum AB32VG1 is a development board based on AB5301A RISC-V microcontroller designed for Bluetooth audio applications as well as general-purpose projects that works with RT-Thread real-time operating system. RT-Thread sent me a board for review, and I’ll write about my experience in a getting started guide for Bluetutm AB32VG1 trying out the RT-Thread Studio IDE with the LED blink and audio samples, as there’s no Bluetooth sample at this time… Bluetrum AV32VG1 Unboxing The board ships with a USB-C cable for power and programming. It offers Arduino UNO headers for expansion, a MicroSD card slot, a USB host port, a 3.5mm audio jack, an IR receiver, and a few buttons. There’s nothing to do on the bottom of the board apart from a QR Core for the WeChat app. There are also several configuration jumpers, but I could not find any documentation about these and did not mess with the […]

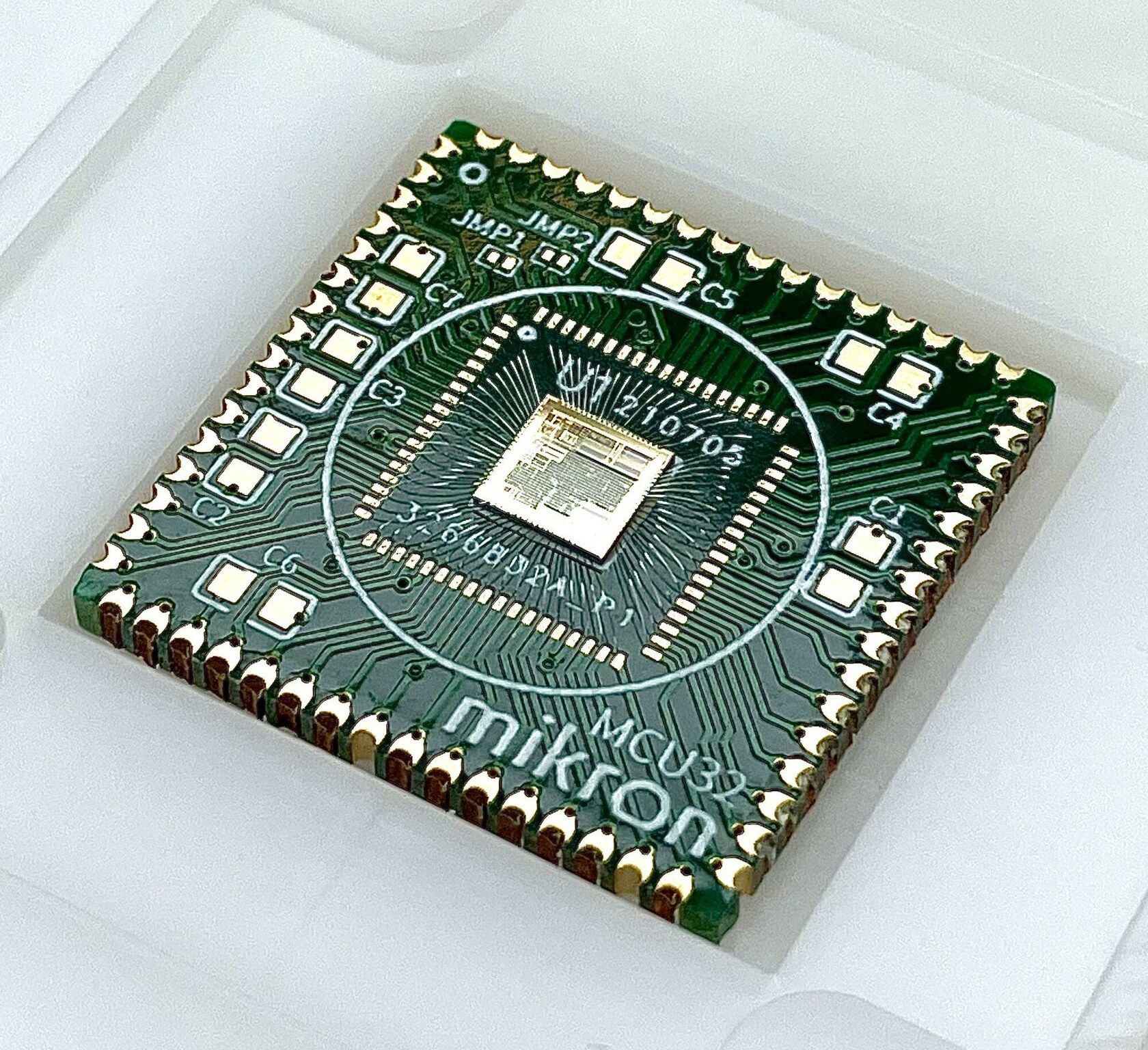

Mikron MIK32 – Made in Russia 32-bit RISC-V MCU offers features similar to STM32L0 MCU

The Mikron MIK32 is a 32-bit RISC-V microcontroller made in Russia with features similar to an STMicro STM32L0 Cortex-M0+ MCU that shows how RISC-V open-source architecture can help lower the barrier to entry, and let more companies design their own chips. The MIK32 microcontroller features CPU IP from Syntacore based in Saint Petersburg following the RV32IMC profile. Clocked at 32 MHz, the MCU comes with I2C, UART, SPI, ADC, DAC interfaces, as well as various timers, an interrupt controller, and more. Mikron MIK32 specifications: CPU Core – 32-bit RISC-V up to 32 MHz with 32 registers, embedded multiplier, debugger (TAP controller and JTAG interface), and interrupt controller Memory & Storage – 256 bytes OTP ROM, 16KB RAM, 8KB EEPROM Interfaces Storage I/F – SPI, Dual-SPI, Quad-SPI interfaces for NOR and NAND flash devices 4-channel DMA controller supporting low-power modes 2x I2C, 2x UART with synchronous mode support, 2x SPI 12-bit […]

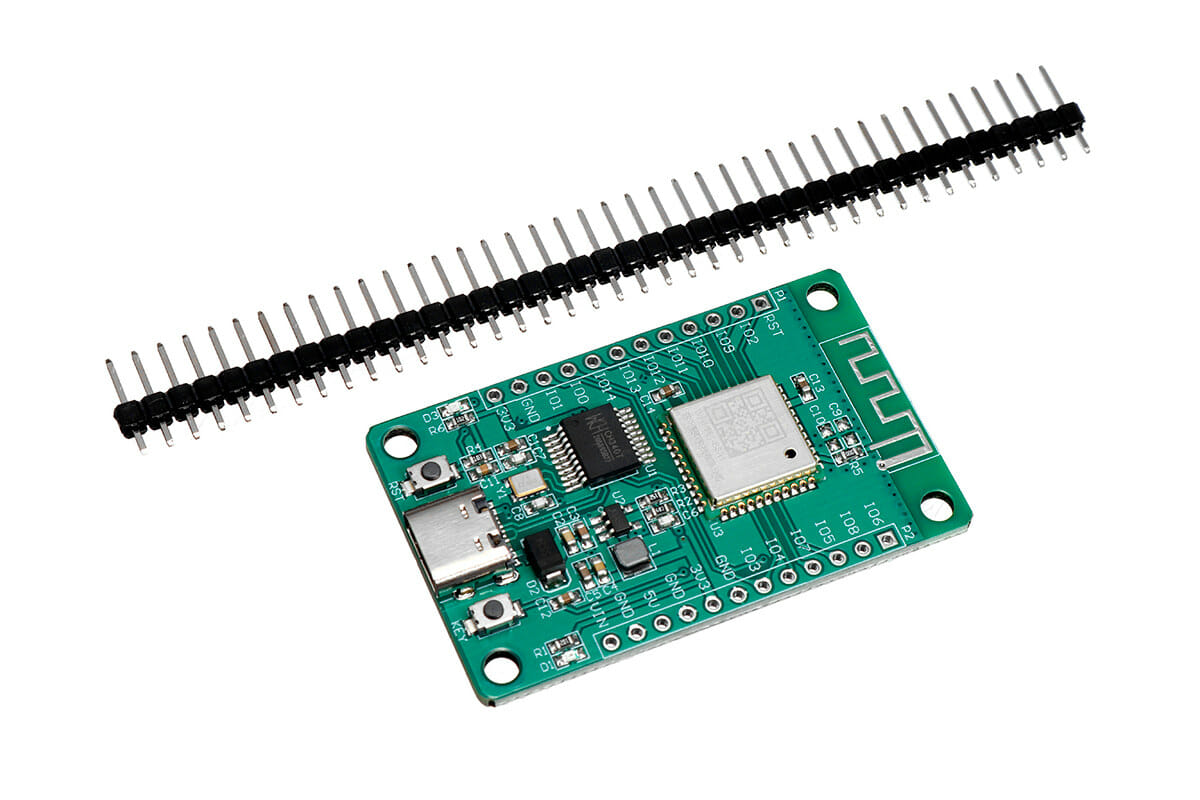

LILYGO T-32C3 – A small ESP32-C3 WiFi & BLE IoT module with 4MB flash

We’re slowly starting to see more hardware-based on ESP32-C3 RISC-V processor, and LILYGO T-32C3 is a compact module based on the WiFi & Bluetooth LE processor that includes 4MB flash and a PCB antenna. I’d expect T-32C3 to be eventually found in the company’s smartwatches and development boards, and it joins other ESP32-C3 modules from AI Thinker. LILYGO T-32C3 module specifications: SoC – Espressif ESP32-C3 RISC-V processor @ 160 MHz with 400 KB SRAM, 384 KB ROM, 8KB RTC SRAM, 2.4 GHz WiFi 4, Bluetooth 5.0 LE & Mesh Storage – 4MB flash On-board PCB antenna I/Os – 22x castellated holes with GPIO, 3x ADC, SPI, UART, I2C, Boot, Reset, 5V, 3.3V, GND Dimensions – 23 x 11 x 3.5 mm (4-layer PCB) Note the USB interface is not listed in the specs, but USB DN and DP signals are located on GPIO18 and GPIO19 so USB should also be […]