OK… I’m a bit late on that one. Linus Torvalds released Linux 5.7 last week: So we had a fairly calm last week, with nothing really screaming “let’s delay one more rc”. Knock wood – let’s hope we don’t have anything silly lurking this time, like the last-minute wifi regression we had in 5.6.. But embarrassing regressions last time notwithstanding, it all looks fine. And most of the discussion I’ve seen the last week or two has been about upcoming features, so the merge window is now open and I’ll start processing pull requests tomorrow as usual. But in the meantime, please give this a whirl. We’ve got a lot of changes in 5.7 as usual (all the stats look normal – but “normal” for us obviously pretty big and means “almost 14 thousand non-merge commits all over, from close to two thousand developers”), So the appended shortlog is only […]

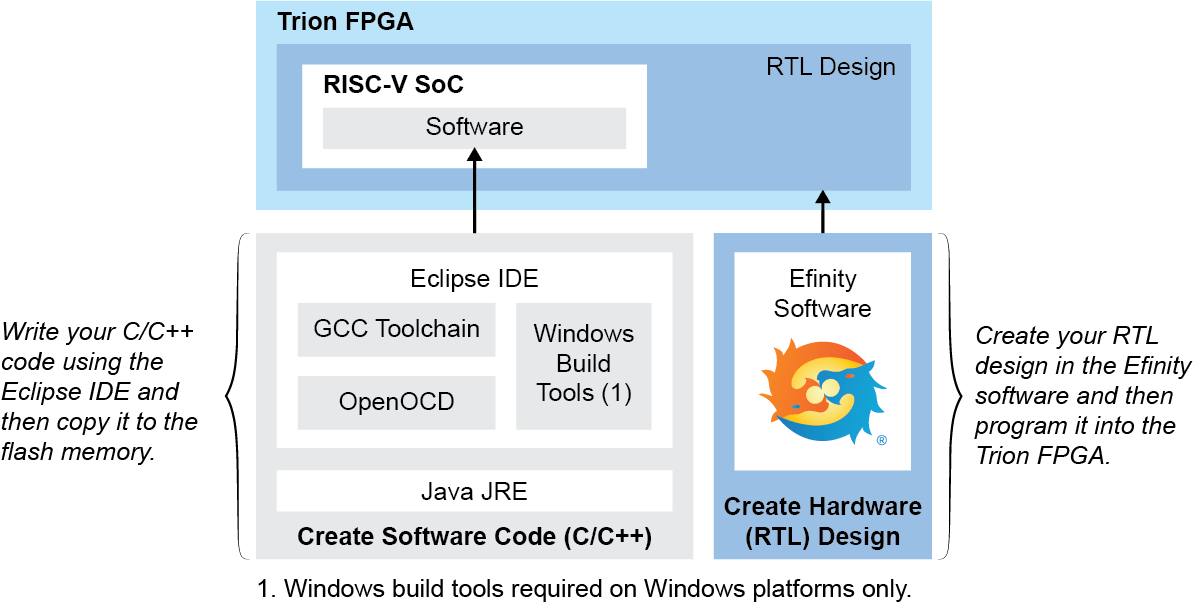

Efinix Releases Three RISC-V Software-Defined SoC’s Optimized for Trion FPGA’s

Efinix has announced three RISC-V Software-defined SoC’s based on Charles Papon’s VexRiscv core and optimized for the company’s Trion T8 to T120 FPGA’s. VexRiscv is a 32-bit RISC-V CPU using RISCV32I ISA with M and C extensions, has five pipeline stages (fetch, decode, execute, memory, and writeback), and a configurable feature set. Each SoC includes a RISC-V core, memory, as well as various I/O and interfaces. Key features for each of three RISC-V SoC’s: Ruby SoC FPGA footprint – ~12K LEs/78 RAM blocks Performance – 50 MHz (1.16 DMIPS/MHz) Memory – 4 KB on-chip RAM, up to 3.5 GB DDR DRAM Peripherals – 16x GPIO, Timer, PLIC, 3x SPI masters, 3x I2C masters/slaves, 2x UARTs 1x AXI4, 2x APB3 user peripherals Target applications – real-time system controls and image signal processing. Jade SoC FPGA footprint – ~7K LEs/93 RAM blocks Performance – 50 MHz (1.2 DMIPS/MHz) Memory – 32 KB […]

TTGO T-Watch K210 / K210 AIOT Watches Perform Face Detection with Kendryte K210 RISC-V Processor, ESP32 WiSoC

After covering ESP32 based TTGO T-Watch-2020 programmable watch last month, I noticed LilyGO launched “TTGO T-Watch K210 AIOT” watch with Kendryte K210 RISC-V AI SoC and a camera for face detection and recognition, and while searching for information, I discovered another apparently similar “TTGO T-Watch K210“. But let’s look into the specifications to find out what the differences are. I first came across TTGO T-Watch K210 AIOT, so let’s have a look at some preliminary specifications for this model: AI Processor – Kendryte K210 RISC-V Dualcore 64bit with FPU with 8MB SRAM Storage – 16MB QSPI flash, MicroSD card socket Display I/F – FPC connect for external display (not included) Camera – 2MP OV2640 sensor Audio – MAX98357A Audio codec; CVSD & SBC audio encoding Connectivity – 2.4 GHz 802.11b/g/n WiFi 4 up to 150 Mbps, Bluetooth 4.2 BR/EDR and BLE Debugging – USB-C port via CP2104 Expansion UART, SPI, […]

QEMU 5.0 Supports Recent Armv8.x Features, Cortex-M7 CPU, Host Directory Access, and More

QEMU (Quick EMUlator) is an open-source emulator that’s great to run programs on various architectures such as Arm, RISC-V, and many others when you don’t own proper hardware. The developers have now released QEMU 5.0.0 will plenty of new features and such as support for Armv8.1 to Armv8.4 architectures, Arm Cortex-M7 processor, various changes to MIPS, PowerPC, RISC-V, s390… architectures, support for accessing a directory on the host filesystem from the guest using virtiofsd and more. There have been over 2800+ commits from 232 developers, so the list of changes to too long to write here, but some of the highlights include: Support for passing host filesystem directory to guest via virtiofsd Support for ARMv8.1 VHE/VMID16/PAN/PMU, ARMv8.2 UAO/DCPoP/ATS1E1/TTCNP, ARMv8.3 RCPC/CCIDX, ARMv8.4 PMU/RCPC Added ARM Cortex-M7 CPU support New Arm boards: tacoma-bmc, Netduino Plus 2, and Orange Pi PC Allwinner SoC model now wires up the USB ports TPM support for […]

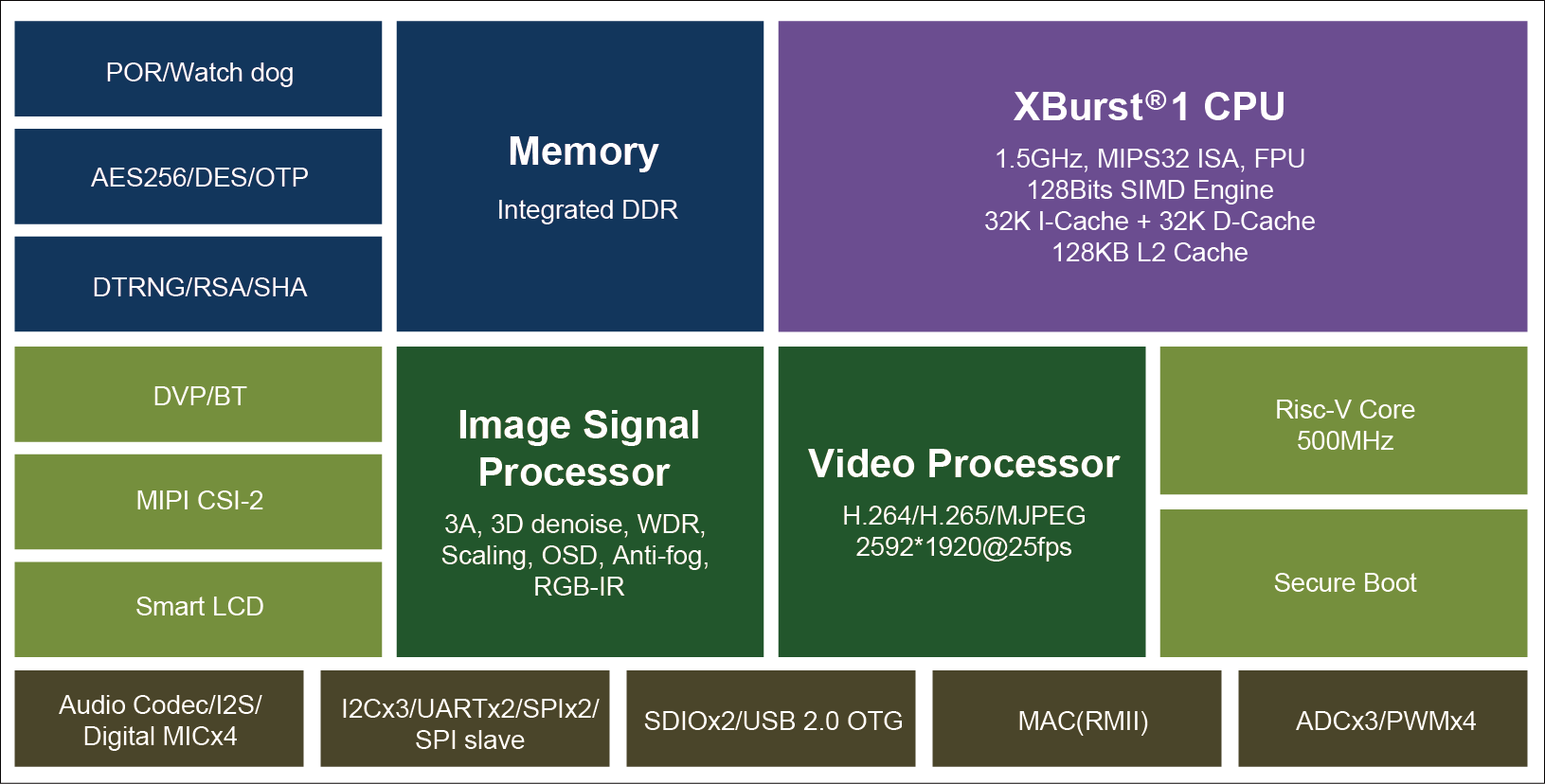

Ingenic T31 AI Video Processor Combines MIPS & RISC-V Cores

Last week we asked “is MIPS dead?” question following the news that Wave Computing had filed for bankruptcy, two MIPS Linux maintainers had left, and China-based CIP United now obtained the exclusive MIPS license rights for mainland China, Hong Kong, and Macau. Ingenic is one of those Chinese companies that have offered MIPS-based processors for several years, but one commenter noted that Ingenic joined the RISC-V foundation, and as a result, we could speculate the company might soon launch RISC-V processors, potentially replacing their MIPS offerings. But Ingenic T31 video processor just features both with a traditional Xburst MIPS Core combines with a RISC-V “Lite” core Ingenic T31 specifications: Processors XBurst 1 32-bit MIPS core clocked at 1.5GHz with Vector Deep Learning accelerator based on SIMD128, 64KB + 128KB L1/L2 Cache RISC-V independent lite core System Memory – Built-in 512Mbit (64MB) or 1Gbit (128MB) DDR2 Storage – Quad SPI flash, […]

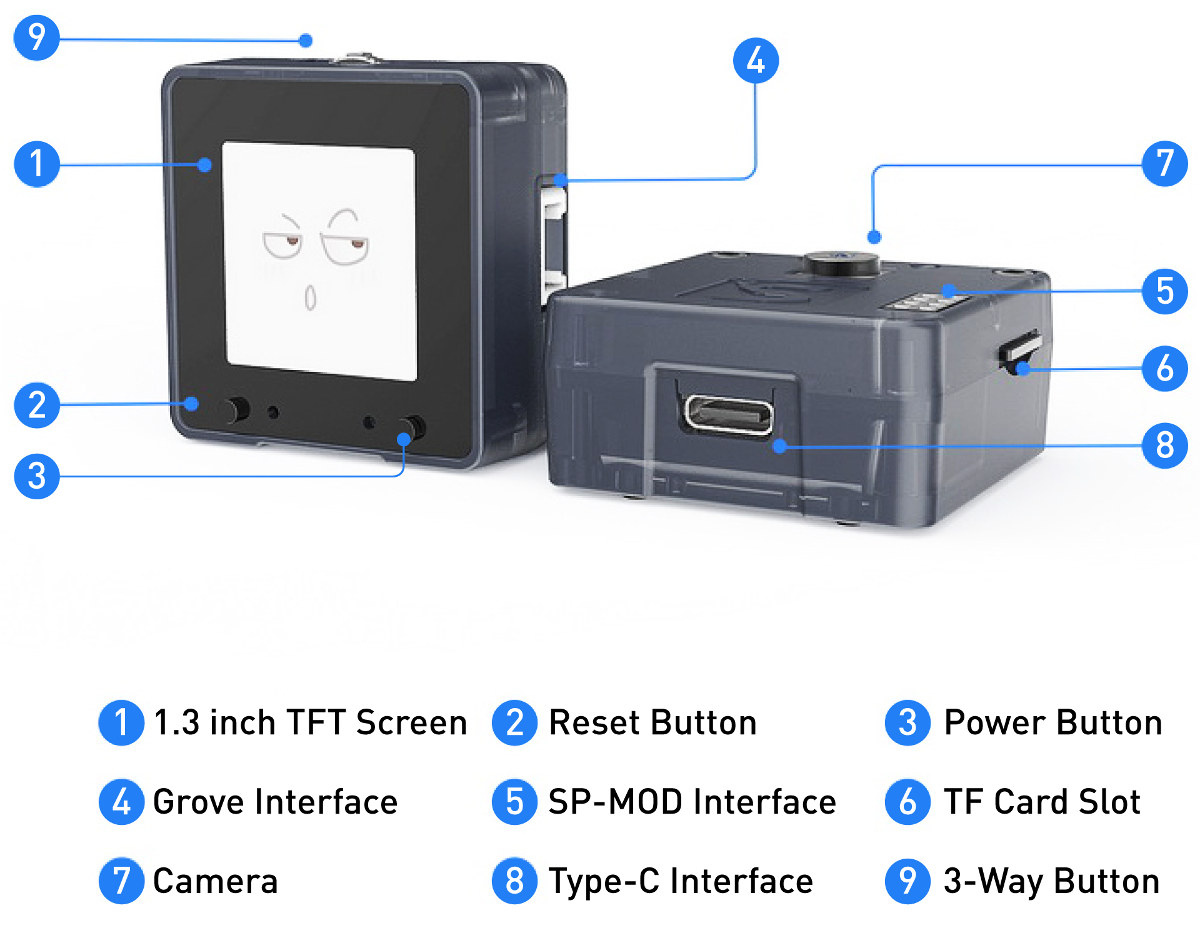

Sipeed MaixCube is a Fully Integrated AI Development Platform Powered by Kendryte K210 RISC-V SoC

Sipeed has made several boards and kits based on Kendryte K210 RISC-V processor for low-power AI workloads such as face detection or object recognition including Maixduino board and Grove AI HAT that ship with camera and display. The company has now come up with MaixCube all-in-one development platform that houses Sipeed M1 module, a display, a camera, and a battery into a plastic case that’s somewhat similar to MStack M5StickV but with a larger display, and variations in the form factor and features. Sipeed MaixCube specifications: SoC – Kendryte K210 dual-core 64-bit RISC-V processor @ 400 MHz (overclockable to 600 MHz) with FPU, 8MB SRAM, KPU AI accelerator, APU audio processor, and FFT accelerator Storage – 128 Mbit flash, MicroSD card slot Display – 1.3″ TFT screen with 240×240 resolution Camera – OV7740 sensor (VGA camera) Audio – Built-in microphone, external speakers support; ES8374 audio codec USB – 1x USB […]

Linux 5.6 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds has just announced the release of Linux 5.6 on the Linux Kernel Mailing List: So I’ll admit to vacillating between doing this 5.6 release and doing another -rc. This has a bit more changes than I’d like, but they are mostly from davem’s networking fixes pulls, and David feels comfy with them. And I looked over the diff, and none of it looks scary. It’s just slightly more than I’d have preferred at this stage – not doesn’t really seem worth delaying a release over. So about half the diff from the final week is network driver fixlets, and some minor core networking fixes. Another 20% is tooling – mostly bpf and netfilter selftests (but also some perf work). The rest is “misc” – mostly random drivers (gpio, rdma, input) and DTS files. With a smattering of fixes elsewhere (a couple of afs fixes, some vm fixes, etc). […]

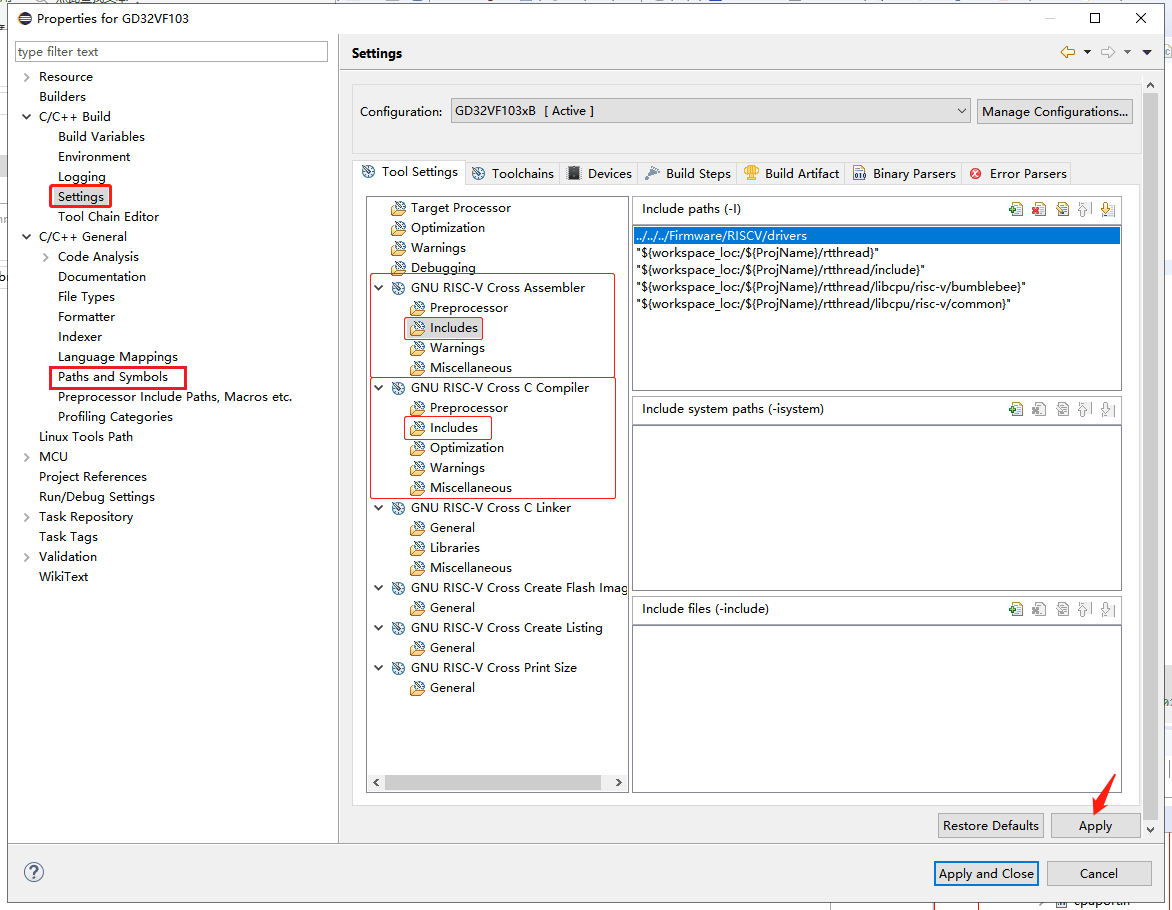

Getting Started with RT-Thread Nano RTOS on RISC-V Processors

CNXSoft: This is a guest post by RT-Thread explaining how to create your first program running on their real-time operating system using a GD32V RISC-V MCU board as an example. This article describes how to “port” RT-Thread Nano to the RISC-V architecture, using the Eclipse IDE, GCC toolchain, and a basic project for the Gigadevice GD32V103 MCU. Foreword RT-Thread is an open-source embedded real-time operating system. RT-Thread has a standard version and a Nano version. The standard version consists of a kernel layer, components and service layer, and IoT framework layer, while the Nano version has a very small footprint and refined hard real-time kernel, better suited to resource-constrained microcontroller units (MCU). The main steps for porting Nano are as follows: Prepare a basic Eclipse project and get the RT-Thread Nano source code. Add the RT-Thread Nano source code to the base project and add the corresponding header path. Modify […]