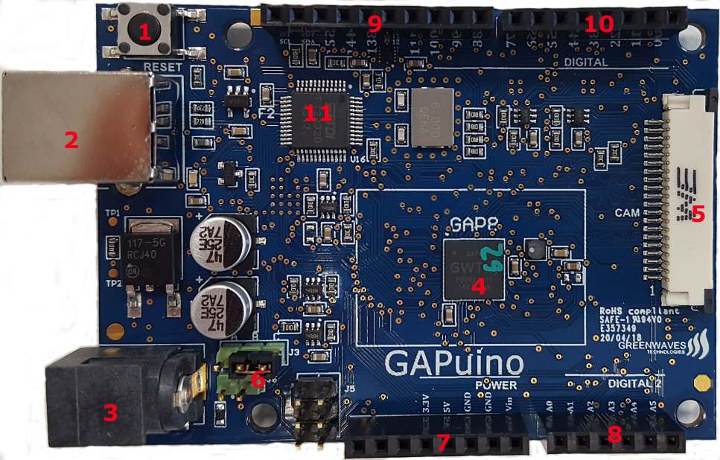

GreenWaves Technologies GAP8 multi-core RISC-V microcontroller was introduced last year for artificial intelligence (AI) at the edge at ultra-low power consumption. GAP8 AIoT SoC was shown to perform inference at 3.7mA against 60mA for the same workload on STM32F7 Arm Cortex-M7 MCU. The company has now expanded its GAP IoT application processor family with GAP9 that delivers five times lower power consumption compared to GAP8 microcontroller while enabling inference on neural networks 10 times larger. Greenwaves GAP9 will bring machine learning and signal processing capabilities to (coin cell) battery operated or energy harvesting devices such as IoT sensors in consumer and industrial markets, wearables, smart building, smart farming and so on. GAP9 is said to combine architectural enhancements with Global Foundries 22nm FDX process to achieve a peak cluster memory bandwidth of 41.6 GB/sec and up to 50 GOPS compute power while consuming only 50mW. The increased memory bandwidth (20x […]

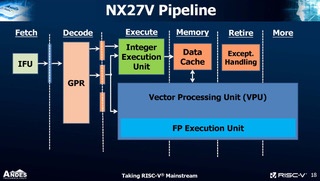

AndesCore 27-Series Linux RISC-V SoC Features a Vector Processing Unit

AndesCore 27-Series VPU Andes has developed a Linux capable RISC-V based SoC which runs on the first Vector Processing Unit (VPU) that is reported to be groundbreaking in its application ability, especially in the AI sector. The Andes 27 Series CPU has debuted in the RISC-V Summit in San Jose, to a great deal of talk in many quarters. The AndesCore 27-Series RVV The company reports that the AndesCore 27 offers a user-configurable vector-processing unit that has a scalable data size, flexible microarchitecture implementations and subsystem memory decisions open to system-level optimization. The use of the RISC-V Vector (RVV) instruction extension allows the CPU cores to deliver higher performance and versatility. The TimeTable and Offerings Andes is saying delivery of its first Andes 27 RISC-V based SoC will begin in Q1 2020. Already the earliest licensees have seen the delivery of the betas. Initial availability will center around a […]

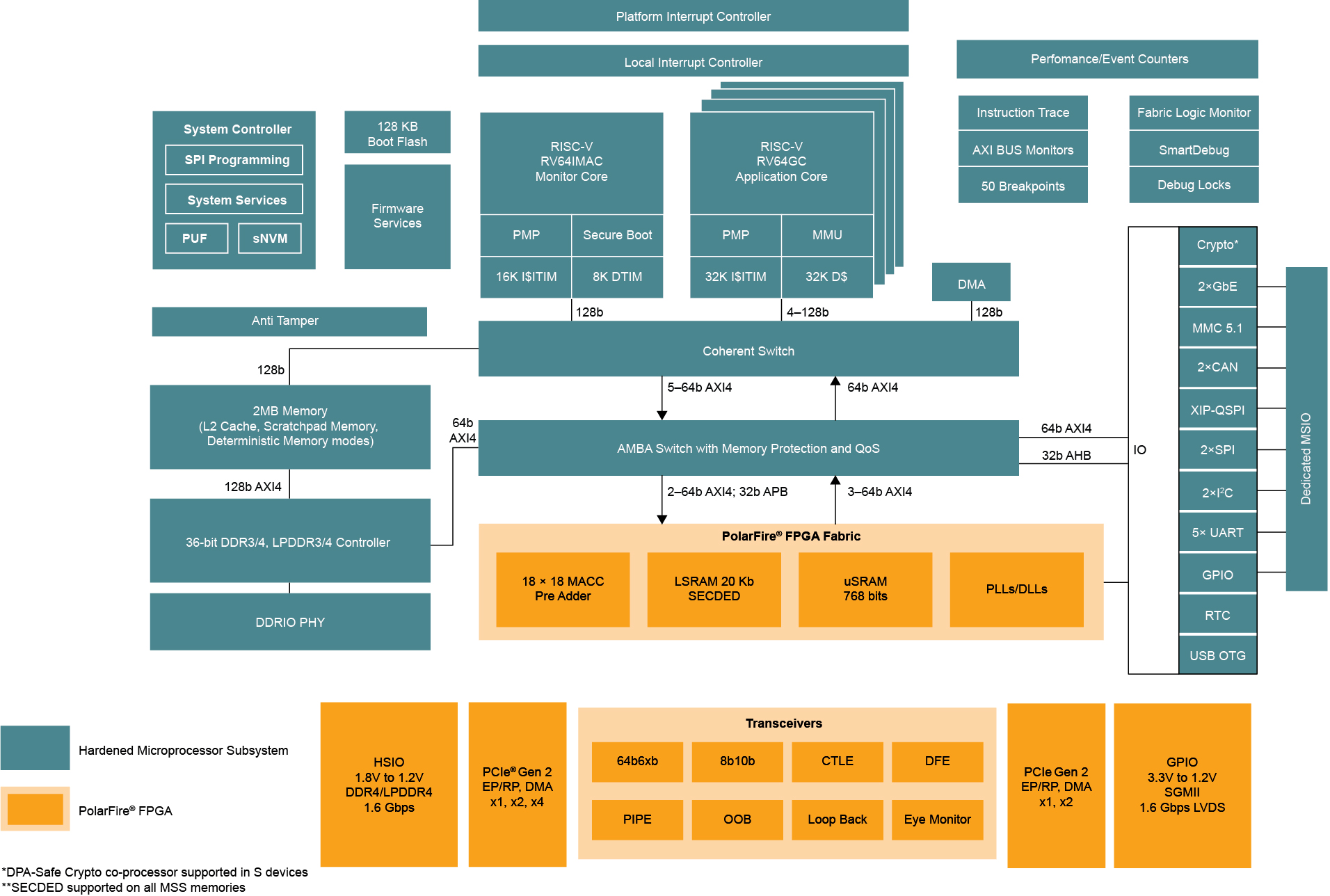

RISC-V based PolarFire SoC FPGA and Devkit Coming in Q3 2020

Microsemi unveiled PolarFire FPGA + RISC-V SoC about one year ago, but at the time, development was done on a $3,000 platform with SiFive U54 powered HiFive Unleashed board combined with an FPGA add-on board from Microsemi. I’ve now been informed that Microchip has announced its Linux-capable PolarFire FPGA+RISC-V SoC would start shipping in Q3 2020 at the RISC-V summit and that a development kit will be sold for a few hundred dollars. PolarFire SoC FPGA PolarFire SoC FPGA key features and specifications: Mid-Range FPGA optimized for Low Power High-speed serial connectivity with built-in multi-gigabit/multi-protocol transceivers from 250 Mbps to 12.7 Gbps Up to 461k logic elements consisting of a 4-input Look-Up Table (LUT) with a fracture-able D-type flip-flop Up to 31.6 Mb of RAM Power optimized transceivers Up to 1420 18 × 18 multiply-accumulate blocks with hardened pre-adders Integrated dual PCIe for up to ×4 Gen 2 Endpoint […]

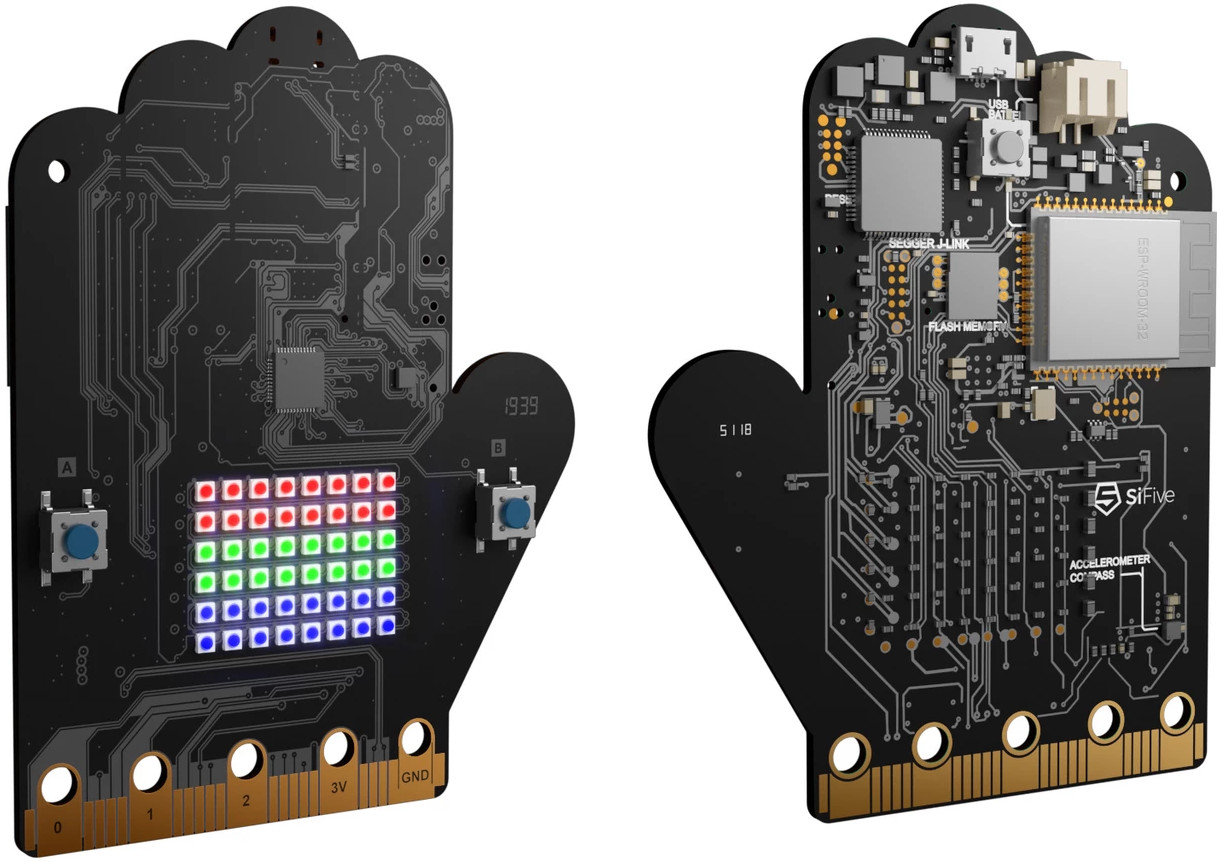

SiFive Learn Inventor is a Wireless RISC-V Development Kit Inspired by BBC Micro:bit

SiFive Learn Inventor is a RISC-V educational board partially inspired by BBC Micro:bit board with the same crocodile clip-friendly edge connector, and an LED matrix. The board is also fully qualified to work with the Amazon FreeRTOS real-time operating system. Shaped in the form of a hand, the board features SiFive FE310 RISC-V processor found in the SiFive HiFive1 board, as well as ESP-WROOM-32 WiFi + Bluetooth module. SiFive Learn Inventor specifications: SoC – SiFive FE310-G003 32-bit RISC-V (RV32IMAFC) processor @ 150 MHz with 64KB of internal SRAM Storage – 512 KB flash “Display” – 6×8 “widescreen” array of RGB LEDs with 262,000 colors each; LEDs can expand off-board onto external arrays via the edge connector Wireless Connectivity – 802.11b/g/n WiFi 4 (2.4GHz) and Bluetooth 4.2 LE via an ESP32 module (ESP-WROOM-32) USB – 1x Micro USB port for power and programming/debugging Expansion A/D Converters (four) accessed via on-board coprocessor […]

Think Silicon NEOX|V is the First RISC-V ISA based GPU

We are seeing more and more RISC-V microcontrollers and processors hitting the market, but so far they all lacked a GPU for 3D graphics acceleration. Think Silicon, the make of NEMA GPU for IoT and wearables, has now announced it will demonstrate NEOX|V GPU, the first RISC-V ISA based 3D, at the RISC-V Summit at the San Jose Convention Center, on December 10-12, in San Jose, California. NEOX|V key features: Parallel multi-core and multi-threaded architecture based on the RISC-V64GC ISA instruction set with adaptive NoC (Networks-on-Chip) Configurable from 4 to 64 cores Variety of cache sizes and thread counts organized in 1 to 16 cluster elements Variety of cluster/core configurations with compute power ranging from 12.8 to 409.6 GFLOPS at 800 MHz Support for FP16, FP32, and FP64 plus SIMD instructions Beside 3D graphics, the RISC-V GPU can also be used for machine learning, vision/video processing, and open GPGPU compute […]

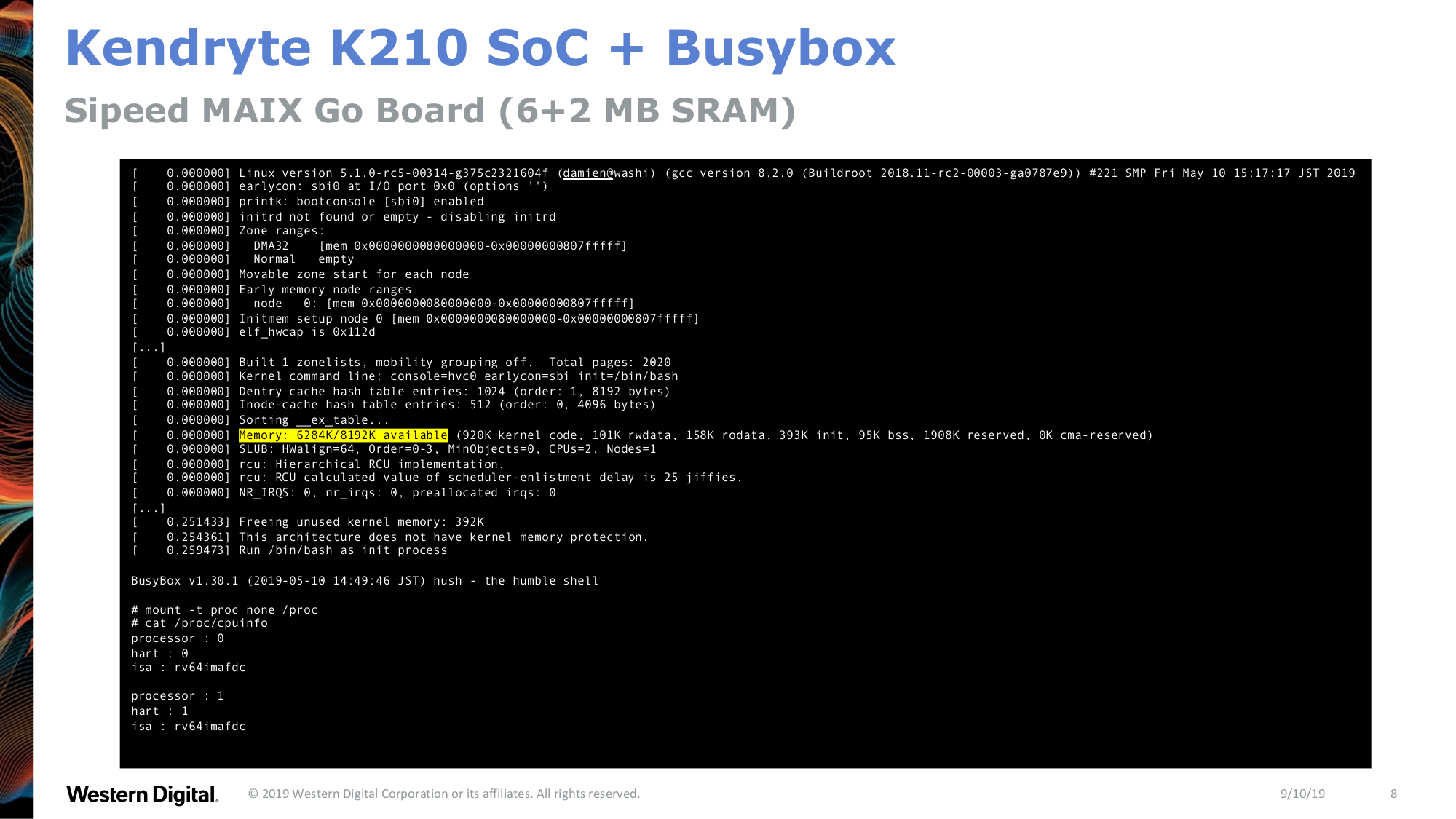

Western Digital Made RISC-V Linux & BusyBox Boot on Sipeed Maix Go Board

The other day we wrote about Getting Started with Embedded Linux on RISC-V in QEMU emulator and noted that Linux capable RISC-V hardware is currently fairly expensive. We also mentioned there was work on porting uCLinux to Kendryte K210 RISC-V processor on boards such as Sipeed Maix board. The processor only comes with 8MB RAM, and does not feature an MMU (Memory Management Unit) so what you’d be able to do on the board would be limited, and for instance, a desktop environment is clearly impossible on the platform. NOMMU support also requires some extra work, and in Linux 5.4 we saw only of the changes was “SiFive PLIC IRQ chip modifications, in preparation for M-mode Linux”. The slide above is extracted from the “RISC-V NOMMU and M-Mode Linux” presentation by Damien Le Moal, Western Digital at the Linux Plumbers Conference 2019 last September. It explains M-mode support is better […]

Linux 5.4 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds has just announced the release of Linux 5.4: Not a lot happened this last week, which is just how I like it. And as expected, most of the pull requests I got were for the 5.5 merge window, which I’ll obviously start working through tomorrow. What little there is here is mostly some networking updates (mix of network drivers and core networking), and some minor GPU driver updates. Other than that it’s a small collection of random other things all over. The appended shortlog is small enough that you might as well just scroll through it. Anyway, this obviously opens the merge window for 5.5. It’s not ideal timing with Thanksgiving week coming up, but it hopefully shouldn’t be too much of an issue. If I fall behind (not because I’m all that big of a fan of the indiscriminate and relentless turkey-killing holiday) it’s because we’ve got […]

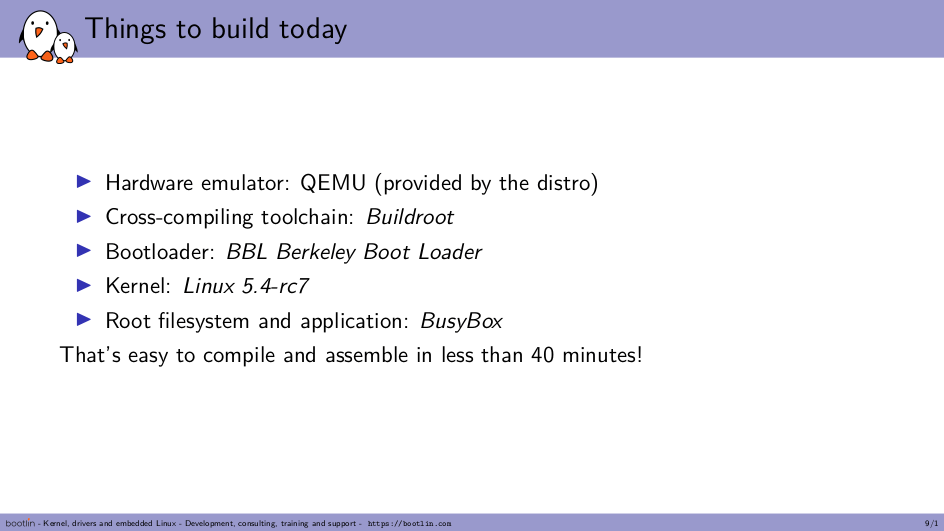

Getting Started with Embedded Linux on RISC-V in QEMU

RISC-V is getting more and more popular, but if you want to run Linux on actual hardware it’s currently fairly expensive since you either need to rely on HiFive Unleashed SBC ($999), or expensive FPGAs. Another solution is running Linux RISC-V via QEMU emulator, and I showed how to do this using BBL (Berkeley Boot Loader), Linux 4.14, and busybear rootfs. If you check the comments section of that earlier post you could also try out Fedora RISC-V images in QEMU. Bootlin has now published a presentation showing how to run embedded Linux on RISC-V in QEMU with many of the same components as in the previous instructions, but with a more up-to-date Linux kernel (5.4), and using Buildroot to build everything from scratch including the toolchain, BBL, the Linux kernel, and a Busybox based root file system. They explain each step in detail in the 45-page presentation to allow […]