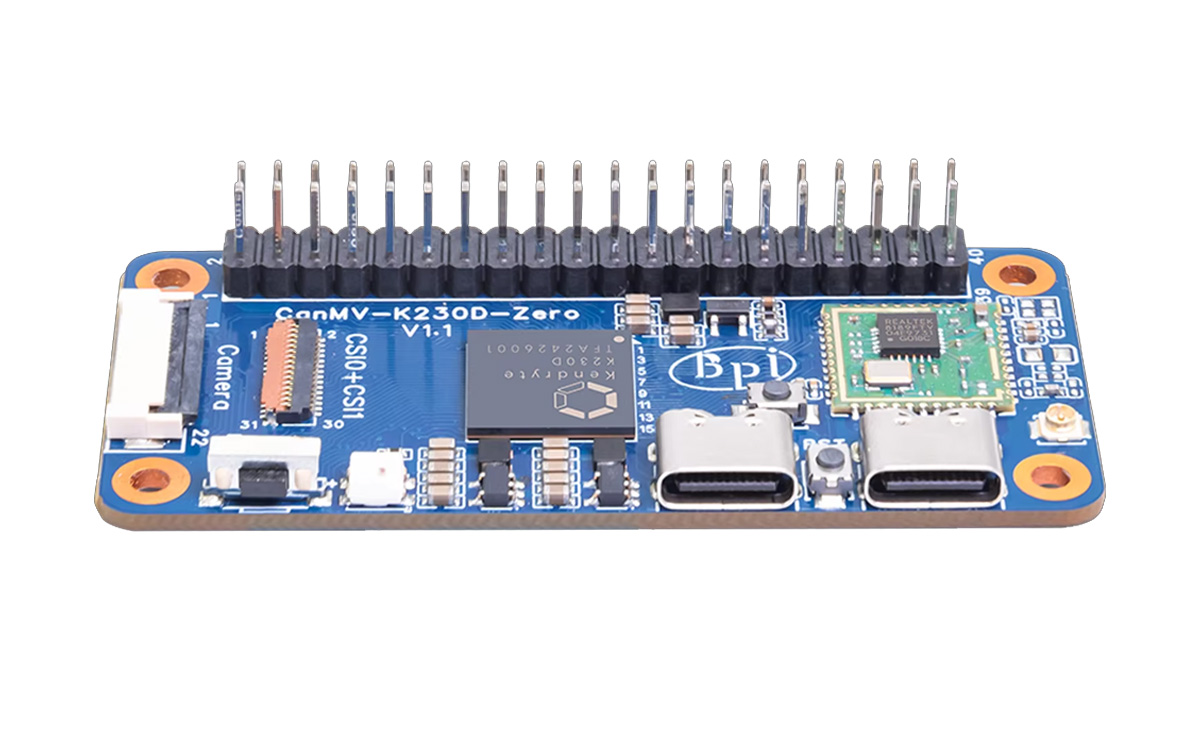

The Banana Pi BPI-CanMV-K230D-Zero is a compact and low-power single-board computer built around the Kendryte K230D dual-core XuanTie C908 RISC-V chip with an integrated third-generation Knowledge Process Unit (KPU) for AI computation. It follows the form factor of the Raspberry Pi Zero or Raspberry Pi Zero 2W board and targets IoT and ML applications. The SBC comes with 128MB of LPDDR4 RAM and uses a microSD card slot for storage. Additional features of this board include dual MIPI-CSI camera inputs for 4K video, a 40-pin GPIO header for I2C, UART, SPI, PWM, and more. Wireless features include 2.4GHz WiFi, USB 2.0 with OTG, and microphone support. These features make this SBC suitable for applications such as AI tasks such as image, video, and audio processing. Banana Pi BPI-CanMV-K230D-Zero Specifications SoC – Kendryte K230D CPU CPU1 – 64-bit RISC-V processor @ 1.6GHz with RVV 1.0 support CPU2 – 64-bit RISC-V processor […]

Qualcomm QCC730M dual-band WiFi 4 and QCC74xM WiFi 6, BLE 5.3, and 802.15.4 modules target low-power and IoT edge devices

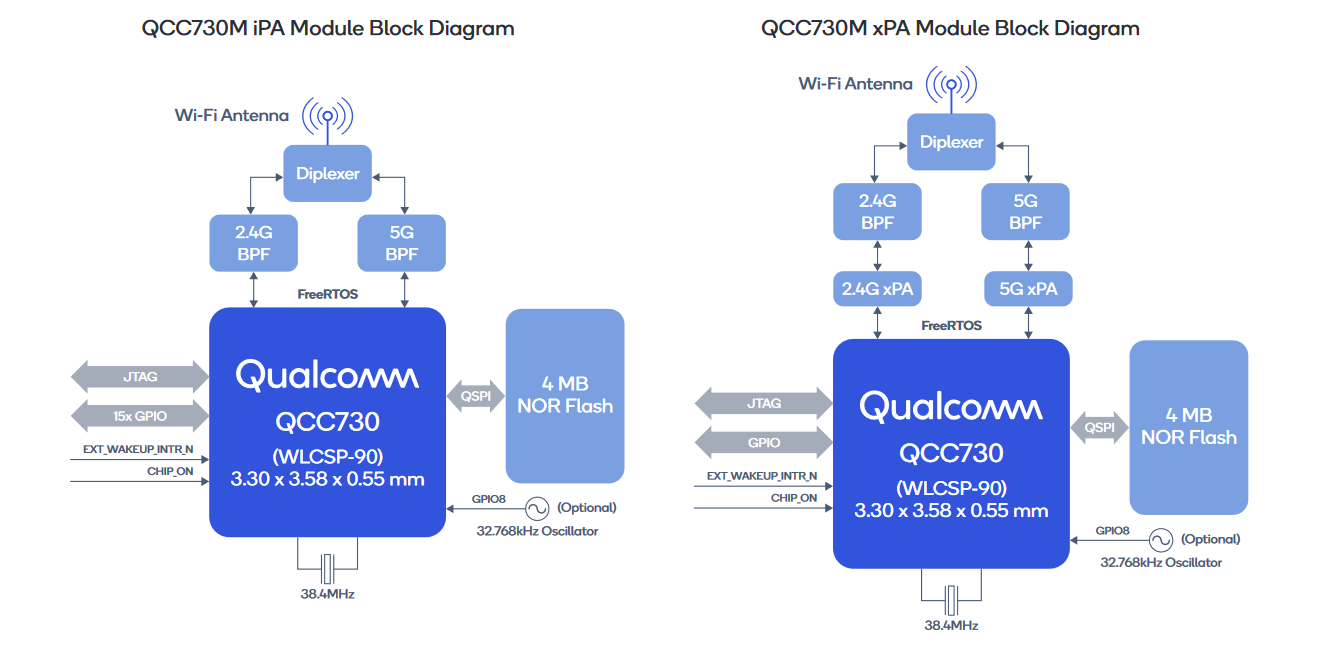

Qualcomm has added two new IoT modules to its wireless connectivity product series: the Qualcomm QCC730M ‘micro-power’ WiFi 4 module and the QCC74xM tri-radio module, with both modules designed for smart homes, smart appliances, medical devices, and industrial applications. The Qualcomm QCC730M is a dual-band, micro-power Wi-Fi 4 module with a 60MHz Arm Cortex-M4F MCU, 640kB SRAM, 1.5MB RRAM, hardware crypto accelerator, and secure boot, debug, and storage. Its low-power design is ideal for portable, battery-powered IoT devices like IP cameras, sensors, and smart locks. Based on the Qualcomm QCC730 module, it features a 36-pin LGA package with a PCB antenna or RF connector and supports up to 4MB of optional NOR flash. The Qualcomm QCC74xM is Qualcomm’s “first programmable connectivity module,” integrating a 32-bit RISC-V module, optional stacked memory (PSRAM and NOR flash), and a tri-radio chipset for WiFi 6, Bluetooth 5.3, and IEEE 802.15.4 (Thread and Zigbee). Its […]

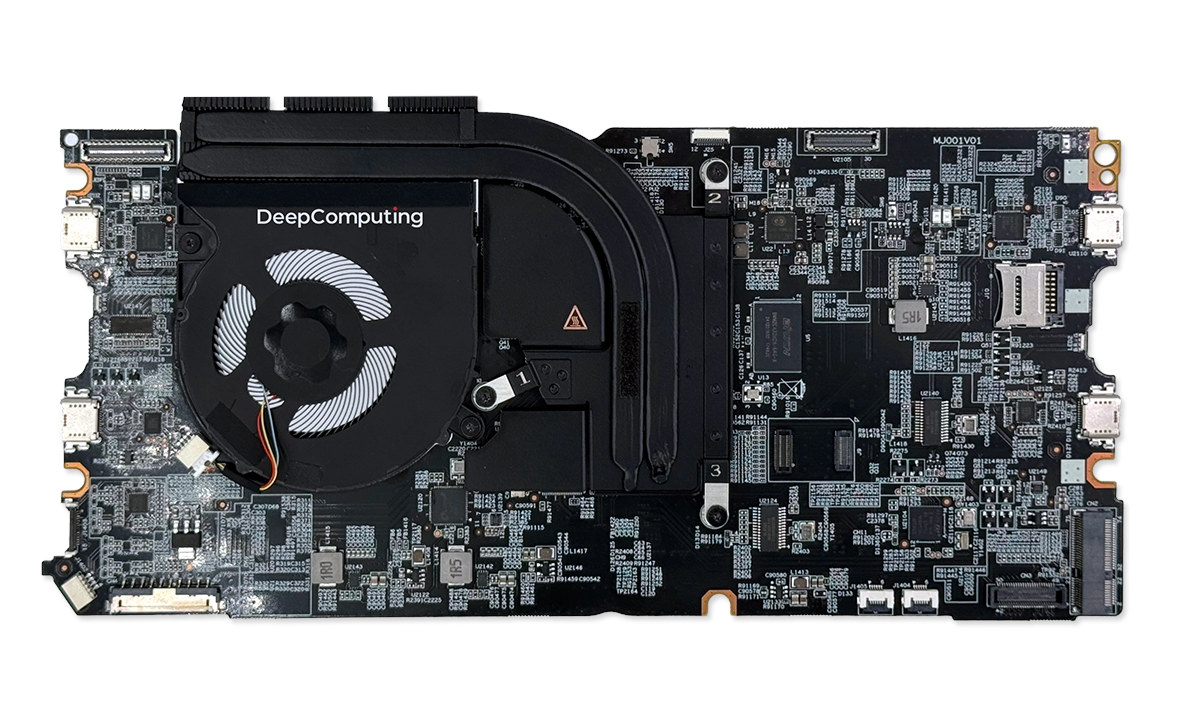

DC-ROMA RISC-V Mainboard is designed for the Framework Laptop 13 modular laptop

DeepComputing’s DC-ROMA RISC-V Mainboard is designed for the modular Framework Laptop 13 and powered by a StarFive JH7110 quad-core RISC-V processor running either Ubuntu 24.04 Desktop or Fedora 41 Linux distribution. The Framework Laptop 13 was initially offered with Intel Core i5-1135G7, Core i7-1165G7, or Core i7-1185G7 processor, but the advantage of a modular laptop is that you can replace components, and that’s exactly what the “DC-ROMA RISC-V Mainboard” does by allowing users/developers to do by switching to a less powerful RISC-V processor for software development. Framework Laptop 13 specifications with DC-ROMA RISC-V Mainboard: SoC – StarFive JH7110 CPU Quad-core 64-bit RISC-V SiFive U74 (RV64GC) processor @ up to 1.5 GHz with 32KB D-Cache, 32KB I-cache Single-core 64-bit RISC-V SiFive S7 (RV64IMAC) monitor core with 16KB I-cache, 8KB DTIM Single-core 32-bit RISC-V SiFive E24 (RV32IMFC) real-time control core with 16KB I-cache Up to 2MB L2 cache GPU – Imagination BXE-4-32 […]

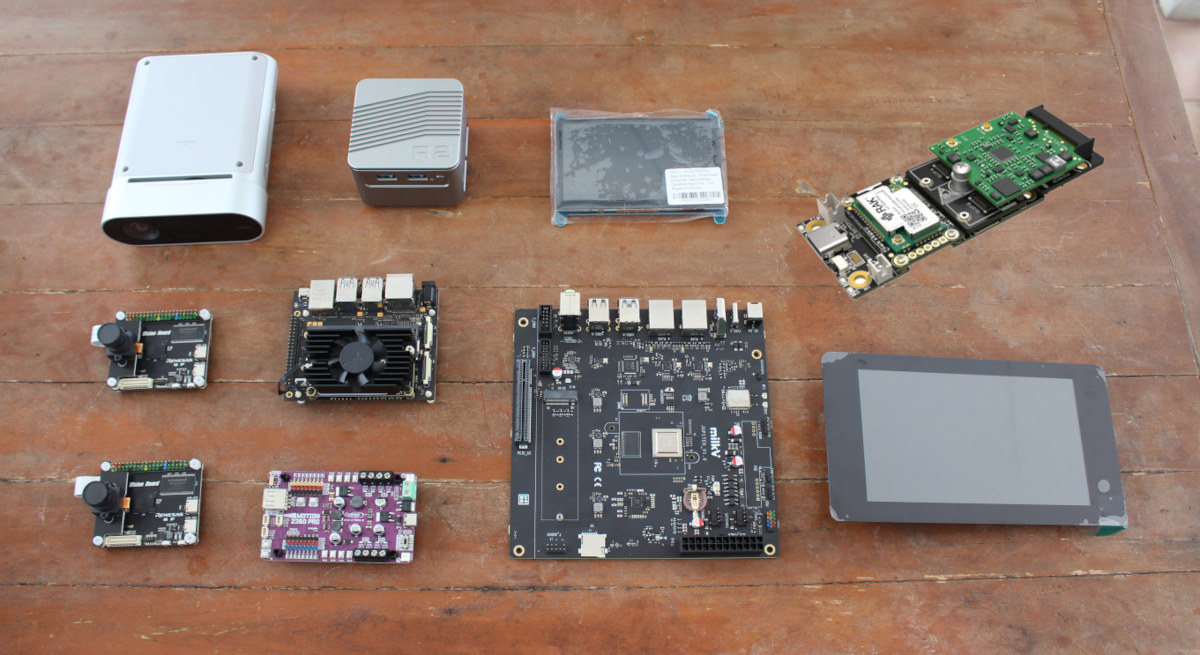

Giveaway Week 2024 winners announced!

We’re now ready to announce the winners of CNX Software’s Giveaway Week 2024. We offered some of the review samples we tested (and some we did not test) in the last year, and for the fourth year running, RAKwireless also gave away two IoT development kits shipped directly to winners. This year’s prizes also included a RISC-V motherboard, a 3D depth camera, a few Arm development boards, two touchscreen displays, and an Alder Lake-N mini PC/router. All those products can be seen in the photo, minus some accessories. You’ll find more than seven devices because we organized the third Giveaway Week on CNX Software Thailand simultaneously with four prizes. We had seven winners on CNX Software: Jupiter RISC-V mini-ITX motherboard – François-Denis, Canada Orbbec Femto mega 3D depth and 4K RGB camera – Reifu, Japan RAKwireless Blues.ONE LoRaWAN, LTE-M, and NB-IoT devkit – OldCrow, Portugal Mixtile Core 3588E development kit […]

Signaloid C0-microSD is an iCE40UP5K FPGA SoM in the microSD card form factor (Crowdfunding)

Cambridge-based hardware and cloud computing company, Signaloid has begun crowdfunding for the C0-microSD – a tiny, programmable iCE40UP5K FPGA system-on-module (SoM) in a microSD card form factor. It comes preloaded with a RISC-V softcore and users can also load custom FPGA designs onto the board. Part of the Signaloid C0-microSD’s unique appeal is its SD card form factor, which allows it to fit in unused full SD or microSD slots. This allows the implementation of FPGA-based hardware acceleration in systems without traditional expansion interfaces like PCIe M.2 slots. It can also be interfaced with as a standard SD block device and used to bring hardware-accelerated data processing to existing industrial automation, manufacturing, and robotics systems. The iCE40UP5K FPGA SoM has two main use cases: a hot-pluggable FPGA module or a hot-pluggable RISC-V co-processor module. The SD interface allows you to load custom FPGA bitstreams and applications onto the module from […]

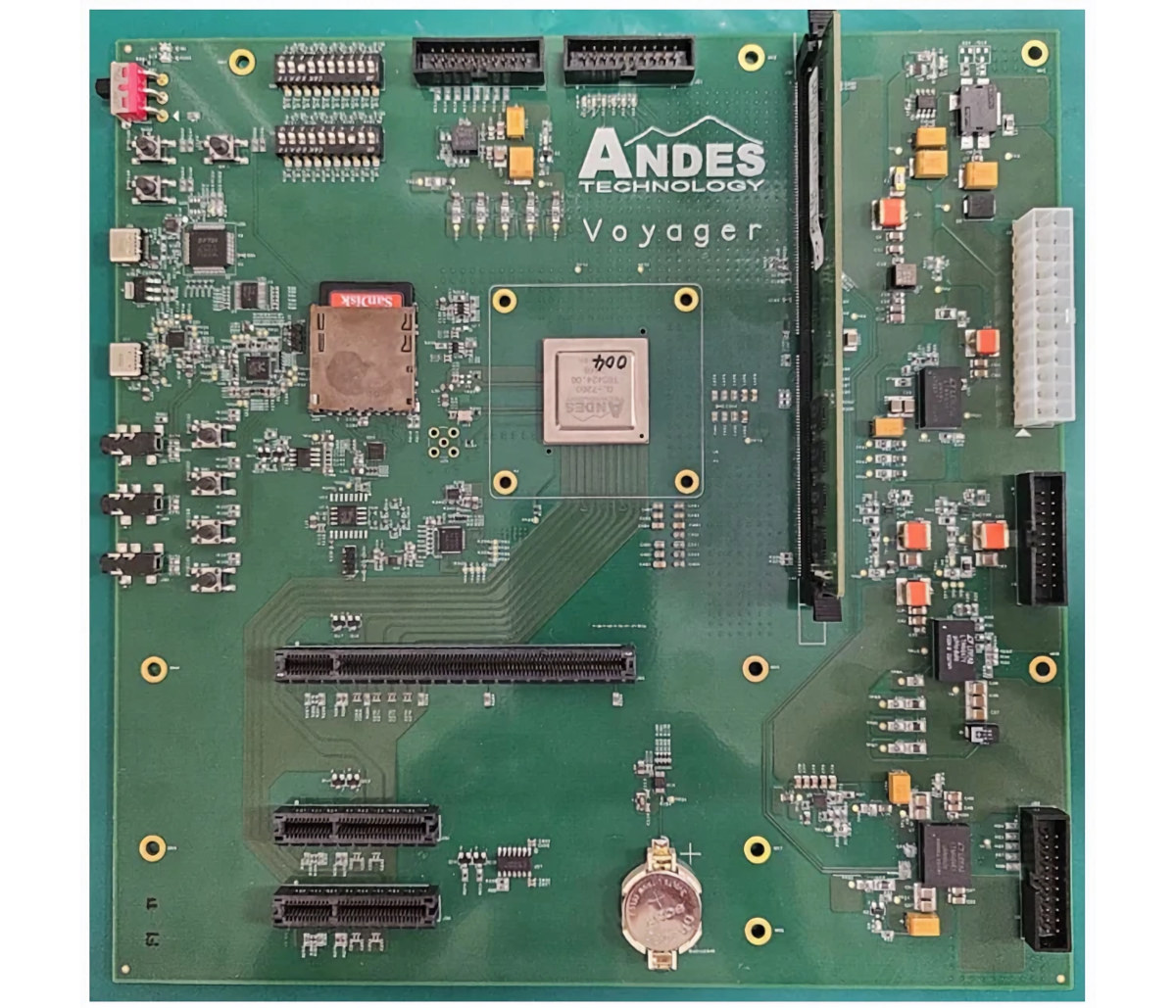

Andes QiLai quad-core AX45MP RISC-V SoC with NX27V vector processor powers micro-ATX Voyager Development Platform

Andes’ Voyager Development Platform is a micro-ATX motherboard based on the company’s QiLai SoC with four AX45MP 64-bit RISC-V cores and an NX27V vector processor optimized for AI workloads. The Voyager board supports up to 16GB of DDR4 via a UDIMM socket, features 16Mbit SPI Flash for boot code and an SD card socket, includes three PCIe Gen4 slots to connect external devices such as GPU card and SSD, as well as a JTAG debugger and USB to UART bridge for debugging during Linux software development. Andes QiLai RISC-V AI SoC Before looking at the board itself, let’s check the Andes QiLai SoC specifications: CPU cores Andes AX45MP-4C cluster 4x RV64GC 8-stage superscalar processors clocked at 1.6 GHz (worse) / 2.1 GHz (typ.) Support of MESI cache coherence protocol with Coherence Manager 32KB L1 Instruction and Date cache 2MB L2 cache I/O Coherence Port (IOCP) – Synchronous AXI4 (256 bits […]

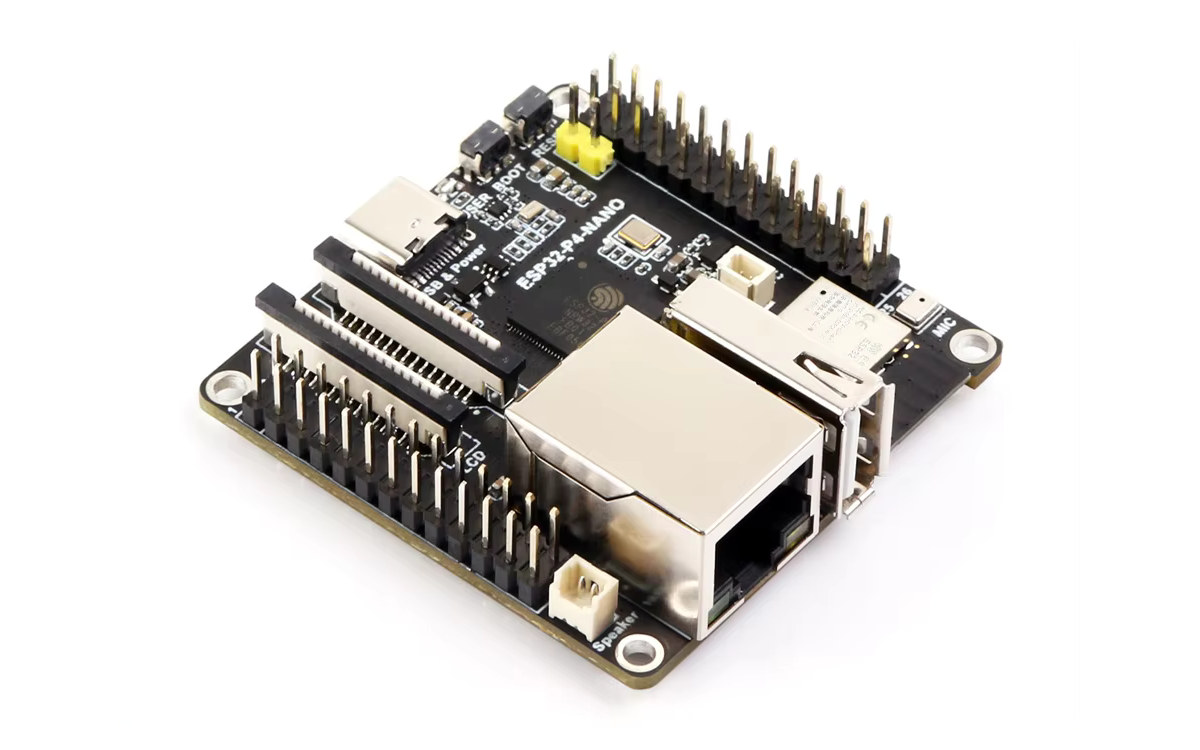

Waveshare ESP32-P4-NANO board offers Ethernet, WiFi 6, Bluetooth 5, MIPI display and camera interfaces, GPIO headers

Waveshare ESP32-P4-NANO is the first third-party ESP32-P4 RISC-V board we’ve seen and it follows the launch of the Espressif Systems’ ESP32-P4-Function-EV-Board devkit introduced this summer. While the ESP32-P4 is a general-purpose microcontroller, the ESP32-P4-NANO board still implements wireless connectivity through an ESP32-C6 WiFI 6 and Bluetooth LE 5.4 module and offers a range of interfaces such as an Ethernet RJ45 port with optional PoE, MIPI DSI and CSI interfaces, a USB Type-A OTG port, and GPIO headers for expansion. ESP32-P4-NANO specifications: Microcontroller – ESP32-P4NRW32 MCU Dual-core RISC-V microcontroller @ 400 MHz with AI instructions extension and single-precision FPU Single-RISC-V LP (Low-power) MCU core @ up to 40 MHz GPU – 2D Pixel Processing Accelerator (PPA) VPU – H.264 and JPEG codecs support Memory – 768 KB HP L2MEM, 32 KB LP SRAM, 8 KB TCM, 32MB PSRAM Storage – 128 KB HP ROM, 16 KB LP ROM Wireless module – […]

Giveaway Week 2024 – Jupiter RISC-V mini-ITX motherboard

The 11th edition of CNX Software giveaway week is underway! We have seven items to give away this time around: six review samples I will send myself and one from a company offering one of its cellular IoT development kits… The contest is open worldwide, and CNX Software Thailand is also joining the fun with four additional items available to people with an address in Thailand. The first prize of this year’s giveaway is Shenzhen MILK-V Technology’s Jupiter RISC-V mini-ITX motherboard powered by a 1.8 GHz SpacemiT K1/M1 octa-core processor, equipped with 16GB LPDDR4x, and various interfaces and features such as M.2 PCIe 2.0 x2 socket for an NVMe SSD, a 4K-capable HDMI video output, two gigabit Ethernet ports, WiFi 6 and Bluetooth 5 module, and more. I reviewed the Jupiter mini-ITX motherboard with Ubuntu-based Bianbu OS and an Auriga 6-Bay NAS mini-ITX chassis last August and the results were […]