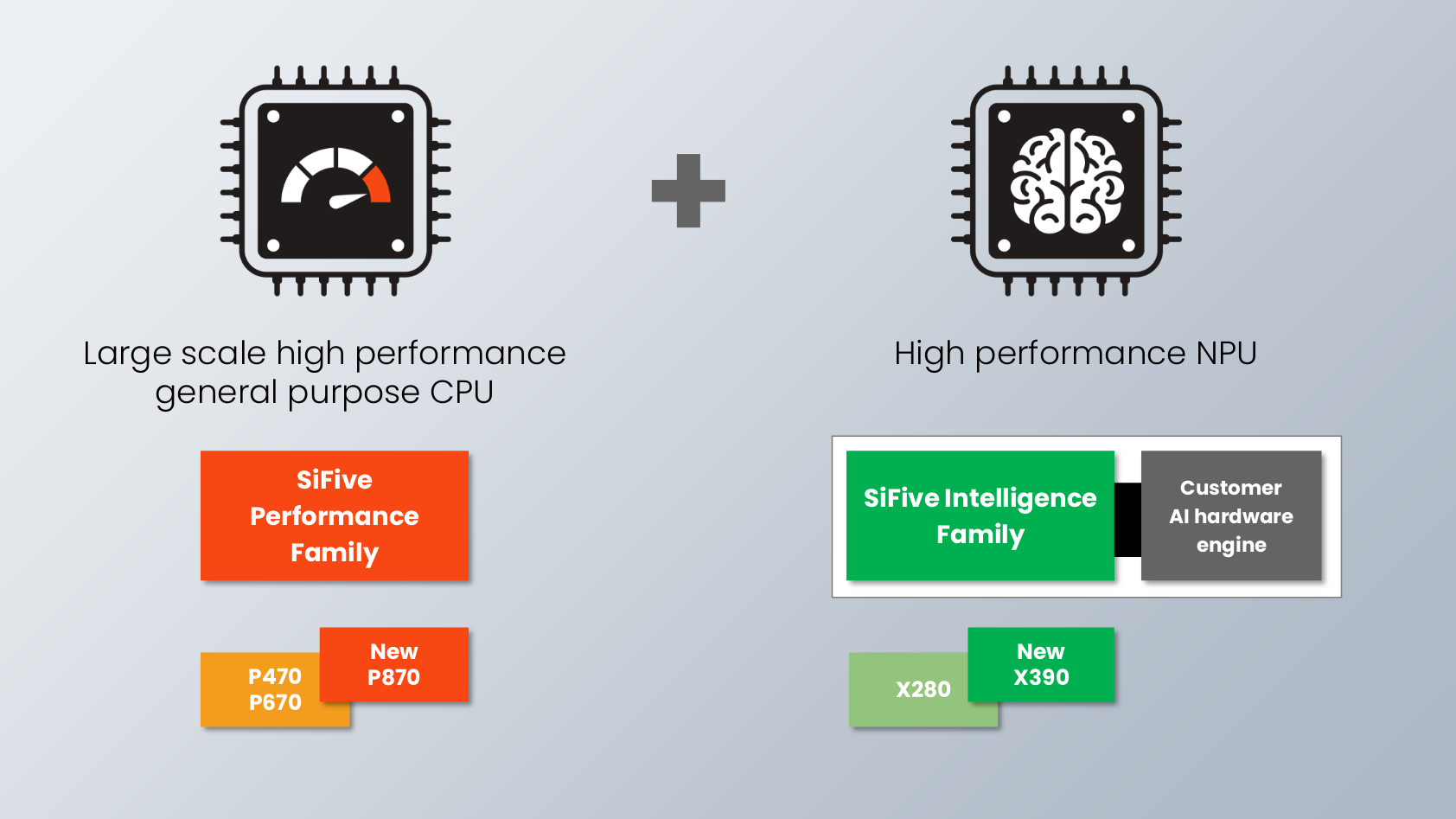

SiFive has announced two new high-performance IP blocks with the Intelligence X390 NPU and the Performance P870 RISC-V core that should find their way into SoC designed for Generative AI and ML applications. We had already covered the Performance P870 and its automotive sibling – the P870-A – from information in an earlier presentation, but the SiFive Intelligence X390 NPU is new to me and appears to be aimed at generative AI in data centers, although we will very soon be seeing companies implement generative AI at the edge in pretty powerful embedded devices. SiFive Performance P870 highlights: Full support for the RVA23 RISC-V profile specification and Vector 1.0 and Vector Crypto Six-wide, out-of-order 64-bit core Up to a 32-core cluster >12 SpecINT2k6/GHz, or a 50% peak single thread performance upgrade over the previous generation SiFive Performance P670 SiFive Features 2x 128b VLEN RVV Vector crypto and hypervisor extensions IOMMU […]

SiFive unveils P870 high-performance core, discusses future of RISC-V

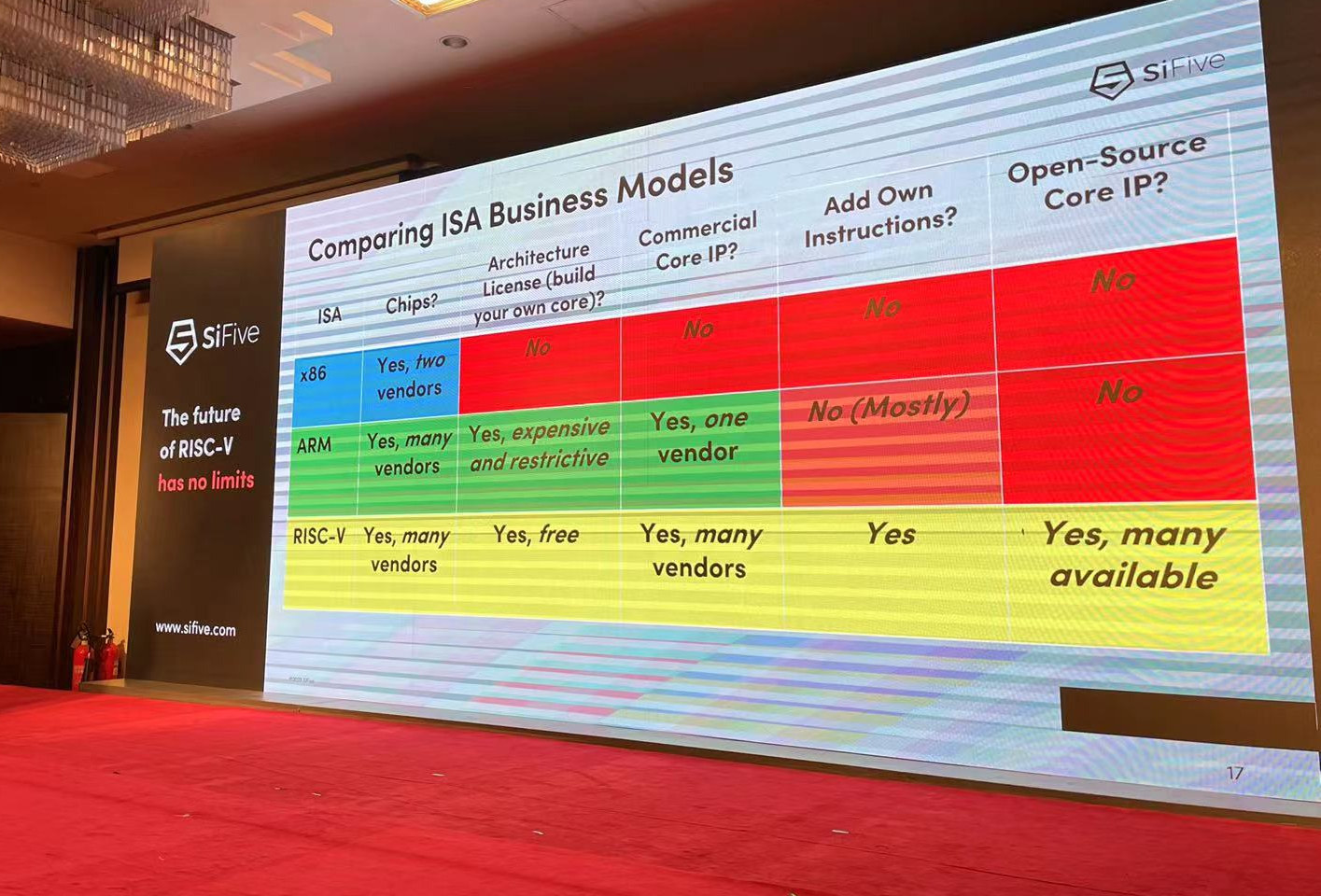

SiFive has just given a presentation at Hot Chips 2023 introducing the new high-performance P870 RISC-V core and its automotive equivalent the P870-A core, plus discussing RISC-V in general, its previous generation RISC-V cores, and what to expect going forward. SiFive has not officially announced the P870 and P870-A cores just yet, so most of the information we have from the English-speaking Internet is from ServeTheHome who managed to get some presentation slides, but this is also corroborated by various Chinese sources on Baidu and Guokr. SiFive P870 and P870-A The P870 and P870-A RISC-V cores are new cores from the SiFive Performance family compatible with the RISC-V RVA23 profile and succeeding the SiFive P670 core. The SpecINT2k6 benchmark reports 17 points per GHz on the P870 compared to 13.2 points per GHz for the P670 (comparable to the Arm Cortex-A78) or about a 29% higher performance at the same […]

HiFive Pro P550 “Horse Creek” RISC-V motherboard with 16GB RAM to launch this summer

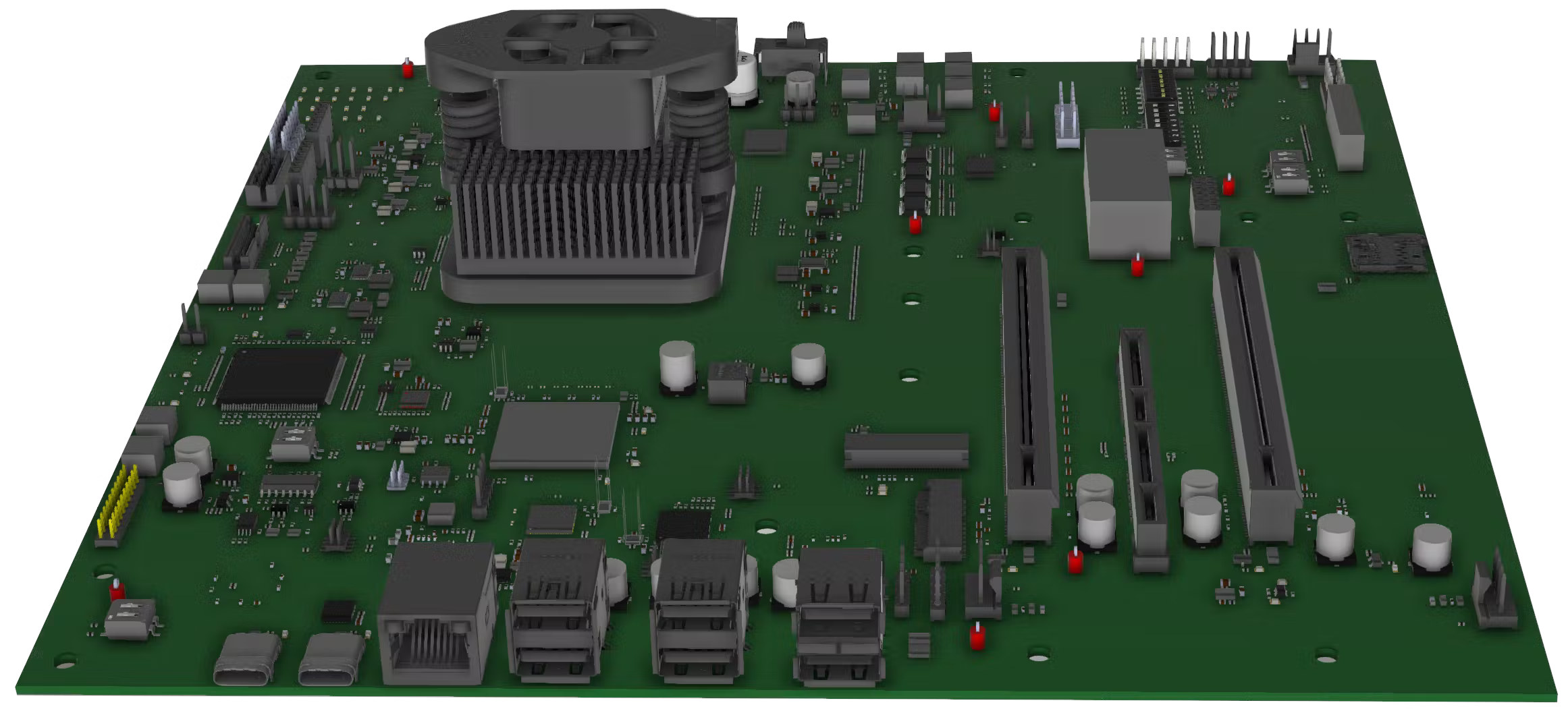

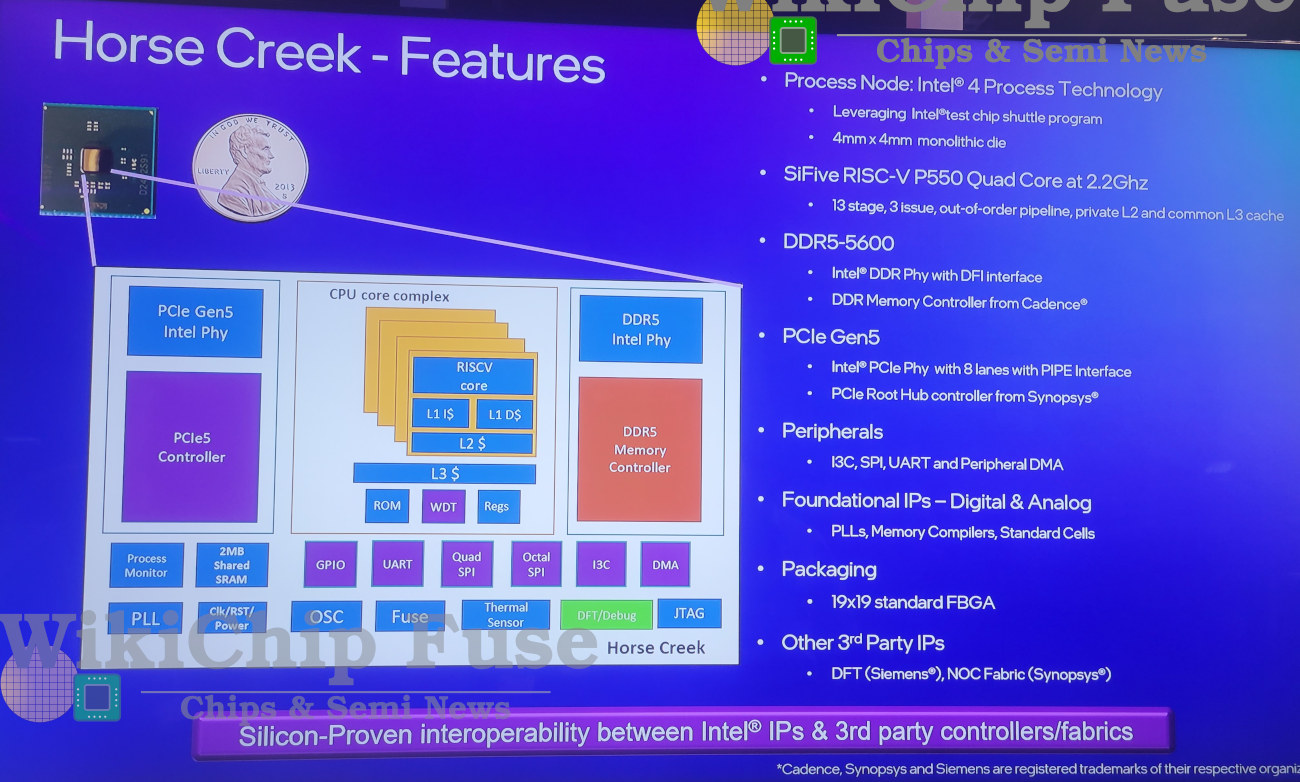

SiFive HiFive Pro P550 RISC-V motherboard based on Intel “Horse Creek” quad-core SiFive Performance P550 processor will launch this summer with 16GB DDR5 memory, two PCIe expansion slots, Gigabit Ethernet networking, USB 3.x ports, and on-board graphics. Intel Horse Creek platform was first revealed when SiFive unveiled the SiFive Performance P550 64-bit RISC-core with Cortex-A75 class performance in June 2021. The companies then demonstrated an internal Intel Horse Creek board with 8GB DDR5 and PCIe Gen5 at the Intel Innovation 2022 Developer Conference last October, and it looks like the 7nm RISC-V processor, manufactured with an Intel 4 process, will finally be available to developers this summer with the launch of the HiFive Pro P550 motherboard/development system. HiFive Pro P550 preliminary specifications: SoC – Intel-SiFive Horse Creek SoC equipped with 4x SiFive Performance P550 RV64GBC RISC-V cores with a 13-stage, 3-issue, out-of-order (OoO) pipeline GPU – “On-board graphics” [Update: […]

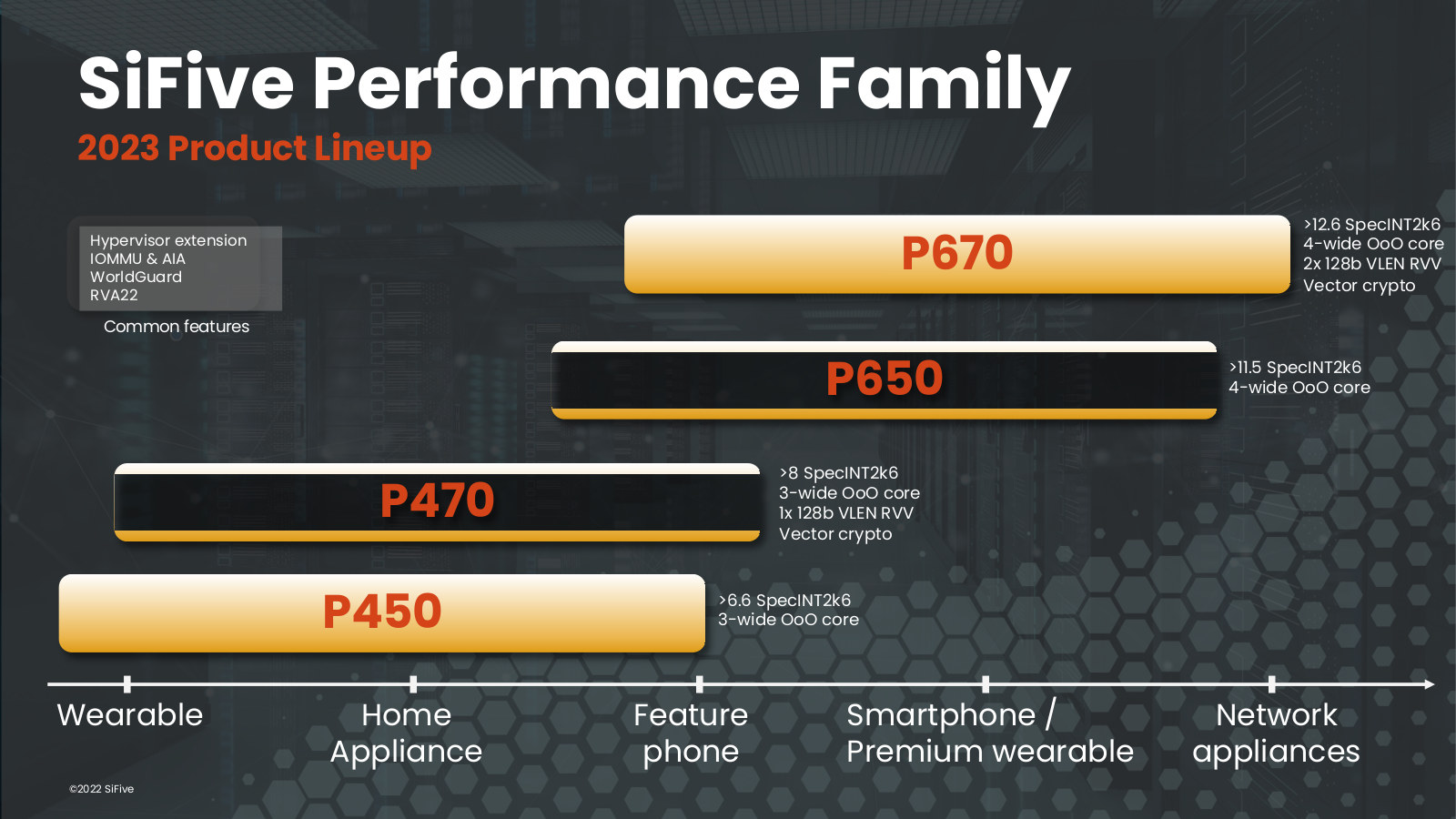

SiFive P670 and P470 RISC-V processors feature RISC-V Vector Extensions

SiFive has announced two new RISC-V Performance cores with the P670 and P470 processors with RISC-V Vector Extension for AI/ML, media and sensor processing, and designed for high volume applications such as wearables, smart home, industrial automation, AR/VR, and other consumer devices. The P670 is comparable to the Cortex-A78, and the P470 is comparable to the Cortex-A55. Both support the standardized RISC-V RVA22 profile for better OS compatibility and implement RISC-V Vector v1.0 and Vector Cryptography extensions. The SiFive Performance P470 and P670 share the following features: Full RISC-V RVA22 profile compliance Full, Out-of-Order, RISC-V Vector implementation, based on the ratified RISC-V Vector v1.0 Specification RISC-V Vector Cryptography extensions SiFive WorldGuard system security Support for virtualization, including a separate IOMMU for accelerating virtualized device IO Advanced Interrupt Architecture (AIA) compliant interrupt controller with better support for Message Signal Interrupts (MSI) and virtualization Enhanced scalability with fully coherent multi-core, multi-cluster, with […]

Intel Horse Creek platform showcased with SiFive P550 RISC-V CPU, 8GB DDR5, PCIe Gen5

When SiFive introduced its Performance P550 64-bit RISC-V processor in 2021, we were told that Intel would use it in the Horse Creek platform with “leading-edge interface IP such as DDR and PCIe” and manufactured with Intel’s 7nm process. We now have more details about the Horse Creek platform, as a development board was showcased for the first time in public at the Intel Innovation 2022 Developer Conference, and according to a report by Wikichip, the Cortex-A75 class quad-core RISC-V processor runs at up to 2.2 GHz, supports DDR5-5600 memory and eight PCIe 5.0 lanes, and was taped out with Intel 4 process. Horse Creek platform specifications: CPU – SiFive P500 quad-core RISC-V processor @ up to 2.2 GHz with a 13-stage, 3-issue, out-of-order (OoO) pipeline, private L2 cache, and common L3 cache Memory – DDR5-5600 interface PCIe – PCIe Gen5 through Intel’s PCIe PHY with 8 lanes, Synopsys PCIe […]

SiFive unveils Automotive E6-A, X280-A, and S7-A RISC-V processors

RISC-V is coming to your car too, with the introduction of SiFive Automotive E6-A, X280-A, and S7-A RISC-V processors designed for automotive applications such as infotainment, cockpit, connectivity, ADAS, and electrification. Those are built on the existing SiFive Essential 6-series E6 32-bit real-time cores, SiFive Intelligence X280 64-bit RISC-V processor with AI extensions, and SiFive S7 64-bit real-time cores (equivalent to Cortex-R7/R8), but adds safety, security, and performance required by the automotive market such as ASIL compliance. Each new core targets specific applications within a vehicle: The SiFive E6-A series will be found in system control boards, hardware security modules (HSMs) and safety islands, as well as standalone in microcontrollers. The SiFive S7-A 64-bit real-time core is said to be suited to the needs of SoCs with performant safety islands, requiring both low latency interrupt support and the same 64-bit memory space as the main application CPUs. The SiFive X280-A […]

Linux 5.18 release – Main changes, Arm, RISC-V, and MIPS architectures

Linux 5.18 is out! Linus Torvalds has just announced the release on lkml: No unexpected nasty surprises this last week, so here we go with the 5.18 release right on schedule. That obviously means that the merge window for 5.19 will open tomorrow, and I already have a few pull requests pending. Thank you everybody. I’d still like people to run boring old plain 5.18 just to check, before we start with the excitement of all the new features for the merge window. The full shortlog for the last week is below, and nothing really odd stands out. The diffstat looks a bit funny – unusually we have parsic architecture patches being a big part of it due to some last-minute cache flushing fixes, but that is probably more indicative of everything else being pretty small. So outside of the parisc fixes, there’s random driver updates (mellanox mlx5 stands out, […]

Intel to invest $1 billion in foundry innovation, becomes RISC-V International member

Intel has just announced a $1 billion fund to support companies bringing innovations and new technologies to the foundry ecosystem. The company says the fund will prioritize investments in “capabilities that accelerate foundry customers’ time to market – spanning intellectual property (IP), software tools, innovative chip architectures, and advanced packaging technologies.” What’s interesting is that it does not only cover x86 architecture but also Arm and RISC-V, with a focus on the latter, as Intel has just become a Premier member of RISC-V International, and partnered with several companies offering RISC-V solutions including Andes Technology, Esperanto Technologies, SiFive, and Ventana Micro Systems. Intel’s Open Chiplet Platform Part of the investment will go to the Open Chiplet Platform offering a modular approach to chip design through chiplets with each block/chiplet customized for a particular function. This will allow designers to select the best IP and process technologies for a particular SoC. […]