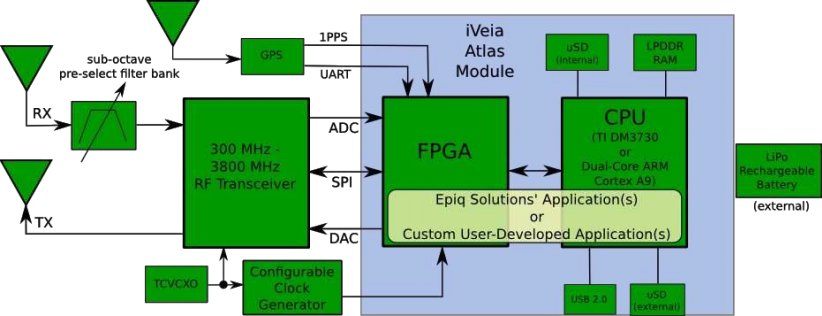

Epiq Solutions recently announced the Matchstiq, a software defined radio (SDR) combining a broadband RF transceiver with CPU (TI DM3730)/FPGA (Xilinx Spartan-6) processing running Linux 2.6.35. The device offers a complete stand-alone software-defined radio solution with flexibility at a fraction of the size/weight/power consumption of similar products.

Epiq Solutions also provides a library of ready-to-run specialty software applications that allows the Matchstiq platform to be immediately used to solve challenging signal processing requirements.

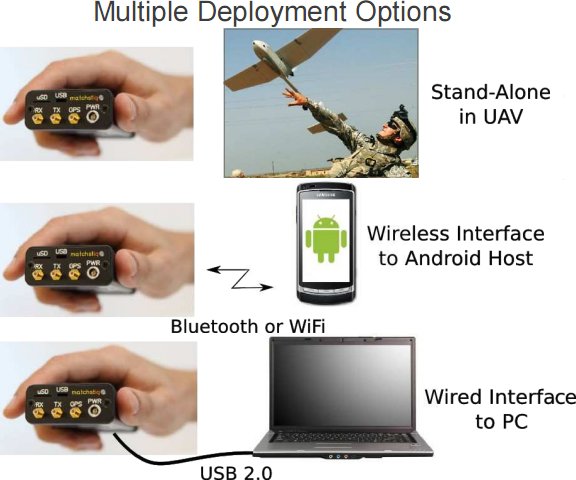

The device can be deployed as stand-alone device in unmanned aerial vehicle (UAV), as a wireless interface to an (Android) host via Bluetooth or Wi-Fi or as wired interface to a PC via USB.

The key features include:

- Integrated CPU (TI DM3730) /FPGA (Xilinx Spartan-6) for signal processing applications

- Single RF transceiver covering 300 MHz to 3.8 GHz

- Supports RF channel bandwidths up to 28 MHz

- Integrated GPS receiver with 1PPS

- Run-time loadable/executable software applications

- Full suite of specialty applications available

- SDK available for custom application development

- uSD provides up to 32 GB of on-board data and application storage

- USB interface to host for system access

- Size: 2.2″ x 4.6″ x 0.9″ (5.58cm x 11.68cm x 2.28cm)

- Power: <3 W (typical)

- Optional external rechargeable battery

The FPGA/CPU module is actually the iVeia Atlas-I-LPe Processing Module. This module uses OMAP3530 or DM3730 processor and Xilinx Spartan 6LX16 FPGA. It comes with 512 MB LPDDR RAM by default (upgradable to 1GB), an onboard SD card (up to 16GB) and runs Linux 2.6 with Real-Time Modifications. iVeai says it will also support Android in the near future.

Here are the technical specifications of the device:

| RF Specification | |

| Receiver | |

| RF Input | SMB (50 Ω) |

| Architecture | Zero-IF (direct conversion) |

| Tuning range | 300 MHz to 3800 MHz |

| Tuning step-size | 1 kHz |

| Tuning time | <2 mS |

| Pre-select filter bank | sub-octave from 300 MHz to 3800 MHz |

| Typical noise figure | 8 dB |

| Typical IIP3 | -10 dBm |

| RF gain control range | 0 to 25 dB |

| Baseband gain control range | 0 to 30 dB |

| Baseband configurable low-pass filter | 0.75 MHz to 14 MHz (RF channel bandwidths from 1.5 MHz to 28 MHz) |

| Typical I/Q balance | >40 dB (with digital correction) |

| A/D converter sample rate | Up to 40 MHz with 1 Hz resolution |

| A/D converter sample width | 12 bits |

| Power consumption (stand-alone) | 1.1 W |

| ESD protection at RF input | 20 kV (human body model) |

| Max safe RF level at RF input (at max gain) | -5 dBm |

| Transmitter | |

| RF Output | SMB (50 Ω) |

| Architecture. | Zero-IF (direct conversion) |

| Tx tuning range | 300 MHz to 3800 MHz |

| Tuning step-size | 1 kHz |

| Tuning time | <2 mS |

| Baseband transmit gain control range | 0 to 31 dB |

| Baseband configurable low-pass filter | 0.75 MHz to 14 MHz (RF channel bandwidths from 1.5 MHz to 28 MHz) |

| RF transmit gain control range | 0 to 25 dB |

| Max Tx output power | +10 dBm |

| D/A converter sample rate | Up to 40 MHz with 1 Hz resolution |

| D/A converter sample width | 12 bits |

| Power consumption (stand-alone) | 1.0 W (@ 0 dBm power output) |

| Digital Specification | |

| CPU/DSP | TI DM3730 @ 1 GHz (ARMv7/Cortex™ A8 + TI C64x DSP) (ARM® Cortex™ A-9 Dual Core in 2Q 2012) |

| FPGA | Xilinx® Spartan®-6 LX45 (Xilinx® Zynq™-7000 in 2Q2012) |

| Non-volatile memory | 32 GB (microSDHC card for storage and applications) |

| RAM | 512 MB LPDDR2 |

| Operating System | Linux 2.6.35 kernel (with real-time extensions) |

| System Interface | microUSB 2.0 OTG (host or device) |

| Typical Power Consumption (stand-alone) | 2 W (dependent on FPGA usage) |

| GPS Specification | |

| Number of Channels | 51 (acquisition), 14 (tracking) |

| Sensitivity | -161 dBm |

| Accuracy | <2.5 meters |

| Hot Start | 1 second |

| Cold Start | 29 seconds |

| RF Input | SMB |

| Support for active antennas | Yes (3V bias default, additional bias voltages possible) |

| Data Interface | NMEA sentences over UART (9600 baud, N81) 1 PPS signal GPS Lock LED indicator |

| Typical power consumption (stand-alone) | 150 mW (acquisition), 84 mW (tracking) |

| System Reference Clock Specification | |

| Type | Temperature Compensated, Voltage Controlled Crystal Oscillator (TCVCXO) |

| Frequency | 30.72 MHz |

| Frequency Accuracy | ±0.5 ppm @ 25° C, ±2 ppm from -30° C to +85° C |

| Frequency Warping | ±8 ppm over range of 0.5 VDC to 2.5 VDC (using on-board D/A converter) |

| Frequency Aging | ±1.0 ppm (first year @ 25° C) |

| Alternate Clock Input Option | External clock in via U.FL connector |

| Temperature Sensor Specification | |

| Temperature Sensing Range | -55° C to +125° C |

| Temperature Accuracy | ±2° C from -25° C to +85° C ±3° C from -55° C to +125° C |

| Power Input Specification | |

| Power Input Connector | Lemo EGG.00.302.CLL (locking) |

| Power Input Voltage Range | 6V to 28V DC |

| Physical Specification | |

| Dimensions | 2.2″ x 4.6″ x 0.9″ |

| Weight | 4 oz |

| Operating Temperature | 0° C to +50° C (without external cooling) |

| Battery Specification (Optional) | |

| Dimensions | 2.2″ x 2.2″ x 0.9″ |

| Chemistry | Lithium Polymer (Rechargeable) |

| Capacity | 7.4V @ 1000 mAH |

| Runtime (Typical) | 2 Hours |

Matchstiq SDR will ship in December 2011 and it will cost 4,500 USD. You can contact to company to pre-order the device. Epiq solutions also sells the following accompanying kits at undisclosed prices:

- Matchstiq™ Software Development Kit (SDK) – Matchstiq + JTAG breakout board + SDK

- Matchstiq™ Platform Development Kit (PDK) – Matchstiq + JTAG breakout board + SDK + FPGA DK

- Matchstiq™ Battery Pack

Further information is available on Matchstiq page.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress