Microchip PIC32CZ CA is a new family of Arm Cortex-M7 microcontrollers with the PIC32CZ CA90 integrating a Hardware Security Module (HSM), and the PIC32CZ CA80 doing without one. The HSM in the PIC32CZ CA90 provides advanced security for industrial and consumer applications and operates as a secure subsystem with a separate MCU on board that runs the firmware and security features including hardware secure boot, key storage, cryptographic acceleration, true random number generator, and more. Microchip PIC32CZ CA key features and specifications: MCU core – Arm Cortex-M7 clocked at up to 300 MHz with 16KB ECC-protected instruction and data L1 cache, up to 256Kb of Tightly Coupled Memory (TCM): 128 KB each of ECC-protected Instruction and Data TCM Memory 512KB or 1MB SRAM with ECC, 8KB SRAM for backup mode 2MB, 4MB, or 8MB flash 2x 80KB boot flash memory 16-bit external bus interface (EBI) – Static memory controller for […]

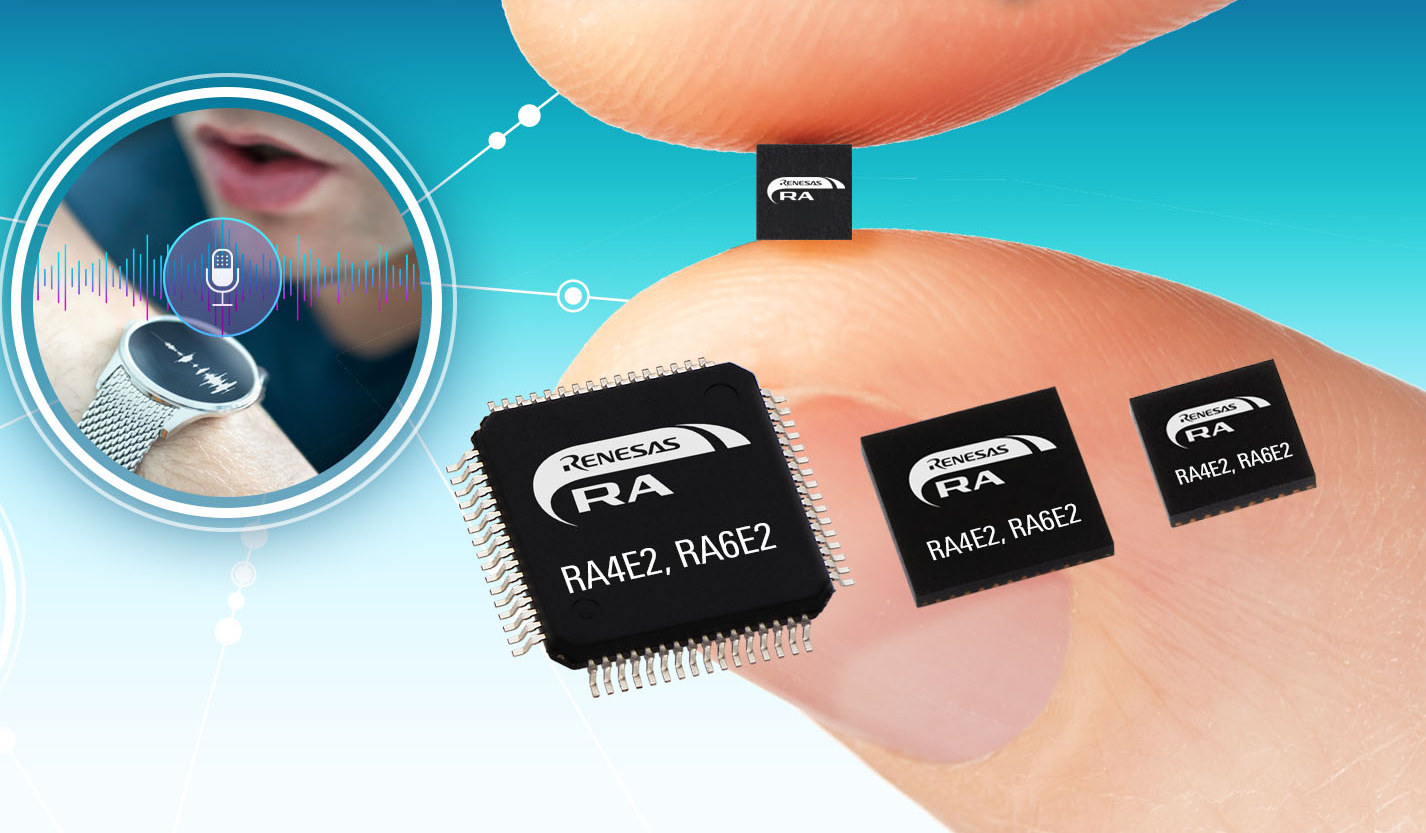

Renesas introduces 100 MHz RA4E2 and 200 MHz RA6E2 Arm Cortex-M33 MCUs for wearables, sensors, appliances

Renesas Electronics has added two new groups to its 32-bit RA family of microcontrollers (MCUs) with the 100 MHz RA4E2 and 200 MHz RA6E2 Arm Cortex-M33 microcontrollers designed for “high-performance applications” in small packages such as sensing, gaming, wearables, and appliances. The new microcontrollers are equipped with 40 KB SRAM, 128 KB or 256 KB flash, and integrate various on-chip interfaces such as CAN FD, USB, QSPI, SSI, and I3C interfaces to offer an easy upgrade path for products based on other members of the Renesas RA Family. Renesas RA4E2 MCU group Both the RA4E2 and the RA6E2 are the most cost-effective microcontroller groups of the RA family with integrated CAN FD, with the RA4E2 group especially well-suited to cost-sensitive applications and other systems requiring relatively high performance, low power consumption, and/or small package size. RA4E2 key features: CPU – Arm Cortex-M33 core with TrustZone @ up to 100 MHz […]

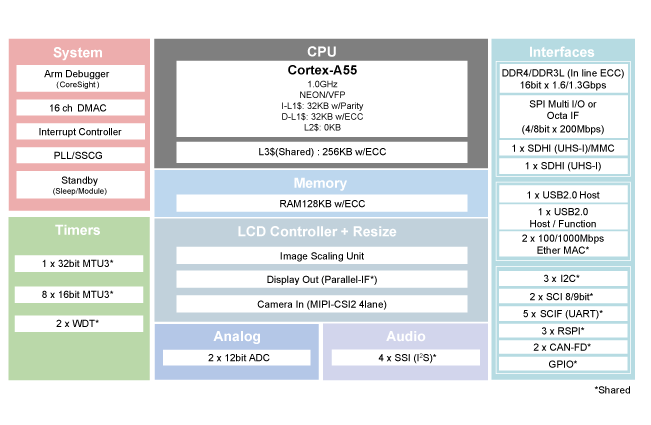

Renesas RZ/A3UL Cortex-A55 CPU runs RTOS for HMI with quick startup times

Renesas RZ/A3UL is a single-core Cortex-A55 processor clocked at up to 1 GHz designed to run FreeRTOS or Azure RTOS on high-definition (1280×800) HMI solutions requiring quick startup times such as industrial equipment, home appliances, office automation equipment, audio equipment, and POS terminals. The new RZ/A3UL processor family has the same peripheral functions and package pin assignments as the RZ/G2UL (Arm Cortex-A55/M33) and RZ/Five (RISC-V) families targeting Linux-based HMI applications. Renesas also designed a SMARC 2.1 compliant System-on-Module (SoM) based on the Renesas RZ/A3UL microprocessor to speed up time to market. Renesas RS/A3UL specifications: CPU – Single-core Arm Cortex-A55 processor @ up to 1.0 GHz with 32KB I-cache with parity, 32KB D-cache with ECC, 256KB L3 cache with ECC Internal Memory – 128KB SRAM with ECC Memory & Storage I/F 16-bit DDR4-1600 or DDR3L-1333 memory interfaces with in-line ECC; up to 4GB RAM Octal Peripheral Interface (OPI) for flash or […]

Linaro Connect San Diego 2019 Schedule – IoT, AI, Optimizations, Compilers and More

Linaro has recently released the full schedule of Linaro Connect San Diego 2019 that will take place on September 23-27. Even if you can’t attend, it’s always interested to check out the schedule to find out what interesting work is done on Arm Linux, Zephyr OS, and so on. So I’ve created my own virtual schedule with some of the most relevant and interesting sessions of the five-day event. Monday, September 23 14:00 – 14:25 – SAN19-101 Thermal Governors: How to pick the right one by Keerthy Jagadeesh, Software Engineer, Texas Instruments With higher Gigahertz and multiple cores packed in a SoC the need for thermal management for Arm based SoCs gets more and more critical. Thermal governors that define the policy for thermal management play a pivotal role in ensuring thermal safety of the device. Choosing the right one ensures the device performs optimally with in the thermal budget. […]

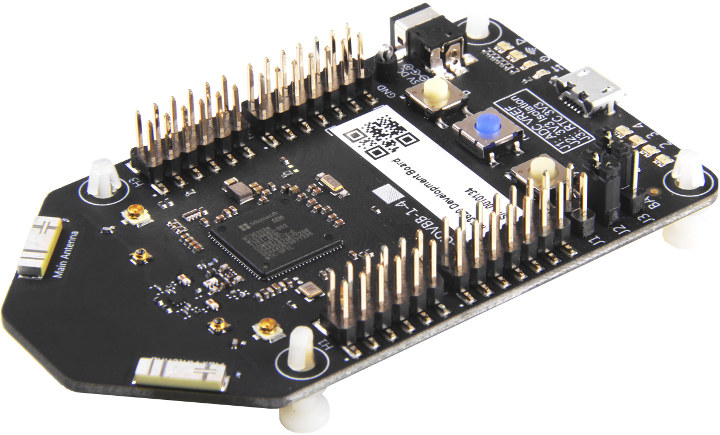

MT3620 Development Board for Azure Sphere is Up for Pre-order for $84.90

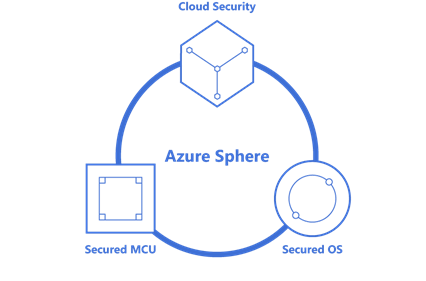

Microsoft unveiled Azure Sphere solutions last month in order to provide a complete secure IoT solution from the hardware to the cloud with three main components: a secure MCU, Linux based Azure Sphere OS, and Azure Sphere Security (Cloud) Service. The company already stated Mediatek MT3620 would be the first Azure Sphere compliant MCU, and today Seeed Studio has announced MT3620 development board for Azure Sphere is up for pre-order for $84.90 with a $5 deposit, and shipping scheduled for the end of September. Preliminary specifications of MT3620 development board for Azure Sphere: WiSoC – Mediatek MT3620AN single core Arm Cortex-A7 processor @ 500 MHz, dual core Arm Cortex-M4F real-time core, Pluton security sub-system, and WiFi. System Memory – Over 5MB of embedded RAM, split among the various cores (4MB for Arm Cortex A7 core) Storage – 2x 8MB dual channel quad SPI (16MB in total) Connectivity – Dual band […]

Microsoft Introduces Azure Sphere OS Linux Operating System for Certified Microcontrollers (MediaTek MT3620 for now)

Last year, Microsoft announced they were working with Mediatek on Project Sopris Secure WiFi MCU, based on Mediatek MT7687 MIPS microcontroller with 7 properties enhancing security (Hardware-based Root of Trust, failure reporting etc…). The company has now unveiled a complete secure IoT solution with Azure Sphere comprised of three main components: Azure Sphere certified secured MCUs which combine real-time and application cores with built-in Microsoft security technology and connectivity. The first compatible MCU will be Mediatek MT3620, which differs from MIPS based Project Sopris, as it features one Cortex A7 and two Cortex M4 cores as well as WiFi connectivity. Azure Sphere OS that provides four layers on top of the hardware: security monitor, custom Linux kernel, on-chip connectivity services to Azure Sphere Security Service, and app containers for computer (A7 core) or/and real-time I/Os (M4 cores). Azure Sphere Security Service, a secure cloud service for Azure Sphere device that […]