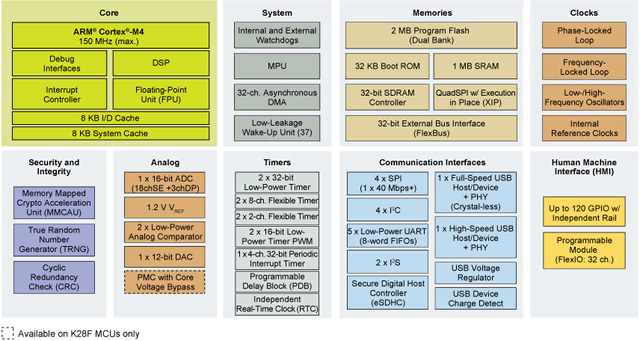

NXP pushed out several press releases with the start of Embedded World 2017 in Germany, including three new micro-controllers/processors addressing different market segments: Kinetis K27/K28 MCU Cortex M4 MCU family, QorIQ Layerscape LS1028A industrial applications processor, and i.MX 8X SoC family for display and audio applications, 3D graphic display clusters, telematics and V2X (Vehicle to everything). NXP Kinetis K27/K28 MCU NXP Kinetis K27/K28 MCU family is based on an ARM Cortex-M4 core clocked at up to 150 MHz with FPU,and includes up to 1MB embedded SRAM, 2MB flash, and especially target portable display applications. Kinetis K27/K28 MCUs share the following main features: 2x I2S interfaces, 2x USB Controllers (High-Speed with integrated High-Speed PHY and Full-Speed) and mainstream analog peripherals 32-bit SDRAM memory controller and QuadSPI interface supporting eXecution-In-Place (XiP) True Random Number Generator, Cyclic Redundancy Check, Memory Mapped Cryptographic Acceleration Unit K28 supports 3 input supply voltage rails (1.2V, 1.8V […]

NXP QorIQ LayerScape LA1575 Programmable Wireless SoC to Support 5G, 802.11ax & 802.11ad WiFi, and Wireline

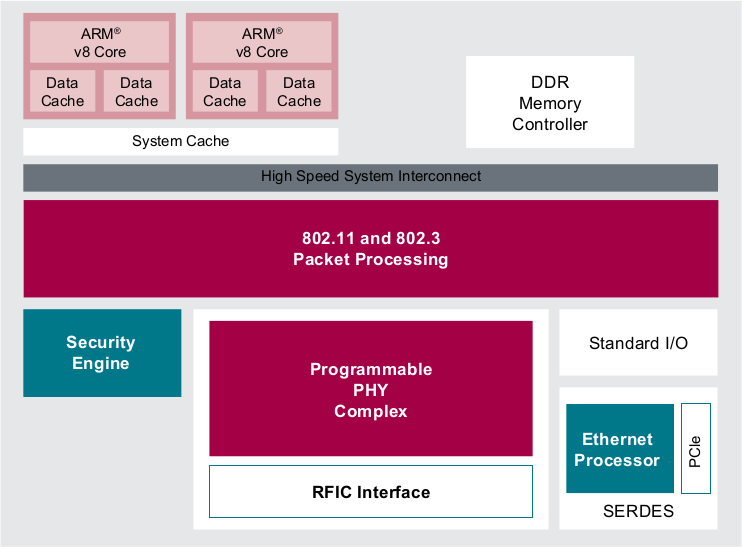

NXP has recently announced QorIQ LayerScape LA1575 programmable wireless platform with two ARMv8 cores, and simultaneous multi-standard support for 5G, Wi-Fi (802.11 ac and 802.11ax) and Wireline systems for enterprise and high-end home gateways. QorIQ LayerScape LA1575 key features and specifications: Multicore ARMv8 Processors for user applications DDR4 with ECC Programmable accelerator engines for signal processing. Programmable low latency MAC layer processing engines Programmable high performance packet processing engines to over 10 Gbps Configurable cryptographic offload engines Simultaneous multi-standard support for 5G, Wi-Fi (802.11 ac and 802.11ax) and Wireline systems Multiple Ethernet interfaces including 10Gbps PCIe gen 3.0 Integrated Trust architecture Single source clocking The main benefit of this SoC is that is is programmable, so even if some standards evolve after the release, it can be re-programmed to reflects the changes in specifications. Just to refresh everybody’s memory: 5G is the successor of 4G/LTE scheduled to start (Wave 1) around 2018, […]

LEDE 17.01.0 “Reboot” Router Operating System Released

LEDE (Linux Embedded Development Environment) is a fork of OpenWrt after some disagreements between developers, and while there are talks about merging OpenWrt and LEDE development, this is not done yet, and LEDE 17.01 has been released a few days ago. Some of notable LEDE 17.01 changes include: Linux kernel updated to version 4.4.50 (from 3.18 in Chaos Calmer) Update to dnsmasq 2.76, busybox 1.25.1, mbedtls 2.4.0, openssl 1.0.2k Improved Security Features Improved Networking Support Added new targets: apm821xx (AppliedMicro APM821xx) arc770 (Synopsys DesignWare ARC 770D) archs38 (Synopsys DesignWare ARC HS38) armvirt (QEMU ARM Virtual Machine) ipq806x (Qualcomm Atheros IPQ806X) layerscape (NXP Layerscape) zynq (Xilinx Zynq 7000 SoCs) Reorganized x86 target – Drop dedicated Xen DomU target, merged with x86/generic * Enable AES-NI support Build system improvements Image Builder / SDK – Rework library bundling to allow for better portability between different Linux distributions, added support for building kernel modules […]

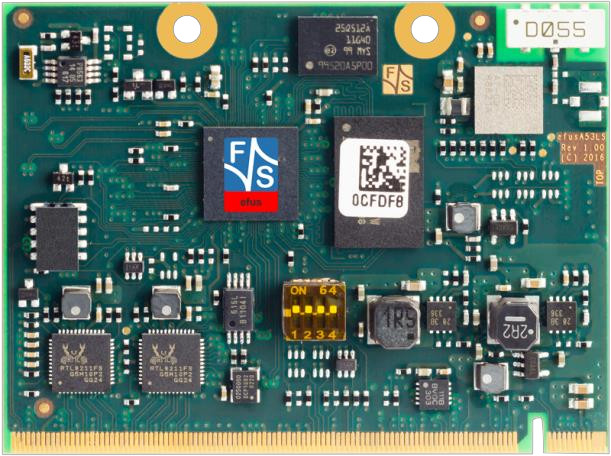

F&S Elektronik Introduces efus A53LS NXP QorIQ LS1012A System-on-Module for Communication & Networking Applications

NXP QorIQ LS1012A is a single core Cortex A53 communication processor that offers a 64-bit update to LS1021A dual core Cortex A7 processors found in gateways such as NXP LS1021A-IOTA IoT gateway reference design, and F&S Elektronik System has just launched efus A53LS system-on-module powered by the processor with up to 1GB RAM, up to 64SQPI NOR, access to the communication interfaces and peripherals from the processor via an efus compliant edge connector, and long term availability until 2030. efus A53LS COM specifications: Processor – NXP QorIQ Layerscape LS1012A single core ARM Cortex-A53 @ up to 800MHz System Memory – 512MB DDR3 by default, supports up to 1GB DDR3 RAM Storage – Up to 64MB QSPI NOR flash on-module, I/Os for SATA and SD card on edge connector Connectivity – 2x Realtek RTL8211F(N) Gigabit Ethernet transceiver chips, optional wireless module with dual WiFi IEEE802.11b/g/n/ac and Bluetooth 4.0 LE efus edge […]

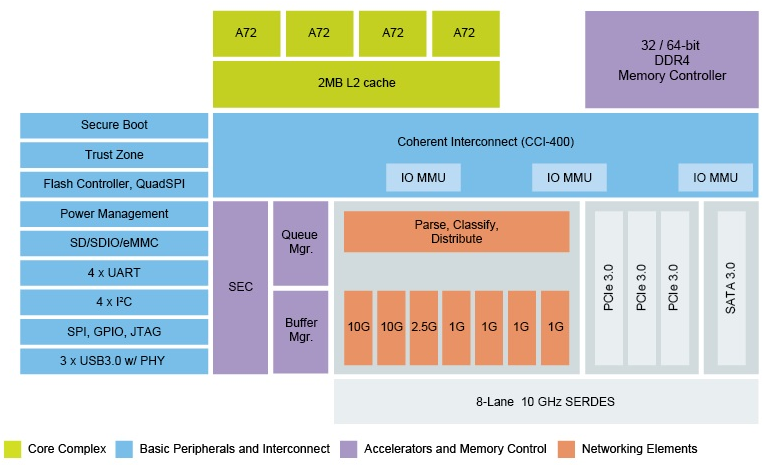

NXP Introduces QorIQ LS1046A Quad Cortex A72 Communication Processor with 10 GbE, SATA 3.0, PCIe 3.0, etc…

NXP has unveiled a new QorIQ communication processor with LS1046A based on quad ARM Cortex-A72 cores, and including 10GbE, PCIe Gen.3, SATA 3.0, and USB 3.0 interfaces. The processors targets CPE and vCPE (virtual Customer Premise Equipment), routers, NAS, and service provider gateways for the home and small office, as well as single board computers. QorIQ LS1046A key specifications: CPU – Four ARM Cortex -A72 cores with 2MB L2 cache; 32,000 CoreMarks. Memory – 32-/64-bit DDR4 memory controller Storage – SATA 3.0 controller, quad SPI Connectivity 2x 10 Gigabit Ethernet controllers 1x 2.5 Gigabit Ethernet controller 4x Gigabit Ethernet controllers Other peripherals 3x PCIe 3.0 Controllers, x4, x2, x 1 3x USB 3.0 with integrated PHY 4x UART, 4x I2C, SPI, GPIO JTAG Support for hardware-based virtualization via ARM SMMU Packet processing acceleration – Packet classification and distribution; hardware work scheduling, shaping, and buffer management. Integrated security engine – High-speed […]

Linux 4.0 Release – Main Changes, ARM and MIPS Architectures

Linus Torvalds “Ima Sheep” released Linux Kernel 4.0 on Sunday: So I decided to release 4.0 as per the normal schedule, because there really weren’t any known issues, and while I’ll be traveling during the end of the upcoming week due to a college visit, I’m hoping that won’t affect the merge window very much. We’ll see. Linux 4.0 was a pretty small release both in linux-next and in final size, although obviously “small” is all relative. It’s still over 10k non-merge commits. But we’ve definitely had bigger releases (and judging by linux-next v4.1 is going to be one of the bigger ones). Which is all good. It definitely matches the “v4.0 is supposed to be a_stable_ release”, and very much not about new experimental features etc. I’m personally so much happier with time-based releases than the bad old days when we had feature-based releases. That said, there’s a few […]

Linux 3.19 Release – Main Changes, ARM and MIPS Architectures

Linus Torvalds released Linux Kernel 3.19 yesterday: So nothing all that exciting happened, and while I was tempted a couple of times to do an rc8, there really wasn’t any reason for it. Just as an example, Sasha Levin used KASan and found an interesting bug in paravirtualized spinlocks, but realistically it’s been around forever, and it’s not even clear that it can really ever trigger in practice. We’ll get it fixed, and mark it for stable, and tempting as it was, it wasn’t really a reason to delay 3.19. And the actual fixes that went in (see appended shortlog) were all fairly small, with the exception of some medium-sized infiniband changes that were all reverting code that just wasn’t ready. So it’s out there – go and get it. And as a result, the merge window for 3.20 is obviously also now open. Linus Linux 3.18 improved performance of […]

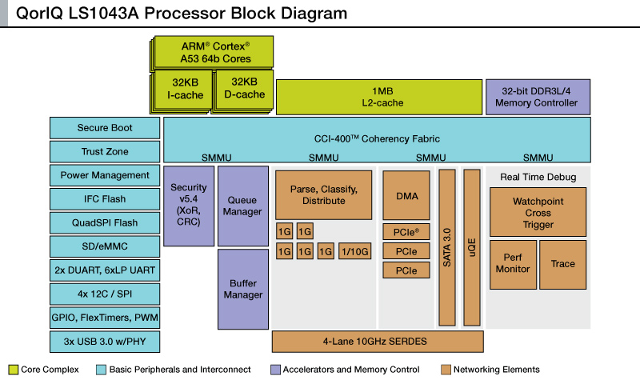

Freescale Unveils QorIQ LS1043A Quad core ARM Cortex A53 Communication Processor for Fanless Networking Equipment

Freescale has introduced the QorIQ LS1043A communications processor, powered by four 64-bit ARM Cortex A53 cores, and destined to be integrated into “intelligent-edge networking equipment including security appliances, SDN (Software Designed Networks) / NFV (Network Functions Virtualization) edge platforms and other fanless, power-efficient applications.” A dual core version named LS1023A is also available. Key features of LS1043A and LS1023A SoCs: CPU – Quad (LS1043A) or Dual (LS1023A) ARM Cortex-A53 64-bit cores @ 1 GHz to 1.5 GHz with 32/32 I/D Cache KB L1 and 1 MB L2 cache. 16,000+ CoreMarks. Networking & High Speed Interfaces: Up to six 1x GbE or 1x 10GbE and five x GbE Four lane SerDes up to 10 GHz multiplexed across controllers supporting: Three PCI Express Gen 2 interfaces SATA 3.0 Interface uQUICC Engine Accelerators and Memory Control DPAA (Data Path Acceleration Architecture) Parse, Classify and Distribution Engines Integrated security engine 32-bit DDR3L/4 controller Other peripherals 3x […]