Linus Torvalds announced the release of Linux 5.2 last Sunday: So I was somewhat pre-disposed towards making an rc8, simply because of my travels and being entirely off the internet for a few days last week, and with spotty internet for a few days before that [*]. But there really doesn’t seem to be any reason for another rc, since it’s been very quiet. Yes, I had a few pull requests since rc7, but they were all small, and I had many more that are for the upcoming merge window. Part of it may be due to the July 4th week, of course, but whatever – I’ll take the quiet week as a good sign. So despite a fairly late core revert, I don’t see any real reason for another week of rc, and so we have a v5.2 with the normal release timing. There’s no particular area that stands […]

More Investments into RISC-V – Qualcomm Backs SiFive, OpenHW Group Created

Some may doubt RISC-V will ever challenge Arm at least in some markets, but the industry is investing in solutions based on the royalty-free open source ISA, with this week SiFive securing $65.4 Million from various investors including Qualcomm Ventures LLC, and the announcement of the launch of the OpenHW Group, a new not-for-profit global organization aims to boost the adoption of open-source processors currently backed by 13 companies, and aiming to reach 25 sponsors by year’s end. SiFive gets more interest from investors Here’s the main part of the announcement of SiFive’s new series D funding: SiFive, Inc., the leading provider of commercial RISC-V processor IP and silicon solutions, today announced it raised $65.4 million in a Series D round led by existing investors Sutter Hill Ventures, Chengwei Capital, Spark Capital, Osage University Partners and Huami, alongside new investor Qualcomm Ventures LLC. This Series D round brings the total […]

SiFive RISC-V Processors to Support Imagination PowerVR GPU and NNA IP Cores

RISC-V is getting more popular and mature as development progress, but if you want a system with RISC-V and a GPU so far you had to use a PCIe graphics card which is not cost-effective nor practical for most applications based on RISC-V processor. What is needed is some GPU IP that will glue with RISC-V core. Developing a new GPU is not an easy task (understatement of the month) so it would make sense to go with solutions available on the market. However, Arm Mali is tied to Arm Cortex cores and Arm is unlikely to want to help RISC-V take away their market share, and Adreno and VideoCore are owned by respectively Qualcomm and Broadcom which are unwilling to provide their GPU IP to third parties. This basically leaves us with Vivante and Imagination. Vivante may have made the most sense since open-source graphics drivers do exist (Etnaviv), […]

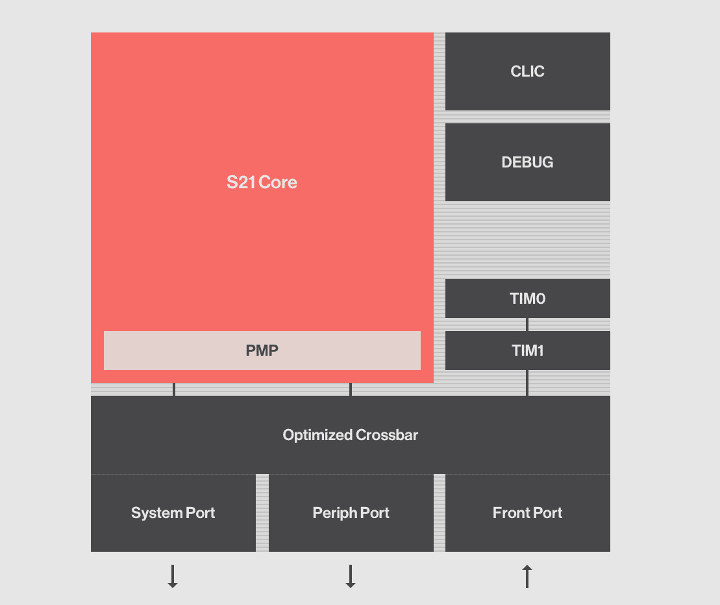

SiFive S2 RISC-V Core may be the World’s Smallest 64-bit Embedded Core

Last year, SiFive introduced their first RISC-V cores competing with Arm Cortex-R family of processors thanks to their S7 Series 64-bit RISC-V Core IP providing an answer to Arm Cortex-R7/R8 32-bit real-time processors. The company has now announced the SiFive S2 RISC-V core that it claims to be the world’s smallest 64-bit embedded core, and also the first SiFive IP core without any direct competitive equivalent in the market. For now, there’s only one core in the family with SiFive S21 offering the following key features: RISC-V ISA – RV64IMAC 64-bit AXI Ports Machine and User Mode with 4 Region Physical Memory Protection 3-stage pipeline with Simultaneous Instruction and Data Access 2 Banks of Tightly Integrated Memory (TIM) CLIC (Core Local Interrupt Controller) with 127 interrupts Advanced debug with 4 hardware breakpoints/watchpoints Performance – 1.6 DMIPS/MHz; 3.2 Coremarks/MHz The company compares its to the SiFive S5 cores, which I had […]

HiFive1 Rev B Board Gets FE310-G002 RISC-V Processor, WiFi & Bluetooth Module

SiFive launched what may have been the very first RISC-V development board in 2016 thanks to their HiFive1 Arduino compatible board powered by Freedom E310 (FE310) open source RISC-V processor. The company has now launched an upgrade version of the processor and board. Meet FE310-G002 processor and HiFive1 Rev B development board. HiFive1 Rev B development board specifications with new features highlighted in bold or stricken-through: MCU – SiFive Freedom E310-G0002 32-bit RV32IMAC processor @ up to 320+ MHz (1.61 DMIPS/MHz) Storage – 32 Mbit SPI flash (was 128 Mbit in the first version) Connectivity – ESP32-SOLO-1 WiFi & Bluetooth module I/Os 19x Digital I/O Pins 19x external interrupt pins 1x external wakeup pin 9x PWM pins 1/3 SPI Controllers/HW CS Pins I/O Voltages – 3.3V or 5V supported; note: bidirectional level shifters removed so FE310-G002 can drive the I/O pins directly at 3.3V only. USB – 1x micro USB […]

FreeRTOS Kernel Now Supports RISC-V Architecture

FreeRTOS is one of the most popular operating systems found in embedded systems, and RISC-V open architecture is getting more and more traction, so it should come as no surprise that Amazon has now added RISC-V to their recently acquired FreeRTOS kernel. Jeff Barr, Chief Evangelist for AWS, explains both 32-bit and 64-bit RISC-V cores are supported, and several RISC-V boards are already supported out of the box: The kernel supports the RISC-V I profile (RV32I and RV64I) and can be extended to support any RISC-V microcontroller. It includes preconfigured examples for the OpenISA VEGAboard, QEMU emulator for SiFive’s HiFive board, and Antmicro’s Renode emulator for the Microchip M2GL025 Creative Board. There’s no a lot of information on Amazon announcement post, but FreeRTOS website has plenty of resources to help you get started with RISC-V. The page also lists some of the key features of the RISC-V port: Supports machine […]

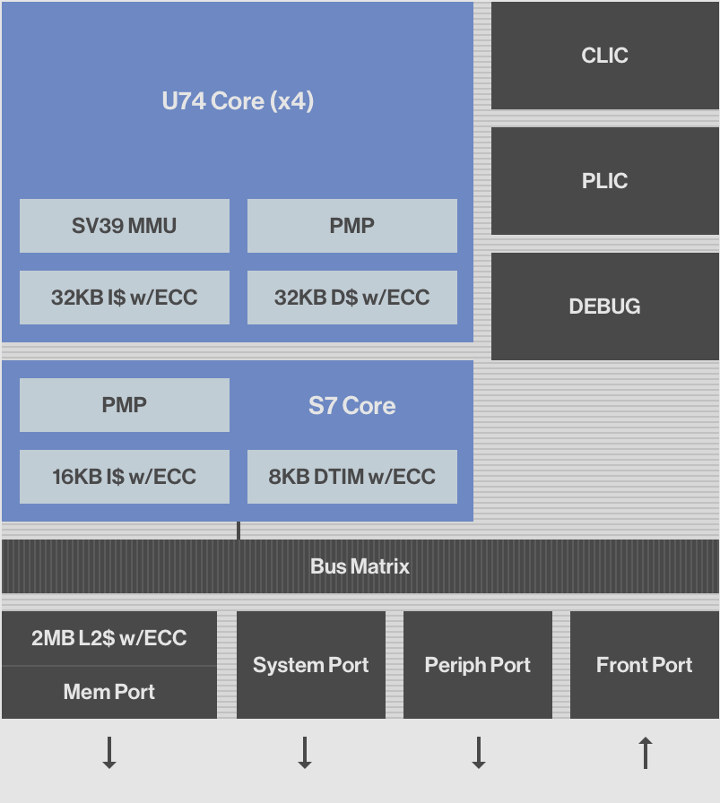

SiFive Introduces 7 Series RISC-V Cores with E7, S7 and U7 series

SiFive has recently announced their Core IP 7 Series of RISC-V cores offering better performance, and designed to enable “embedded intelligence” in applications such as 5G, networking, storage, augmented reality, artificial intelligence, SLAM, and sensor fusion. Three families of the new 7 Series been launched with namely SiFive E7, S7 and U7 Core IP Series, so let’s have a look at each of them. E7 Core IP Series – E76 and E76-MC Cores The E7 Core IP Series comprises the 32-bit E76 and E76-MC (Multi-core), provides hard real-time capabilities, and compares to Arm’s Cortex M7, Cortex-R7/R8 cores. E76-MC Key Features Fully compliant with the RISC-V ISA specification 4x RV32IMAFC E76 Cores Machine and User Mode Support In-order, 8-stage pipeline Advanced Memory Subsystem 32KB Instruction Cache 32KB Instruction Tightly Integrated Memory (ITIM) 32KB Data Cache 32KB FIO RAM 256KB L2 Cache High-performance TileLink Interface Benchmark Scores- 2.3 DMIPS/MHz, 4.9 CoreMark/MHz E76 […]

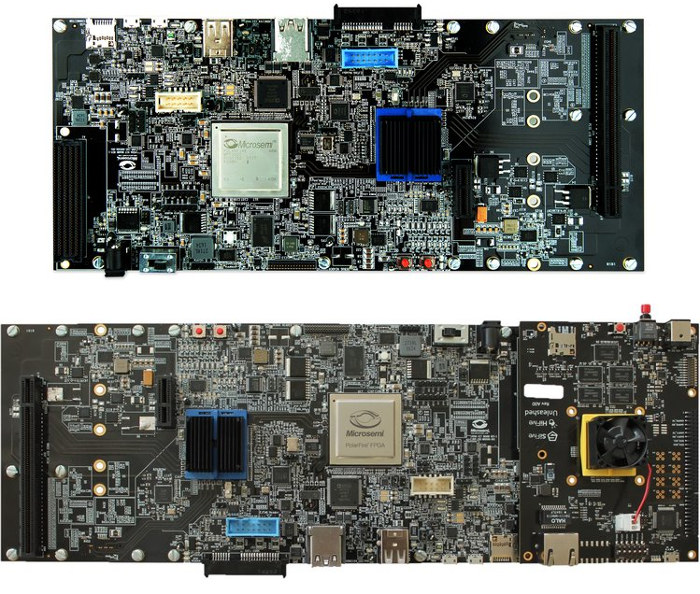

HiFive Unleashed RISC-V Linux Development Board Gets a $2000 FPGA Expansion Board

If you’re a RISC-V architecture’s enthusiast or represent a company working on products with the new ISA, you may have spent $999 or more on Hifive Unleashed RISC-V Linux development board a few months ago. You now have the opportunity to spend an extra $1,999 for HiFive Unleashed Expansion Board powered by a MicroSemi PolarFire FPGA programmed with a PCIe root port bridge, and allowing you to test all sorts of peripherals such as HDD’s & SSD’s, HDMI output, and audio cards, network adapters, graphics cards, and so on. Expansion board specifications: FPGA – Microsemi Low Power PolarFire FPGA with 300K Logic Element 4 Gbit DDR4 x16 SPI Flash for remote FPGA updates, QSPI Flash connected to GPIO 24 lane PCIe Switch x1 PCI Express card connector x16 PCI Express card connector with 4 lanes of PCIe gen2 connected SSD M.2 connector SATA connector HDMI connector eMMC Nand Flash uSD […]