Linus Torvalds has just released Linux 5.8: So I considered making an rc8 all the way to the last minute, but decided it’s not just worth waiting another week when there aren’t any big looming worries around. Because despite the merge window having been very large, there really hasn’t been anything scary going on in the release candidates. Yeah, we had some annoying noise with header file dependencies this week, but that’s not a new annoyance, and it’s also not the kind of subtle bug that keeps me up at night worrying about it. It did reinforce how nice it would be if we had some kind of tooling support to break nasty header file dependencies automatically, but if wishes were horses.. Maybe some day we’ll have some kind of SAT-solver for symbol dependencies that can handle all our different architectures and configurations, but right now it’s just a manual […]

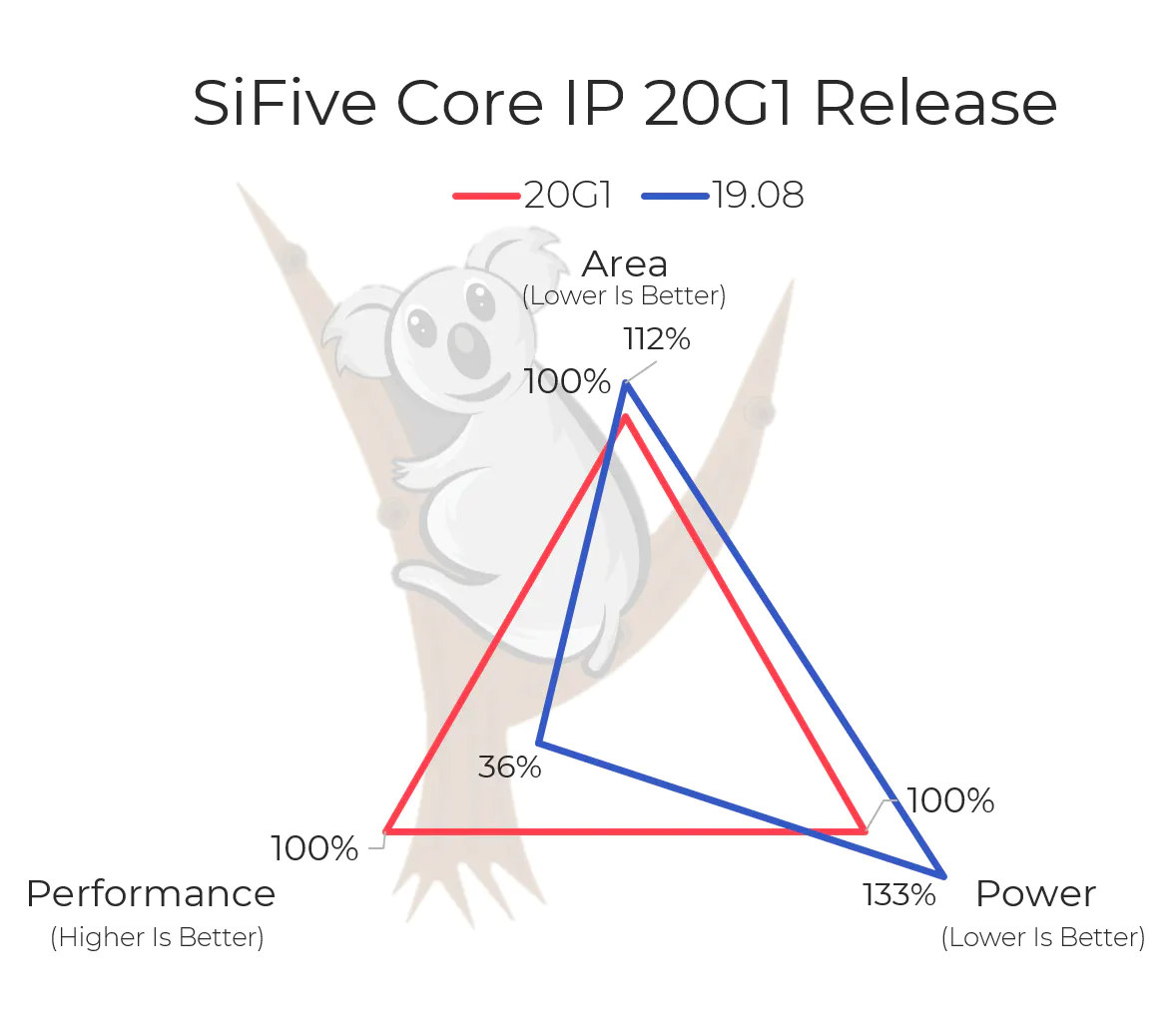

SiFive RISC-V Processors Get Performance & Efficiency Improvements, Smaller Footprint with 20G1 Release

SiFive RISC-V cores portfolio ranges from low power 32-bit IoT processors to more powerful, Linux-capable 64-bi RISC-V cores like the latest SiFive U84/U87 cores rivaling with Arm Cortex-A7x cores. SiFive Core IP 20G1 release further enhances the company’s existing RISC-V cores with performance improvements, higher efficiency, and a smaller footprint. Specifically, SiFive claims the SiFive U7-Series has increased load bandwidth up to 2.8x for memory-intensive workloads such as AI inference processing, and all of the company’s RISC-V cores can now run at lower power, with the SiFive U74 standard core running at up to 25% lower power while running Dhrystone benchmark. The SiFive E-Series processors which feature real-time capability are now available with the RISC-V Embedded extension (RV32E) which reduces the footprint compared to RV32I ISA with for instance up to 11% smaller area for the SiFive E3-Series. RV32E and RV32I have the same instructions set, but RV32E comes with […]

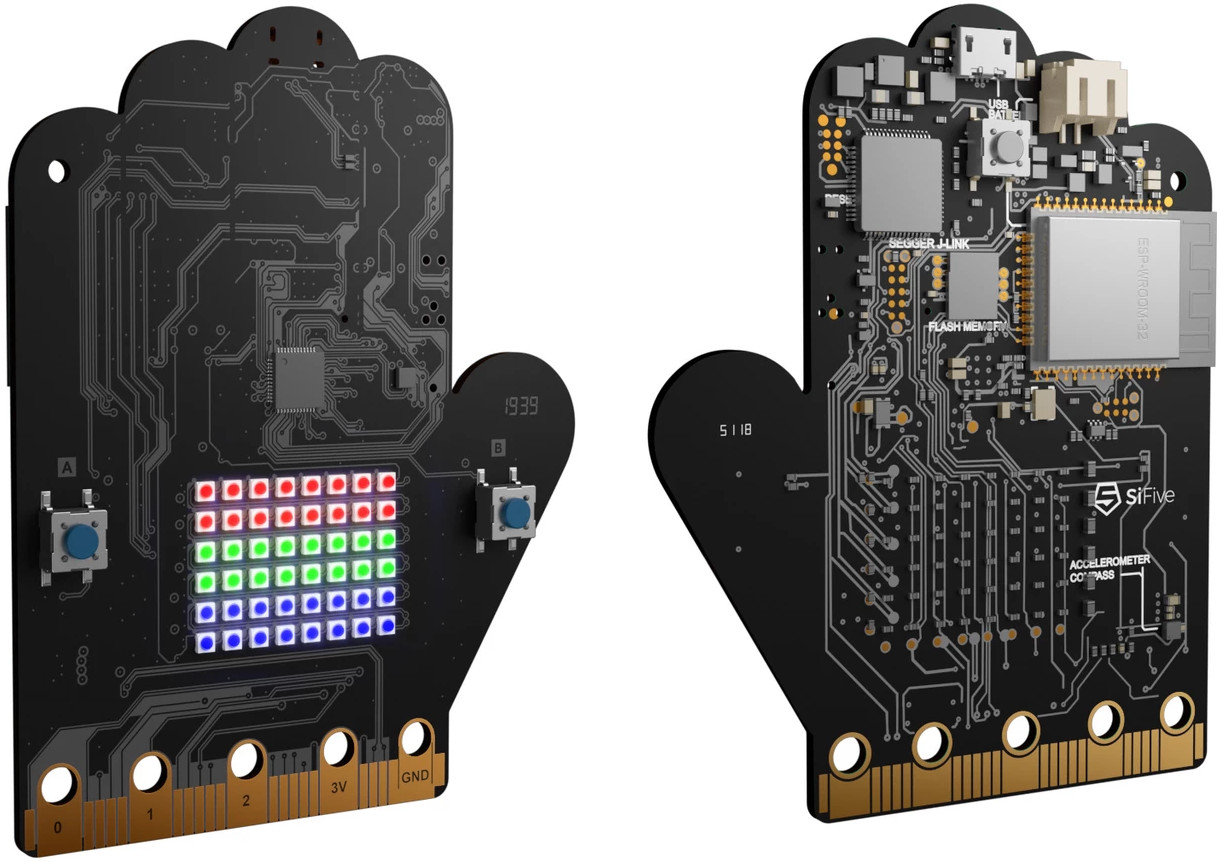

SiFive Learn Inventor is a Wireless RISC-V Development Kit Inspired by BBC Micro:bit

SiFive Learn Inventor is a RISC-V educational board partially inspired by BBC Micro:bit board with the same crocodile clip-friendly edge connector, and an LED matrix. The board is also fully qualified to work with the Amazon FreeRTOS real-time operating system. Shaped in the form of a hand, the board features SiFive FE310 RISC-V processor found in the SiFive HiFive1 board, as well as ESP-WROOM-32 WiFi + Bluetooth module. SiFive Learn Inventor specifications: SoC – SiFive FE310-G003 32-bit RISC-V (RV32IMAFC) processor @ 150 MHz with 64KB of internal SRAM Storage – 512 KB flash “Display” – 6×8 “widescreen” array of RGB LEDs with 262,000 colors each; LEDs can expand off-board onto external arrays via the edge connector Wireless Connectivity – 802.11b/g/n WiFi 4 (2.4GHz) and Bluetooth 4.2 LE via an ESP32 module (ESP-WROOM-32) USB – 1x Micro USB port for power and programming/debugging Expansion A/D Converters (four) accessed via on-board coprocessor […]

Linux 5.4 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds has just announced the release of Linux 5.4: Not a lot happened this last week, which is just how I like it. And as expected, most of the pull requests I got were for the 5.5 merge window, which I’ll obviously start working through tomorrow. What little there is here is mostly some networking updates (mix of network drivers and core networking), and some minor GPU driver updates. Other than that it’s a small collection of random other things all over. The appended shortlog is small enough that you might as well just scroll through it. Anyway, this obviously opens the merge window for 5.5. It’s not ideal timing with Thanksgiving week coming up, but it hopefully shouldn’t be too much of an issue. If I fall behind (not because I’m all that big of a fan of the indiscriminate and relentless turkey-killing holiday) it’s because we’ve got […]

SiFive U8-Series Out-of-Order RISC-V Core IP Takes on Arm Cortex-A72 Core

Earlier this week, we wrote about SiFive Shield open security platform as the equivalent of Arm TrustZone security technology, but the company had had another important announcement this week with the introduction of SiFive U8-Series Out-of-Order (OoO) RISC-V Core IP with much higher performance than the company’s earlier U7-series core and competing with Arm Cortex A72 core. At first, the company will offer two standard cores with SiFive U84 RISC-V core optimized for power efficiency and area efficiency, and the SiFive U87 RISC-V core with vector processing. SiFive U84 Performance & Efficiency We do not have much information about U87, but SiFive already published some interesting details about U84 cores. SiFive U84 core offers about 3.1 times higher performance compared to their earlier U74 standard core thanks to a 2.3x increase in IPC combined with a 1.4x increase in maximum frequency. Compared to SiFive U54, U84 delivers 5.3x higher performance […]

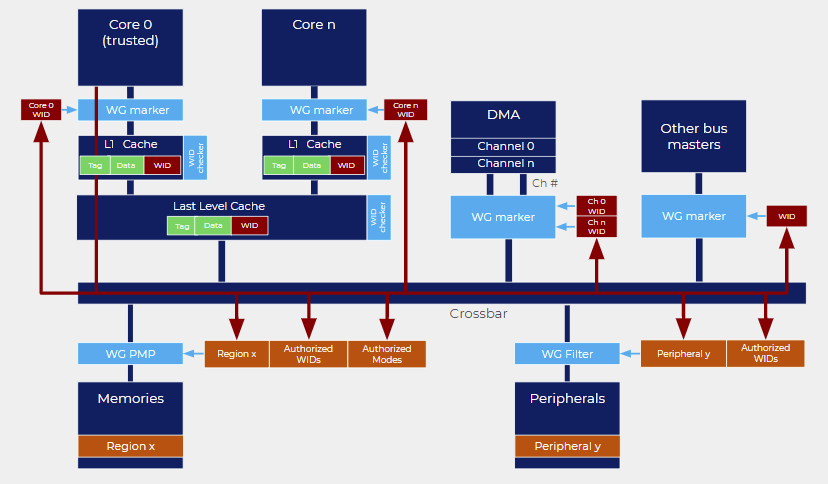

SiFive Shield is an Open Security Platform for RISC-V Processors

Most Arm processors and Armv8-M microcontrollers support Arm TrustZone security with hardware-enforced isolation built into the CPU. But so far, I had not read anything about equivalent solutions for RISC-V processors. It turns out Hex-Five’s MultiZone security is one of the RISC-V hardware-security providing an answer to Arm TrustZone, and besides checking out the presentation slides, you can also watch the video filmed at RISC-V Workshop Taiwan last March. But what brought me to write about RISC-V security is SiFive announcement for their Shield open security platform for RISC-V processors SiFive Shield Overview SiFive Shield is an open, scalable security platform designed for RISC-V processors. It supports root-of-trust, customizations, and offers per-memory protected memory regions and multi-core privilege modes. Combined with SiFive WorldGuard, SiFive Shield enables greater isolation. SiFive WorldGuard Isolation SiFive WorldGuard is a fine-grain security model for isolated code execution and data protection. It offers core-driven and process-id […]

Linux 5.3 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds has just announced the release of Linux 5.3: So we’ve had a fairly quiet last week, but I think it was good that we ended up having that extra week and the final rc8. Even if the reason for that extra week was my travel schedule rather than any pending issues, we ended up having a few good fixes come in, including some for some bad btrfs behavior. Yeah, there’s some unnecessary noise in there too (like the speling fixes), but we also had several last-minute reverts for things that caused issues. One _particularly_ last-minute revert is the top-most commit (ignoring the version change itself) done just before the release, and while it’s very annoying, it’s perhaps also instructive. What’s instructive about it is that I reverted a commit that wasn’t actually buggy. In fact, it was doing exactly what it set out to do, and did it […]

Linux 5.2 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds announced the release of Linux 5.2 last Sunday: So I was somewhat pre-disposed towards making an rc8, simply because of my travels and being entirely off the internet for a few days last week, and with spotty internet for a few days before that [*]. But there really doesn’t seem to be any reason for another rc, since it’s been very quiet. Yes, I had a few pull requests since rc7, but they were all small, and I had many more that are for the upcoming merge window. Part of it may be due to the July 4th week, of course, but whatever – I’ll take the quiet week as a good sign. So despite a fairly late core revert, I don’t see any real reason for another week of rc, and so we have a v5.2 with the normal release timing. There’s no particular area that stands […]