The Spartan UltraScale+ FPGA family is the latest inclusion to AMD’s Cost-Optimized portfolio, a series of FPGAs designed to balance cost, power, and form factor with affordability. The UltraScale+ FPGA family is designed for cost-sensitive, low-power applications requiring high I/O count and substantial security. Devices in the Spartan UltraScale+ family offer a high I/O to logic cell ratio for FPGAs built in 28nm and lower process technology (the highest in the industry, according to AMD), consume up to 30% less power than compared to the previous generation, and feature robust security features that outclass the rest of the Cost-Optimized portfolio. This FPGA family is built on the same UltraScale+ architecture as previous Artix and Zynq products. They are the first AMD UltraScale+ FPGAs to feature a hardened DDR memory controller and PCIe Gen4 x8 support, “providing both power efficiency and future-ready capabilities for customers.” AMD Spartan UltraScale+ specifications: System Logic […]

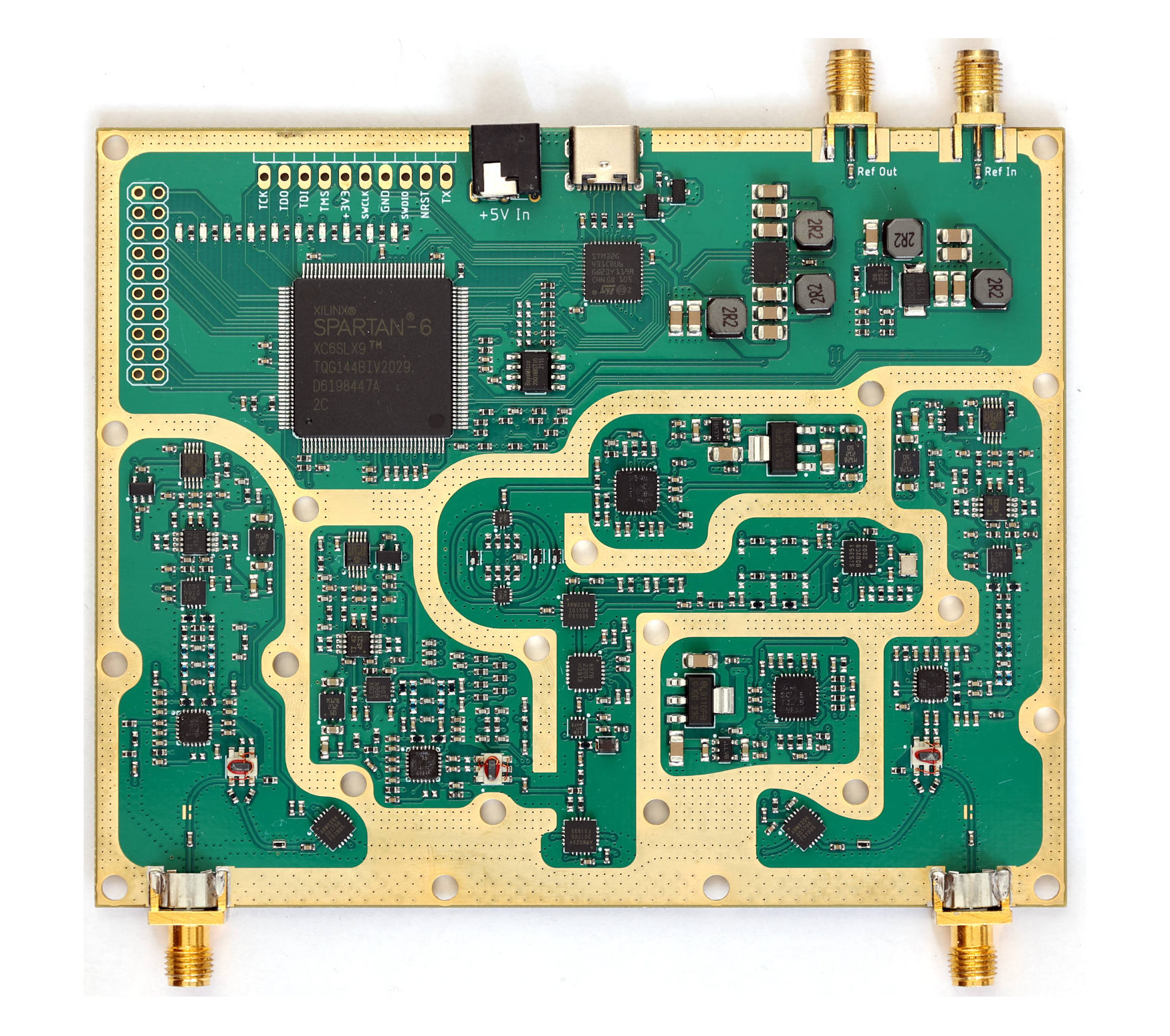

LibreVNA open-source USB vector network analyzer (VNA) works in the 100kHz to 6GHz range

Jan Käberich’s LibreVNA is an open-source hardware USB vector network analyzer (VNA) based on a Spartan-6 FPGA, an STM32 microcontroller, and RF circuitry with MAX2871 and Si5351C chips. The open-source VNA supports two channels and works in the 100kHz to 6GHz frequency range. Vector network analyzers are expensive pieces of electronic test equipment used to measure the magnitude and phase of high-frequency electrical networks costing several thousand dollars. They are commonly used in radio frequency (RF) and microwave engineering applications. Last year, we wrote that Pico Technology released PicoVNA 5 software for Linux, Raspberry Pi, and macOS instead of only providing a Windows program for their commercial PicoVNA devices. I thought it was already a good development even if it was closed-sourced, but LibreVNA goes all the way with an open-source hardware design with hardware design files, the FPGA code, STM32 firmware, and PC software (GUI) all open-source. LivreVNA hardware […]

MNT Pocket Reform 7-inch modular mini laptop takes a range of Arm (and FPGA) modules

MNT Pocket Reform is an open-source hardware mini laptop with a 7-inch Full HD display, an ortholinear mechanical keyboard, and trackball, that follows the path of its older and bigger sibling: the MNT Reform 2 laptop initially launched with an NXP i.MX 8M quad-core Arm Cortex-A53 module. The new laptop will not only support a similar “NXP i.MX 8M Plus” module but also a range of other Arm modules namely an NXP Layerscape LS1028A module with up to 16GB RAM, the Raspberry Pi CM4 module via an adapter, Pine64 SOQuartz (RK3566, up to 8GB RAM), as well as based on AMD Xilinx Kintex-7 FPGA for industrial use. MNT Pocket Reform specifications: Available system-on-modules Standard: NXP i.MX 8M Plus quad-core Arm Cortex-A53 @ 1.8GHz with 4 or 8 GB DDR4, Vivante GC7000UL GPU, 2.3 TOPS NPU NXP Layerscape LS1028A dual-core Arm Cortex-A72 with 8 or 16GB DDR4, Vivante GC7000UL GPU Raspberry […]

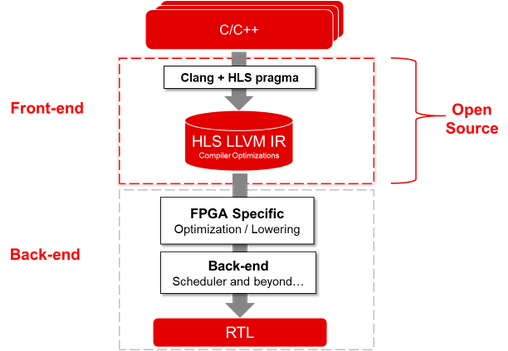

Xilinx open sources Vitis HLS FPGA tool (Front-end only)

While there are some open-source programs for FPGA development such as Symbiflow or Yosys, FPGA vendors usually only provide closed-source programs for developers wanting to work on their chips. But Xilinx has recently made a move to fulfill its “commitment to supporting open-source initiatives for developers and researchers” with the release of the source code of Vitis HLS Front-End. What is Vitis HLS exactly? Before we look at the source code release, we may want to know what Vitis HLS does exactly. The company describes it as a high-level synthesis (HLS) tool that allows C, C++, and OpenCL functions to become hardwired onto the device logic fabric and RAM/DSP blocks. It implements hardware kernels in the Vitis application acceleration development flow, and to use C/C++ code for developing RTL IP for FPGA designs in the company’s Vivado Design Suite. Vitis HLS design flow goes as follows: Compile, simulate, and debug […]

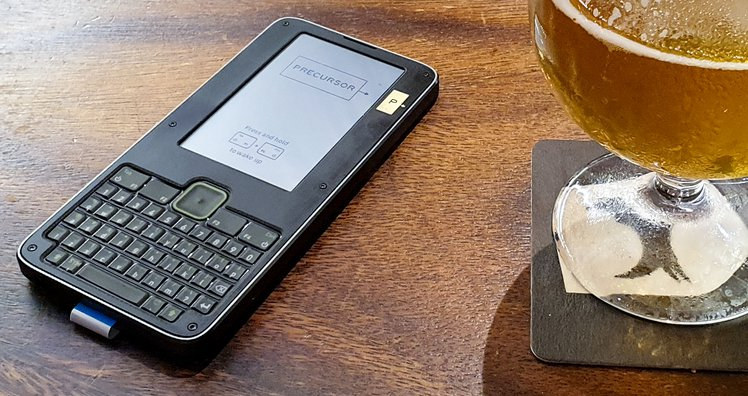

Precursor is a mobile, open hardware, dual FPGA development kit (Crowdfunding)

Sutajio Ko-usagi PTE LTD has launched some interesting hardware on Crowd Supply over the years include Novena open-source hardware Arm laptop, and Fomu FPGA USB board. The company is now back with another project: Precursor, a mobile, open-source hardware devkit powered by not one, but two FPGA with Xilinx Spartan 7-Series FPGA, plus a super-low-power Lattice iCE40 UP5K FPGA for deep-sleep system management. The device also comes with a display, battery, and keyboard that make it looks like older Palm or Blackberry phones. Precursor FPGA devkit specifications: FPGA Xilinx XC7S50 primary System on Chip (SoC) FPGA with -L1 speed grade for longer battery life; tested with 100 MHz VexRISC-V, RV32IMAC + MMU, 4k L1 I/D cache Lattice Semi iCE40UP5K secondary Embedded Controller (EC) FPGA for power, standby, and charging functions; tested with 18 MHz VexRISC-V, RV32I, no cache System Memory – 16MB external SRAM Storage – 128MB flash Display -536 […]

Hacarus Embedded AI Computing Kit Leverages Sparse Modeling Technology

AI training often requires thousands of samples to become accurate, and it can be costly and time-consuming, for example, if you want to train a model to detect manufacturing defects you’d need to provide images with both defective samples and good samples. Japanese AI experts at Hacarus have been working on a solution called Sparse Modeling which requires about 50 samples or even less for training, and worked with Congatec to provides an embedded AI computing kit leveraging the technology. Sparse Modeling Technology Hacarus does not go into great detail but explains Sparse Modeling technology is using a data modeling approach that focuses on identifying unique characteristics, in a way that humans recognize friends and family without having to look at everything from feet to head. That means algorithms based on Sparse Modeling do not need as much data as traditional AI solutions, leading to much smaller AI footprint suitable […]

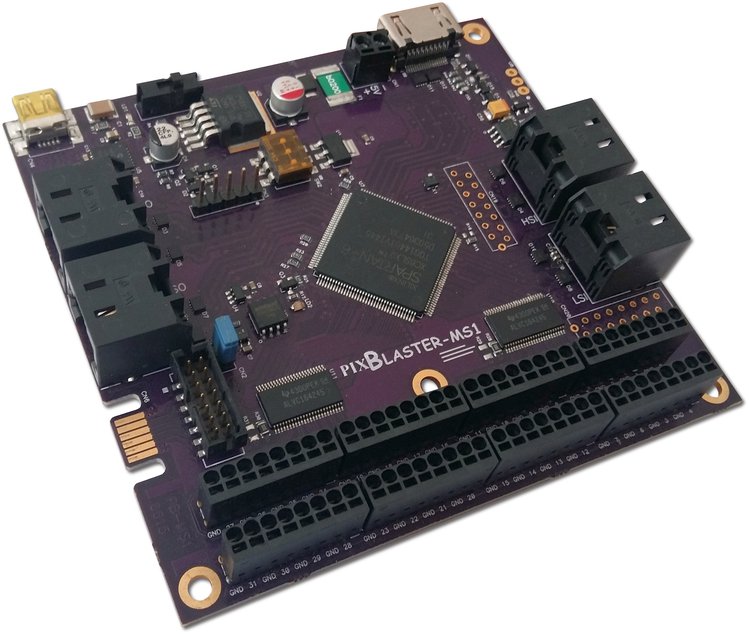

Pixblasters MS1 Video LED Controller Outputs HDMI Input to 16K+ LED Video Walls (Crowdfunding)

Pixblaster Video LED Controller Pixblasters, a company focused on LED signage and video display, have started a Crowd Supply campaign for their MS1 Video Controller. The Pixblaster MS1 controller can be attached to any laptop or computer with HDMI output (think Raspberry Pi SBC) and control 16,384 LEDs without any programming, physical modifications or soldering. Extreme Scalability The market the MS1 video controller is aimed at is small business and makers, who hadn’t before had a controller with this much scalability. The company is saying that the MS1 can be daisy-chained together to control hundreds of thousands of LEDs and act as a full video monitor across hundreds of meters of LED strips. Programming The unit can easily and with little technical knowledge connect WS212B-Based addressable LED strips together for a complex output of digital displays, even mirroring a video display in some instances. Target Users The ability to use […]

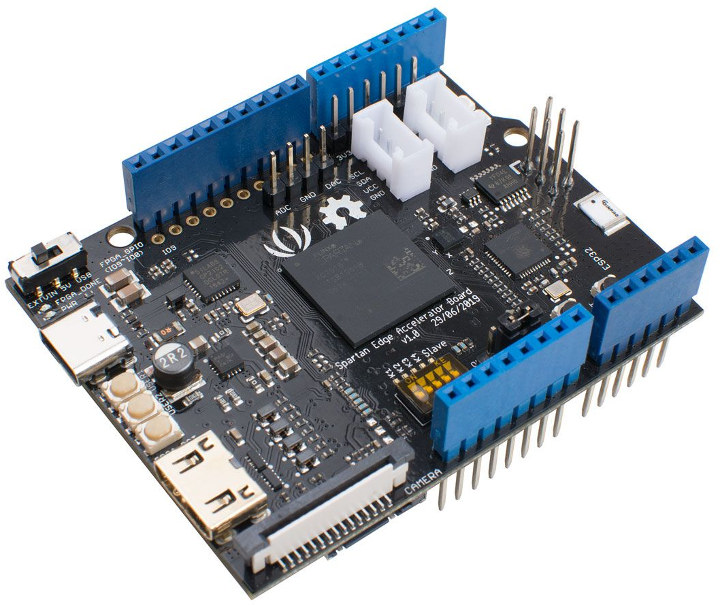

Spartan Edge Accelerator Arduino Compatible Board Combines ESP32 & Spartan-7 FPGA

Xilinx Spartan FPGAs have been around for a while, and a few years ago we covered Spartan-6 FPGA boards such as Spartixed and miniSpartan6+. Seeed Studio has now launched another Xilinx Spartan board with WiFi and Bluetooth connectivity. Spartan Edge Accelerator Board follows Arduino UNO form factor and combines a more recent Xilinx Spartan-7 FPGA with Espressif Systems ESP32 WiFi + Bluetooth chip. Spartan Edge Accelerator specifications: FPGA – Xilinx Spartan-7 XC7S15 FPGA with 12.8K Logic Cells and 360Kb block RAM WiSoC – Espressif Systems ESP32 SoC with 802.11 b/g/n 2.4GHz WiFi and Bluetooth 4.1 BLE Storage – SPI flash, MicroSD card slot Video Output – Mini HDMI Video Input – CSI Camera Interface with support for OV5640 sensor USB – USB type-C port Expansion Arduino UNO headers (5V) FPGA I/O header DAC output and ADC input header (via 8-bit ADC1173 chip) 2x Grove connectors (I2C and digital I/O) Debugging […]