While there are some open-source programs for FPGA development such as Symbiflow or Yosys, FPGA vendors usually only provide closed-source programs for developers wanting to work on their chips.

But Xilinx has recently made a move to fulfill its “commitment to supporting open-source initiatives for developers and researchers” with the release of the source code of Vitis HLS Front-End.

What is Vitis HLS exactly?

Before we look at the source code release, we may want to know what Vitis HLS does exactly. The company describes it as a high-level synthesis (HLS) tool that allows C, C++, and OpenCL functions to become hardwired onto the device logic fabric and RAM/DSP blocks. It implements hardware kernels in the Vitis application acceleration development flow, and to use C/C++ code for developing RTL IP for FPGA designs in the company’s Vivado Design Suite.

Vitis HLS design flow goes as follows:

- Compile, simulate, and debug the C/C++ algorithm.

- View reports to analyze and optimize the design.

- Synthesize the C algorithm into an RTL design.

- Verify the RTL implementation using RTL co-simulation.

- Package the RTL implementation into a compiled object file (.xo) extension, or export to an RTL IP.

A partial open-source release

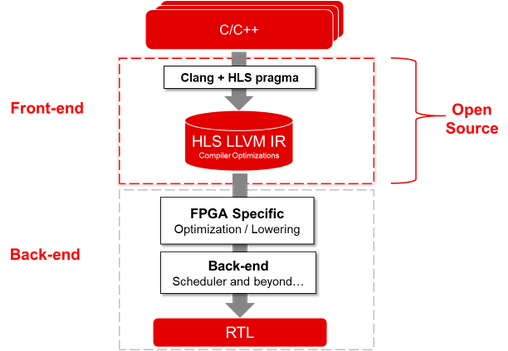

A keyword in the release is “Front-End”, as Vitis HLS back-end handling FPGA specific optimization and scheduling before RTL code generation is still closed-source.

Still, the front-end source code will allow software and hardware developers to use the standard Clang/LLVM infrastructure and customize the design flow to add support for new high-level languages, new domain-specific optimization pragmas or compiler directives, and customize the transformations to the LLVM IR (Intermediate Representations). The source code for Vitis HLS front-end can be found on Github.

The open-source version of Vitis HLS front-end has already been used by companies and universities that received the code in advance. Silexica’s SLX plugin extends Vitis HLS 2020.2 code transformations to improve Vitis HLS latency and throughput results, while the University of Illinois at Urbana Champaign integrated new Clang pragmas and LLVM for evaluation. A Ph.D. student at the Imperial College London leveraged the code to integrate its Dynamic and Static Scheduling (DASS) into the HLS flow, and the Hong Kong University of Science and Technology (HKUST) developed two projects, namely “High-Efficiency Automatic Optimization Pass Phase Ordering” and “Multi-FPGA HLS” respectively using machine-learning and heuristic algorithms to improve performance and resource consumption, and multiple FPGAs interconnected with network or DDR memory.

Additional information may be available in the announcement.

Via EETimes

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

Or an “open source” tool, which is useless if you don’t use their proprietary software. No thank you.

Xilinx, and FPGA companies in general, are the antithesis of open source.