Linus Torvalds has just announced the release of Linux 6.5 on the Linux Kernel Mailing List (LKML): So nothing particularly odd or scary happened this last week, so there is no excuse to delay the 6.5 release. I still have this nagging feeling that a lot of people are on vacation and that things have been quiet partly due to that. But this release has been going smoothly, so that’s probably just me being paranoid. The biggest patches this last week were literally just to our selftests. The shortlog below is obviously not the 6.5 release log, it’s purely just the last week since rc7. Anyway, this obviously means that the merge window for 6.6 starts tomorrow. I already have ~20 pull requests pending and ready to go, but before we start the next merge frenzy, please give this final release one last round of testing, ok? Linus The earlier […]

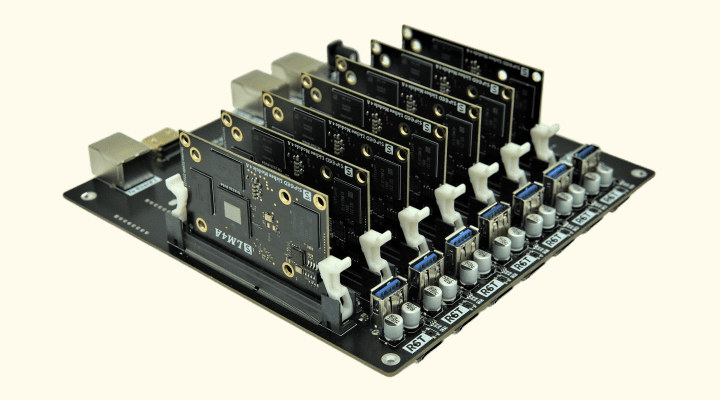

Sipeed LM4A – T-Head TH1520 RISC-V module to power Raspberry Pi 4 competitor and cluster board

Sipeed LM4A is a quad-core RISC-V system-on-module based on the T-Head TH1520 SoC found in the ROMA laptop and destinated to be found in a Raspberry Pi SBC competitor as well as a cluster board. The LM4A, which stands for Lichee Module 4 Model A, comes with 4GB to 16GB RAM, and up to 64GB flash, and connects to the carrier board through a 260-pin SO-DIMM connector. The TH1520 is one of the rare RISC-V SoCs with a 3D GPU, and the SBC based on LM4A has been shown to outperform the Raspberry Pi 4 in benchmarks as we’ll see below. Sipeed LM4A specifications: SoC – Alibaba T-Head TH1520 quad-core RISC-V Xuantie C910 (RV64GCV) processor @ 2.5 GHz, Xuantie C906 audio DSP @ 800 MHz, low power Xuantie E902 core, 50 GFLOPS Imagination 3D GPU, and 4 TOPS NPU System Memory – 4GB, 8GB, or 16GB RAM Storage – Optional […]

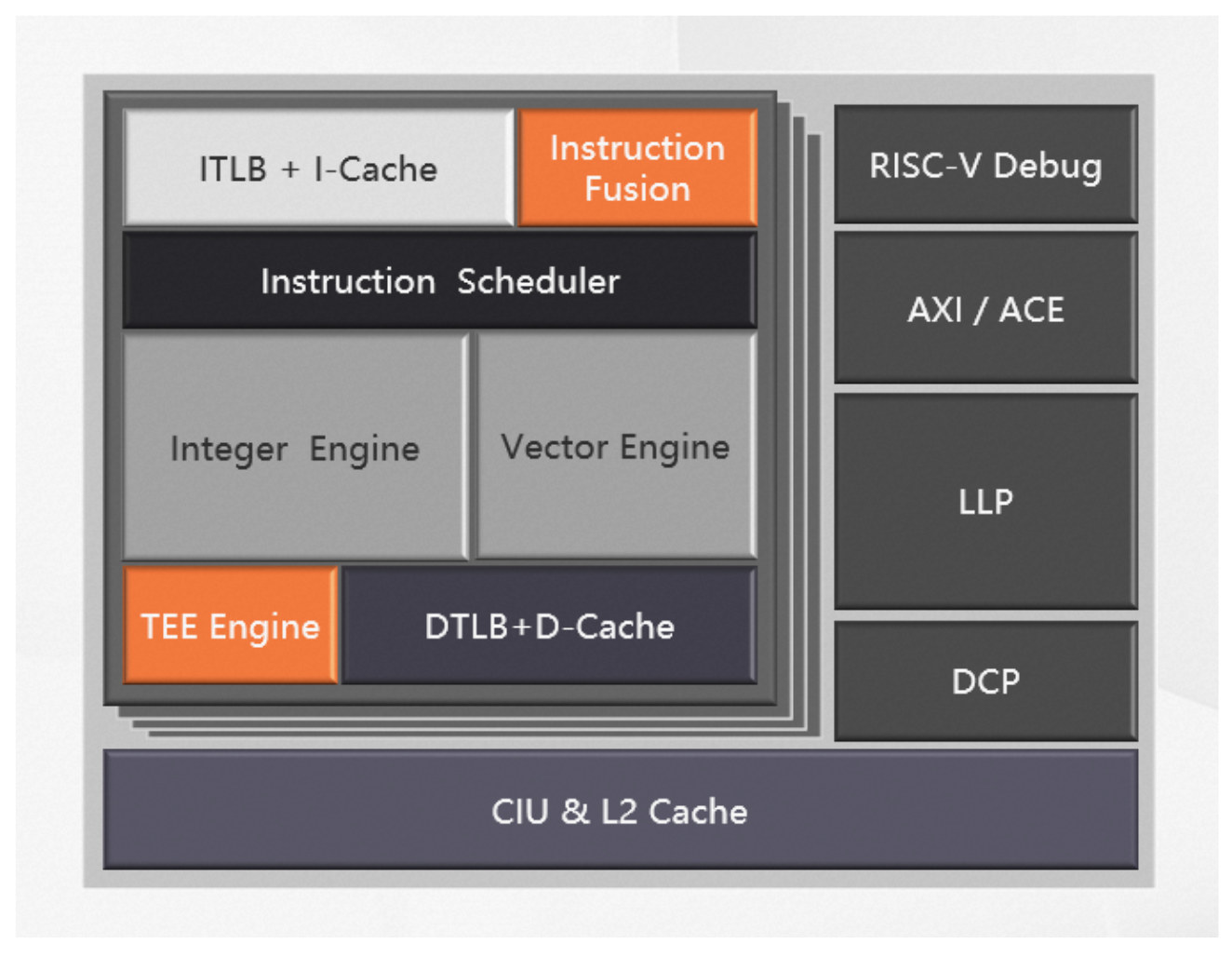

T-Head XuanTie C908 RISC-V core targets AIoT applications

We’ve seen two announcements of high-end RISC-V cores this week with the SiFive P670 and Andes AX65 processors each with a 4-way out-of-order pipeline, but Alibaba’s T-Head Semiconductor Xuantie C908 is a little different with a dual-issued, 9-stage in-order pipeline and support for the RISC-V Vector extension acceleration targeting mid-range AIoT applications. The C908 64-bit RISC-V core adopts the RV64GCB[V] instruction and complies with the RVA22 profile for better compatibility with Android and other “rich” operating systems. The company says its performance is between the C906 and C910 cores introduced in 2020 and 2019 respectively. XuanTie C908 highlights: RV32GCB[V] 32-bit and RV64GCB[V] 64-bit RISC-V architectures with Bit manipulation and (optional) Vector operations extensions Support for RV32 COMPAT mode which allows for 64-bit RISC-V CPUs to run 32-bit binary code, and was merged into Linux 5.19. XuanTie extensions, including Instruction, Memory Attributes Extension (XMAE). RVA22 profile compatibility Cluster of 1 to […]

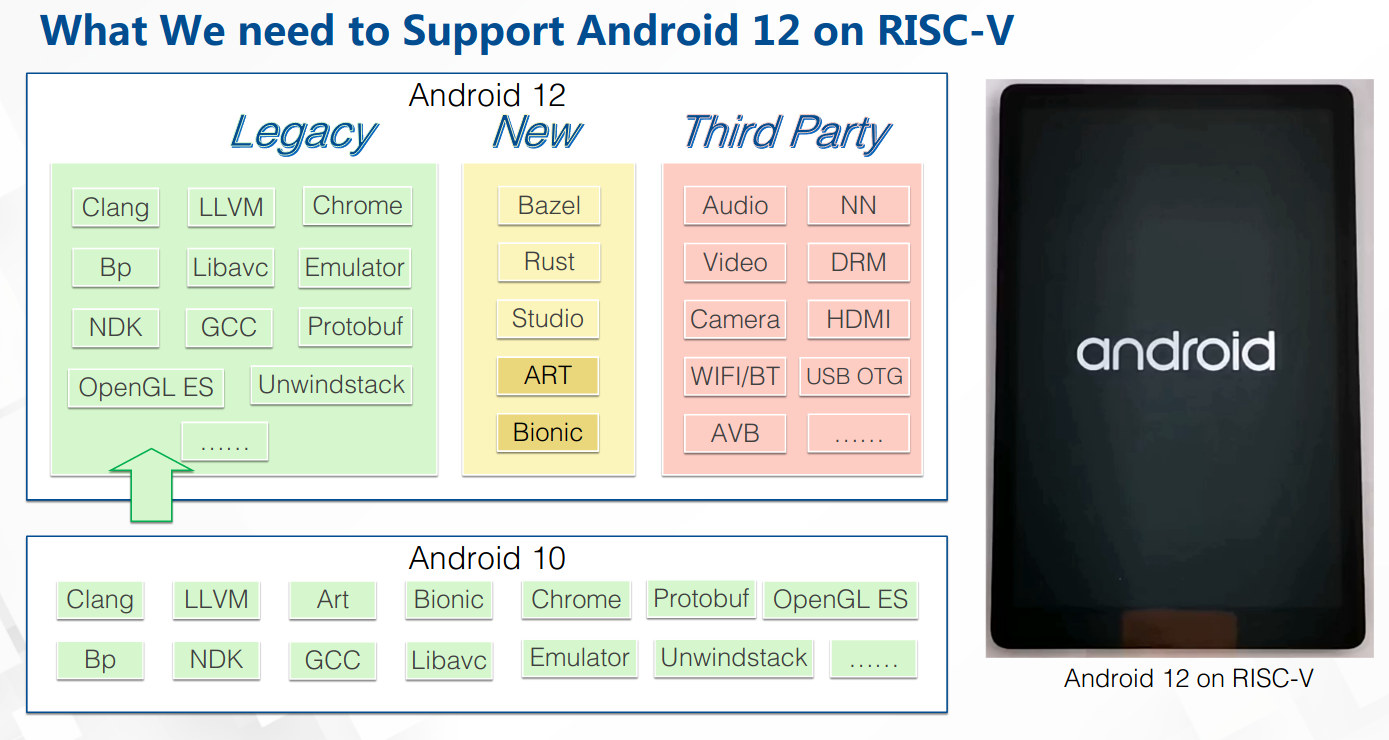

Android RISC-V progress update, emulator support, and roadmap to 2023

We’ve first covered Alibaba T-Head work on Android 10 for RISC-V in January 2021, and later that year they started selling the T-Head RVB-ICE dual-core RISC-V board with GPU for software development. The company has now provided an update for Android 12 RISC-V port, instructions to build Android RISC-V to run it in an emulator, as well as a 2022-2023 roadmap. Alibaba T-head is working on hardware platforms, which appears to be similar to T-Head RVB-ICE board, with the following minimal specifications: CPU – At least Dual-core XuanTie C910 (rv64imafdcv) processor GPU – Compatible with OpenGL ES and OpenCL VPU – HW Video/Picture codec Neural Network Accelerator System Memory – 4GB or more DDR Memory Display – MIPI/HDMI Audio – Multi-Channel Audio output & input Camera – ISP with support for multiple MIPI CSI lanes USB interface(s) They built upon the work done on Android 10 to add support for […]

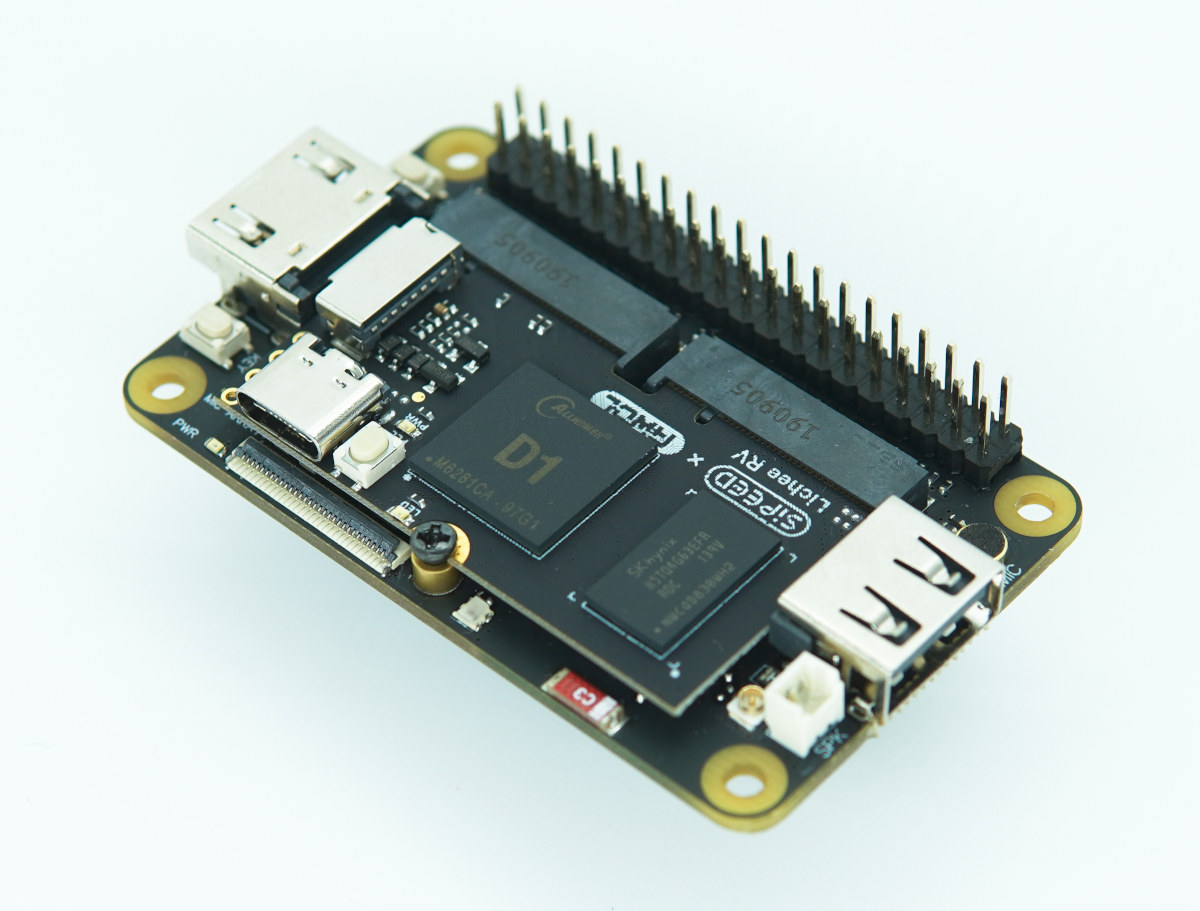

Sipeed Lichee RV RISC-V module gets $5+ carrier board with HDMI and USB ports, optional WiFi

Sipeed introduced the Lichee RV Allwinner D1 Linux RISC-V board going for just $17 with 512MB RAM last month. While with a USB-C port it could be used as a standalone part, its dual M.2 connector makes it more like a module and we noted a tiny carrier board was in the works at the time. The baseboard is now available and known as the Lichee RV Dock adding HDMI and USB ports, as well as a 40-pin GPIO header for just $5, or $8 if you’d like to get Wi-Fi 4 and Bluetooth 4.2 connectivity through a Realtek RTL8723DS module. Sipeed Lichee RV Dock specifications: Supported system-on-module (SoM) – Lichee RV module with Allwinner D1 RISC-V processor @ 1 GHz, 512MB DDR3, MicroSD card slot, and USB Type-C OTG port Storage – Optional SPI flash Display interfaces HDMI port up to 4Kp30 Optional RGB interface for up to 720p30 […]

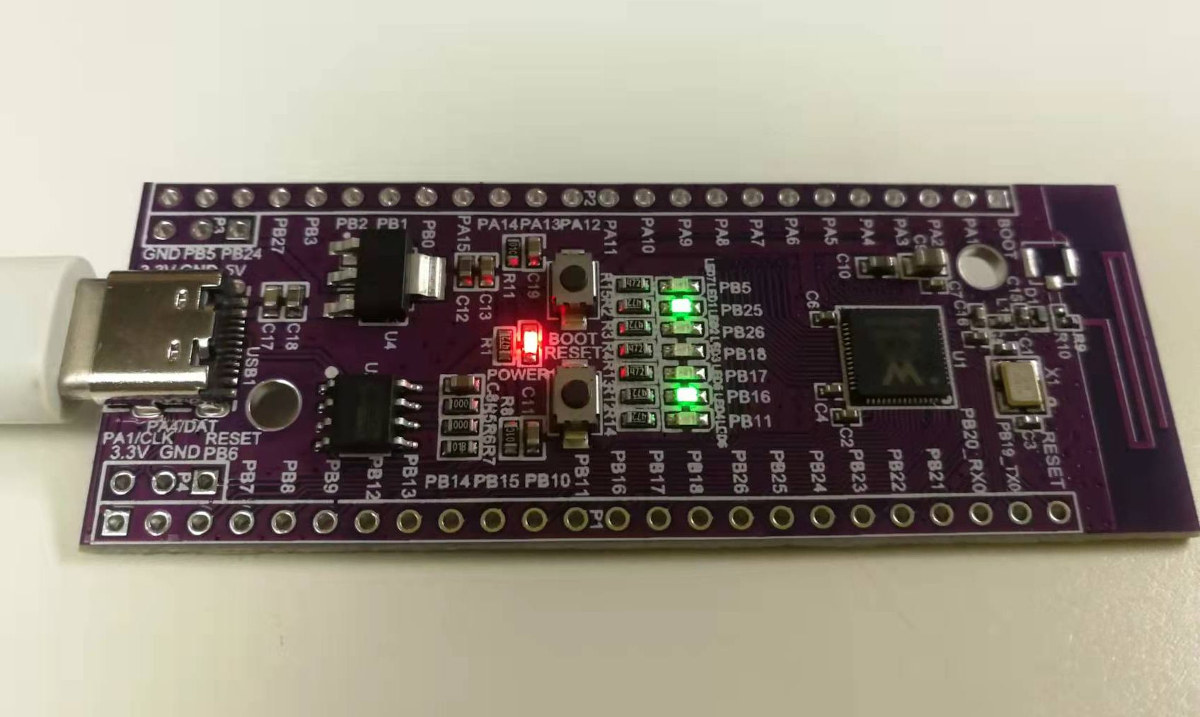

HLK-W801 board features Alibaba Xuantie XT804 based MCU with WiFi 4, Bluetooth LE 4.2

Earlier this month, we wrote about the 240 MHz WinnerMicro W806 Alibaba Xuantie XT804 C-Sky microcontroller with 1MB flash, 288KB SRAM found in the $2 HLK-W806 development board. But the company has a nearly identical WinnerMicro W801 microcontroller that bumps the internal flash to 2MB, and more importantly adds a 2.4 GHz radio with WiFi 4 and Bluetooth LE 4.2 connectivity, and HiLink also released the HLK-W801 board that’s nearly identical to HLK-W806, except for some extra LEDs, a USB-C port instead of a Micro USB port, and a longer form factor to make space for the PCB antenna. HLK-W801 board specifications: MCU – WinnerMicro W801 32-bit Alibaba XT804 microcontroller @ 240 MHz with 2MB Flash, 288KB RAM, FPU, DSP, crypto engine, 2.4 GHz radio Connectivity 802.11b/g/n WiFi 4 up to 150 Mbps supporting station, soft AP and station+soft AP modes, WPA2 security Bluetooth 4.2 Expansion – 2x 24-pin headers […]

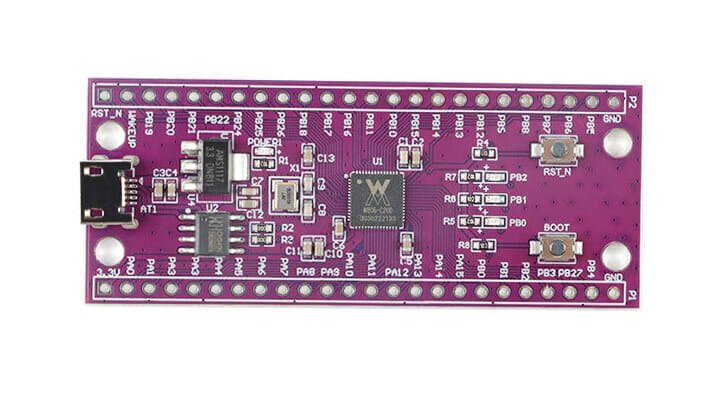

WinnerMicro W806 240 MHz MCU finds it way into a $2 development board

I’ve just been notified about an inexpensive board (HLK-W806) based on WinnerMicro W806 32-bit XT804 (XuanTie E804) microcontroller clocked at up to 240 MHz and equipped with 1MB flash and 288KB RAM. XuanTie is the microcontroller family from Alibaba’s subsidiary T-Head Semiconductor, notably XuanTie RISC-V cores, but I’ve just learned not all XuanTie cores are based on the RISC-V architecture, and as we’ll see below, Xuantie E804 core appears to be based on the C-Sky architecture. It may still be interesting, as it’s in the STM32 board price range (pre-2020), but with a much higher frequency, so let’s have a look. HLK-W806 development board specifications: MCU – WinnerMicro W806 32-bit XT804 microcontroller @ 240 MHz with 1MB Flash, 288KB RAM, FPU, DSP, crtypto engine Expansion – 2x 24-pin headers with (based on MCU specs) 1x SDIO host with support for SDIO 2.0, SDHC, MMC 4.2 1x SDIO device up to […]

Alibaba open sources four RISC-V cores: XuanTie E902, E906, C906 and C910

Alibaba introduces a range of RISC-V processors in the last few years with the Xuantie family ranging from the E902 micro-controller class core to the C910 core for servers in data centers. This also includes the XuanTie C906 core found in the Allwinner D1 single-core RISC-V processor. While RISC-V is an open standard and there’s a fair share of open-source RISC-V cores available, many commercial RISC-V cores are closed source, but Zhang Jianfeng, President of Alibaba Cloud Intelligence speaking at the 2021 Apsara Conference, announced that T-Head had open-sourced four RISC-V-based Xuantie series processor cores, namely Xuantie E902, E906, C906, and C910, as well as related software and tools. Those are not empty words as we can find the RTL for the four cores released on T-Head Semiconductor’s Github account with the first commits having taken place yesterday. Each repository contains the code and instructions to get started, all under […]