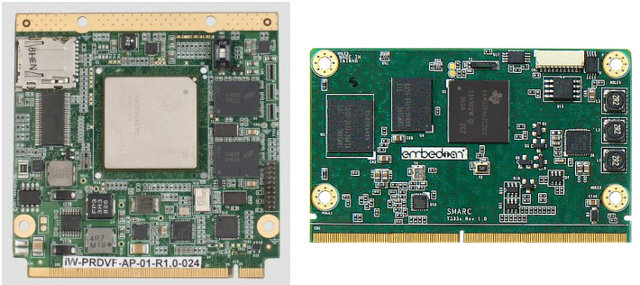

A System-on-Module (SoM), also known as a Computer-on-Module (CoM), is a small board with the key components of a computer such as SoC, memory, and possibly others components such as PMIC (Power Management IC), an Ethernet PHY, as well as one or more connectors used to connect to a baseboard, also called carrier board, which features standard ports such as Ethernet (RJ45), USB ports, SATA, power jack and so on. The advantages of using of baseboard + SoM design compared to a single board are at least twofold: Most of the PCB design complexity is often around the CPU/SoC and high-speed buses connected to the CPU/SoC. So you could buy an SoM, design your own baseboard and get a complete design relatively in a short amount of time, with reduced development resources and costs. The design is modular, so you could easily upgrade from one SoM to another one. For […]

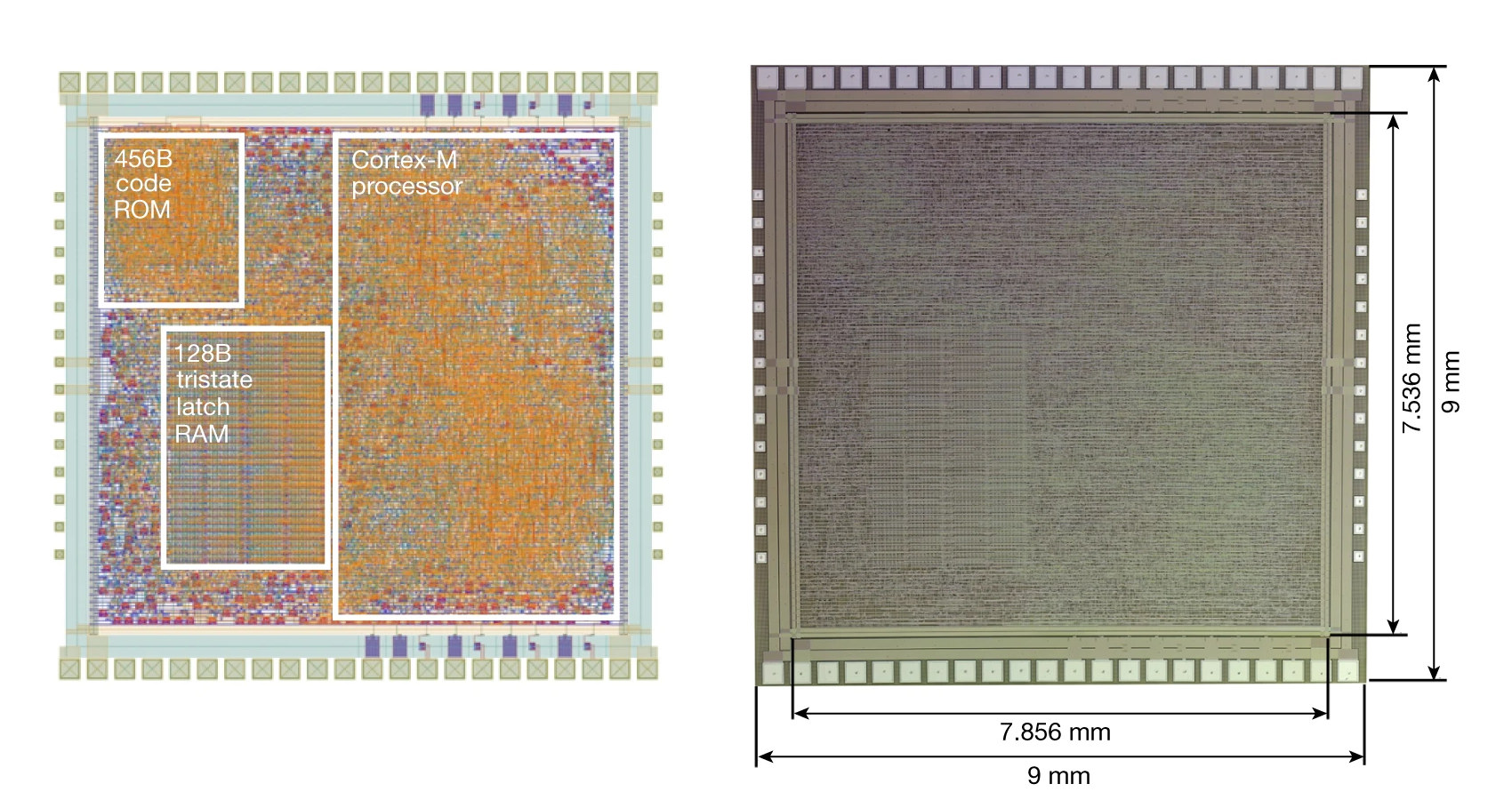

PlasticArm is a functional, non-silicon, flexible Cortex-M0 microcontroller

Four years ago, we wrote about PragmatIC’s ultrathin and flexible plastic electronics circuit, with news that an ultra-cheap ARM Cortex M0 MCU made of plastic materials was coming soon. In this case, “soon” means about four years, but Arm has now finally announced PlasticArm, an ultra-minimalist, fully functional Cortex-M0-based SoC, with 128 bytes of RAM and 456 bytes of ROM that, with 18,000 gates, is twelve times more complex than previous state-of-the-art flexible electronics. PlasticArm specifications are similar to a standard Cortex-M0+ core with some notable exceptions: Cortex-M core in PlasticARM ARMv6-M architecture ISA – 16-bit Thunb and subset of 32-bit Thumb 32-bit data access and address width 86 instructions 2-stage pipeline Architectural register file mapped to RAM external to the CPU (instead of inside the CPU) Runs code from other Cortex-M CPUs 0.8-μm process There are two main advantages of PlasticArm. First, It’s flexible and integrated into paper, plastic, […]

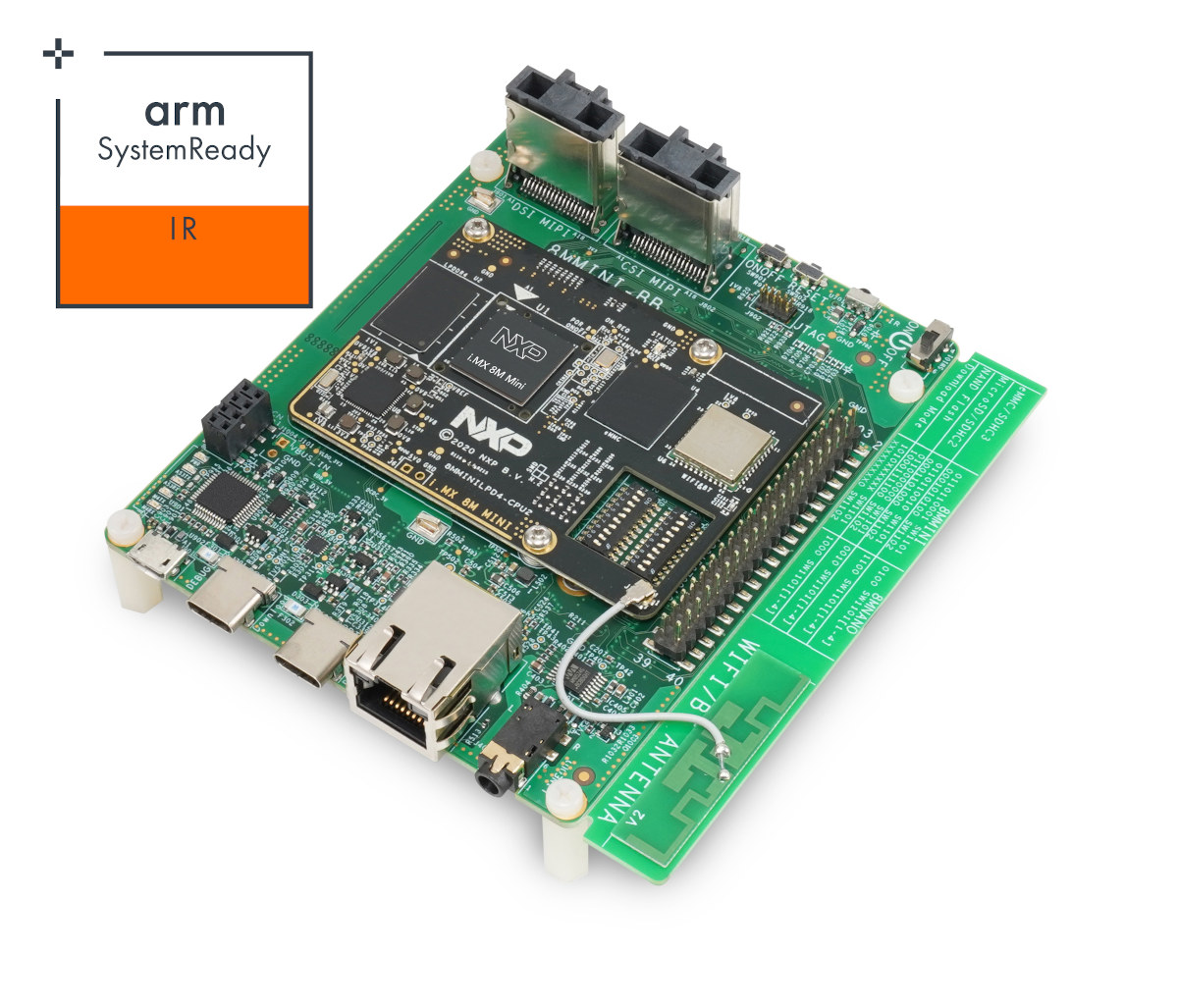

The first Arm SystemReady IR certified platforms – NXP i.MX 8M Mini EVK & Compulab IOT-GATE-IMX8 gateway

A few months ago, we noted SolidRun HoneyComb LX2K became a certified Arm SystemReady ES platform. SystemReady is a certification program by Arm that ensures systems just work with generic operating systems like in the x86 world. When we looked at the details of the program in the article, we noted there were different categories including SystemReady ES for embedded servers and SystemReady IR for IoT Edge applications. The first SystemReady IR platform – NXP i.MX 8 Mini evaluation kit Arm has just announced the first SystemReady IR platform had just been certified. That device is the NXP i.MX 8M Mini EVK, and that means that anyone that uses the i.MX 8M family of devices with the associated Board Support Package (BSP) can build platforms that will pass the same certification process and boot compliant Linux distributions with minimal integration effort. We can see more details about the certifications on Arm developer’s website. NXP i.MX 8M Mini EVK achieved certification with NXP 2021 Q2 pre-release firmware, version LF […]

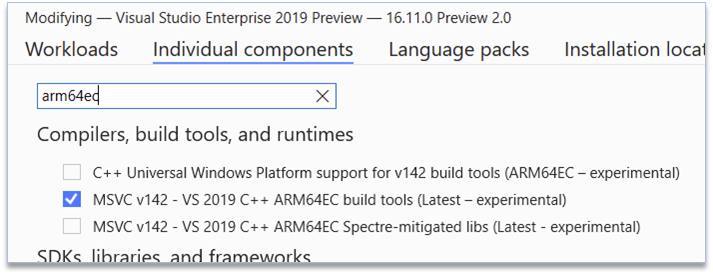

ARM64EC mixes Arm and x64 emulated code in Windows 11 for higher performance on Arm

Windows has been available on Arm for a few years, and while software support has progressed there have always been some limitations, and emulated x86/x64 code on Arm does not usually run as fast as native ARM32/ARM64 code. So far developers had a binary choice: run their x86/x64 app on Arm using emulation, or port the entire app to Arm, But Microsoft has now come up with a solution that mixes x64 emulation and native Arm with ARM64EC (Emulation Compatible). That means developers won’t need to port the complete app to Arm, but instead could do so step-by-step and focus on part of the code where native Arm support makes the most difference. Microsoft explains: ARM64EC is a new application binary interface (ABI) for Windows 11 on ARM that runs with native speed and is interoperable with x64. An app, process, or even a module can freely mix and match […]

Linux 5.13 Release – Notable changes, Arm, MIPS and RISC-V architectures

Linus Torvalds has just announced the release of Linux 5.13: So we had quite the calm week since rc7, and I see no reason to delay 5.13. The shortlog for the week is tiny, with just 88 non-merge commits (and a few of those are just reverts). It’s a fairly random mix of fixes, and being so small I’d just suggest people scan the appended shortlog for what happened. Of course, if the last week was small and calm, 5.13 overall is actually fairly large. In fact, it’s one of the bigger 5.x releases, with over 16k commits (over 17k if you count merges), from over 2k developers. But it’s a “big all over” kind of thing, not something particular that stands out as particularly unusual. Some of the extra size might just be because 5.12 had that extra rc week. And with 5.13 out the door, that obviously means […]

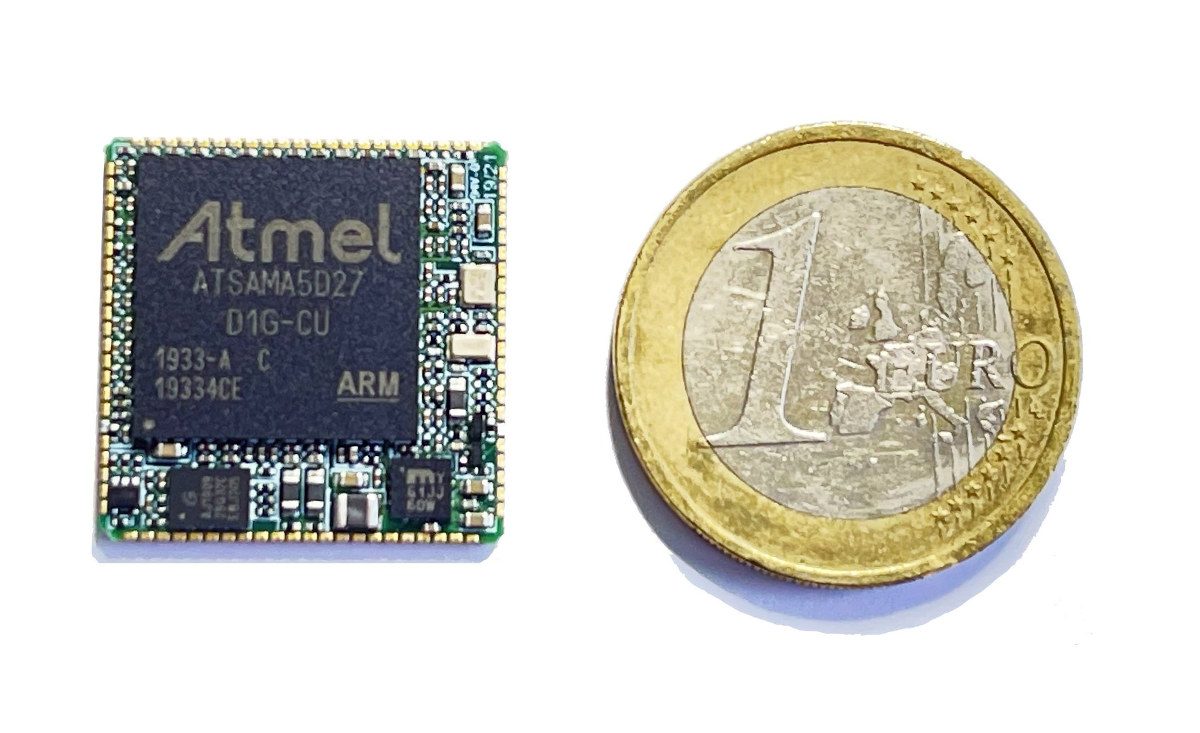

HaneSOM is a 4 cm2 Arm Linux module powered by Microchip SAMA5D2 SiP

DAB Embedded HaneSOM is a tiny (4 cm2) system-on-module based on Microchip SAMA5D2 Arm Cortex-A5 processor running Linux, which could make it the world’s smallest Linux module. The small size is made possible by the use of a SAMA5D2 system-in-package that also integrates 128MB DDR2, and the only two other chips on the modules are a 4MB flash (GD25Q32) and the PMIC (MIC2800). HaneSOM specifications: SiP – Microchip ATSAMA5D27C-D1G system-in-package with SAMA5D27 Arm Cortex-A5 processor @ 500 MHz with NEON, 128MBytes DDR2 System Memory – 128MBytes DDR2 memory Storage – 4 MBytes of QSPI Flash Castellated holes giving access to signal for: Storage – SD card interface Display – 24-bit RGB LCD TFT interface; capacitive touch controller Camera – Up to 5MP CMOS camera sensor support Audio – SSC, I2S Networking – 10/100M Ethernet USB – USB 2.0 (OTG and host) SPI, I2C, UART, CAN-FD, 12-bit ADC, PWM Misc – […]

Panfrost now supports OpenGL ES 3.1 on Midgard (Mali T760 and newer) and Bifrost (Mali G31, G52, G76) GPUs

OpenGL ES 3.0 experimental support for Panfrost open-source Arm Mali GPU driver was announced in February 2020 and culminate with the release of Mesa 20.3 with Panfrost support last December. Collabora has now started to work on Panvk, Panfrost Vulkan driver, but that does not mean OpenGL ES work is done, and the company has just published a blog post about OpenGL ES 3.1 support in Panfrost. Alyssa Rosenzweig explains OpenGL ES 3.1 extends to both the older Midgard GPUs that include Mali T760 and newer version, and the more recent Bifrost GPUs with Mali-G31, Mali-G52 and Mali-G76. Compared to OpenGL ES 3.0, OpenGL ES 3.1 adds compute shaders, indirect draws, and no-attachment framebuffers. Boris Brezillon, Italo, Nicola, Alyssa, and the wider Mesa community especially focused on Mali-G52 GPU, found for instance in Amlogic A311D and Rockchip RK3566, with Panfrost driver passing essentially all of drawElements Quality Program and Khronos […]

Arm introduces Open-CMSIS-Pack and Keil Studio Cloud for MCU software development

Arm has just announced two new initiatives that aim to boost the productivity embedded, IoT, ML, and MCU software developers: the Open-CMSIS-Pack project and Keil Studio Cloud. The Open-CMSIS-Pack Project The Cortex Microcontroller Software Interface Standard (CMSIS) packs have been around for years providing a vendor-independent hardware abstraction layer for microcontrollers, mostly Cortex-M based, but others too, and currently support close to 9000 different microcontrollers. I always assumed CMSIS was open-source as the source code is available in Github under an Apache 2.0 license. But apparently, not all components are, and Arm has now announced the Open-CMSIS-Pack project that will move part of CMSIS into the open project in collaboration with the Linaro IoT and Embedded Group. Linaro, Arm, and other partners like STMicro and NXP will initially focus their work on command-line tools and CMake workflows, with the ultimate goal of making the CMSIS-Pack technology into a true open […]