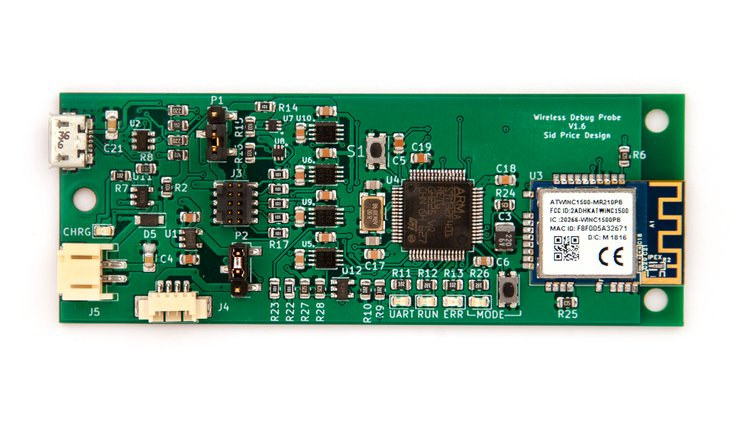

Last month, we wrote about Blip nRF52840 dev board that also included an STM32F103 MCU running the open source Black Magic Probe (BMP) firmware for debugging and programming. Based on the original Black Magic Probe hardware product page, BMP is a JTAG and SWD adapter used for programming and debugging ARM Cortex MCUs, and does not require intermediate programs such as OpenOCD or STLink server. Instead, you can run GNU Debugger (GDB) and select the virtual COM port offered by the debug board. The reason I’m bringing BMP again today, is because a new open source hardware wireless debugging probe for Cortex-M based on Black Magic Probe has been launched in the last few days. ctxLink key features and specifications: Microcontroller – STMicro STM32F401RE Arm Cortex -M4F MCU at up to 84 MHz Connectivity – 802.11b/g/n WiFi via Microchip WINC1500 module USB – 1x micro USB port for connection to […]

Linux 5.3 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds has just announced the release of Linux 5.3: So we’ve had a fairly quiet last week, but I think it was good that we ended up having that extra week and the final rc8. Even if the reason for that extra week was my travel schedule rather than any pending issues, we ended up having a few good fixes come in, including some for some bad btrfs behavior. Yeah, there’s some unnecessary noise in there too (like the speling fixes), but we also had several last-minute reverts for things that caused issues. One _particularly_ last-minute revert is the top-most commit (ignoring the version change itself) done just before the release, and while it’s very annoying, it’s perhaps also instructive. What’s instructive about it is that I reverted a commit that wasn’t actually buggy. In fact, it was doing exactly what it set out to do, and did it […]

How to Sandbox an arm64 GCC on aarch64 Hardware with armv7 Userspace

CNXSoft: Guest post by Blu about setting up arm64 toolchain on 64-bit Arm hardware running a 32-bit Arm (Armv7) rootfs. Life is short and industry progress is never fast enough in areas we care about. That’s an observation most of us are familiar with. One would think that by now most aarch64 desktops would be running arm64 environments, with multi-arch support when needed. Alas, as of late 2019, chromeOS on aarch64 is still shipping an aarch64 kernel and an armhf userspace. And despite the fine job by the good folks at chromebrew, an aarch64 chromeOS machine in dev mode ‒ an otherwise excellent road-warrior ride, is stuck with 32-bit armhf. Is that a problem, some may ask? Yes, it is ‒ aarch64 is the objectively better arm ISA outside of MCUs, from gen-purpose code to all kinds of ISA extensions, SIMD in particular. That shows in contemporary compiler support and […]

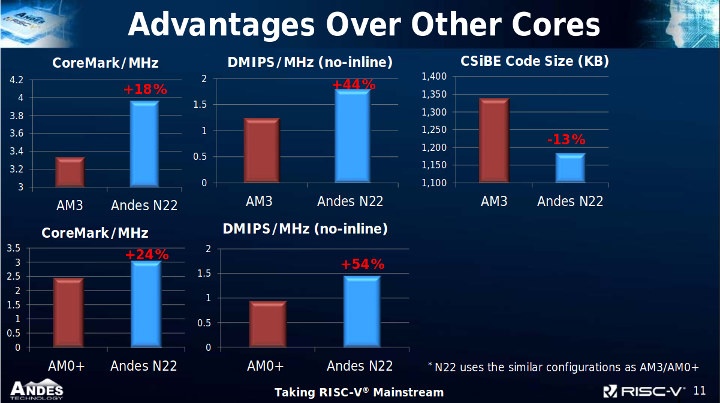

AndesCore N22 RISC-V Core Supports RV32IMAC or RV32EMAC Instruction Sets

We covered Gigadevice GD32V general-purpose microcontroller with a RISC-V “Bumblebee” core last week, and I was informed that Andes Technology had recently introduced AndesCore N22 RISC-V “Bumblebee” IP core capable of supporting either RV32IMAC or RV32EMAC instruction sets. A web search did not reveal any specific information about what “Bumblebee” RISC-V cores are exactly, or maybe it’s in reference that many can be coupled in parallel. But that’s just a small detail, let’s check out in some details what AndesCore N22 core has to offer. The RISC-V core is designed for entry-level MCUs found in IoT devices and wearables, and is capable of deeply embedded protocol processing for I/O control, storage, networking, AI and AR/VR. Highlights of AndesCore N22: AndeStar V5 (RV32IMAC) / V5e (RV32EMAC) Instruction Set Architecture (ISA), compliant to RISC-V technology plus Andes extensions architectured for performance and functionality enhancements 32-bit, 2-stage pipeline CPU architecture 16/32-bit mixable instruction […]

Linaro Connect San Diego 2019 Schedule – IoT, AI, Optimizations, Compilers and More

Linaro has recently released the full schedule of Linaro Connect San Diego 2019 that will take place on September 23-27. Even if you can’t attend, it’s always interested to check out the schedule to find out what interesting work is done on Arm Linux, Zephyr OS, and so on. So I’ve created my own virtual schedule with some of the most relevant and interesting sessions of the five-day event. Monday, September 23 14:00 – 14:25 – SAN19-101 Thermal Governors: How to pick the right one by Keerthy Jagadeesh, Software Engineer, Texas Instruments With higher Gigahertz and multiple cores packed in a SoC the need for thermal management for Arm based SoCs gets more and more critical. Thermal governors that define the policy for thermal management play a pivotal role in ensuring thermal safety of the device. Choosing the right one ensures the device performs optimally with in the thermal budget. […]

Samsung Galaxy Book S Snapdragon 8cx Laptop to Launch soon for $1,000

Qualcomm Snapdragon 8cx was announced as the first Snapdragon processor specifically designed for connected mobile PCs (aka laptops with cellular connectivity) last December. Earlier this year we got confirmation 8cx would support 5G connectivity as an option, and in May, we got news Lenovo Limitless 5G laptop was coming and got some benchmarks showing Snapdragon 8cx with performance similar to an Intel Core i5 Kaby Lake-R processor (15 Watt TDP) while offering much longer battery life. It’s Samsung turn to announce their Snapdragon 8cx laptop with Samsung Galaxy Book S that will be available this fall for $999 and up. Samsung Galaxy Book S specifications: SoC – Qualcomm Snapdragon 8cx Compute Platform with eight 64-bit Armv8 cores in two clusters: Kryo 495 Gold cores (Cortex-A76 class) @ 2.84 GHz + Kryo 495 cores (Cortex-A55 class) @ 1.8GHz ; 7nm process; 7W TDP System Memory – 8GB RAM (LPDDR4X) Storage – […]

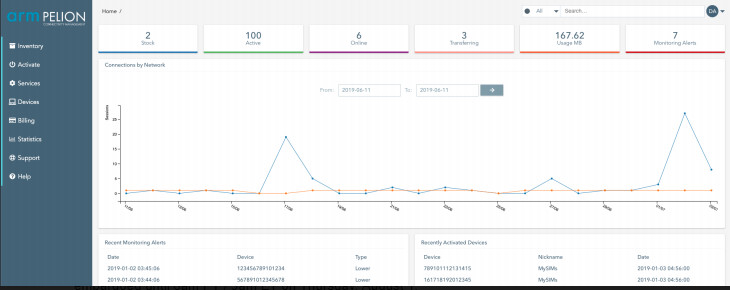

Arm Releases Pelion Connectivity Management 2.0 Platform with Greater Automation

Arm has announced its latest version of Pelion IoT Platform, a no-upgrade needed platform Pelion Connectivity Management 2.0 a SaaS with an automation engine. Previously, we reported on the Sigma Delta Technologies modular devkit that was designed to work with the cloud-based Arm Pelion 1.0 device management service through the Mbed OS, focused on IoT development. The Pelion Connectivity Management 2.0 adds a level of automation that the Pelion 1.0 didn’t have, but that the company felt the customer base in the IoT industry wanted. The new features expand on the Pelion platform, through the Mbed OS, which helped the platform expand through cloud-based management services. The loudest voices in the ever-expanding and transforming IoT industry have said that automation is the key to removing barriers that allow IoT to scale. Pelion 1.0 already offered a single, cloud-based connectivity solution for managing IoT devices. Pelion 2.0 allows IoT devices to […]

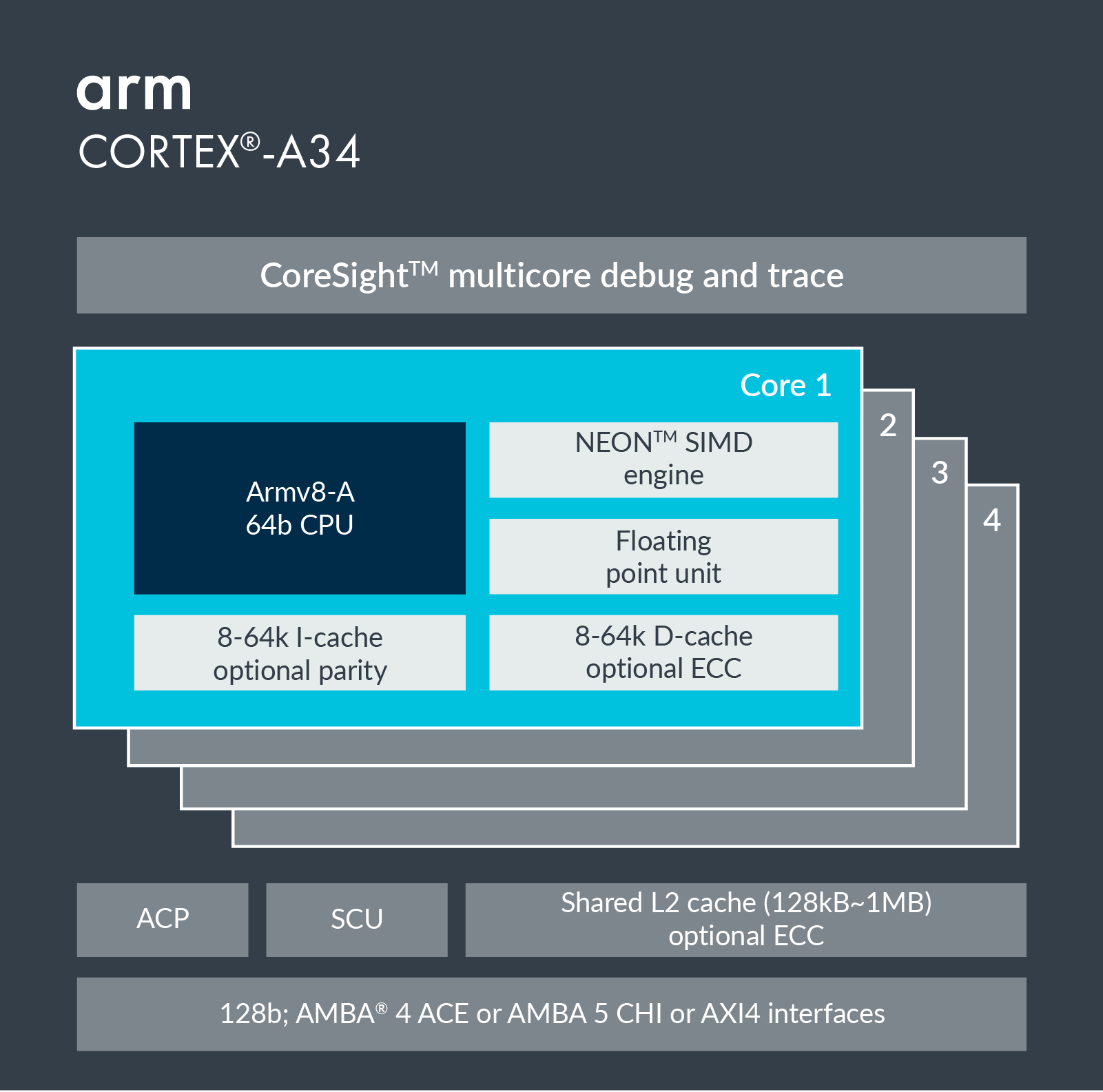

Arm Cortex-A34 is a 64-bit Only Low-Power Core

Arm previously announced Cortex-A35 64-bit & 32-bit lower-power CPU core, and later on Cortex-A32 32-bit only Armv8 CPU core with the usual press release, and blog posts providing details about their new offering. But this morning, I saw a tweet about Cortex-A34… https://twitter.com/never_released/status/1157107187375886337 Based on the twitter handle, I first assumed it was “never released” ;), and was just an internal part name at Arm. But the new Cortex-A34 was actually very discreetly outed last month when Arm announced Flexible Access to lower the barrier of entry by allowing IC designers to access all Arm IP in the program, and only pay for IP blocks they actually use in the final product. Nevertheless, the product page and developer documentation are now up – albeit with limited info for the latter -, so we have more details. Some of the highlights of Arm Cortex-A34 core include: Architecture – 64-Bit Armv8-A Multicore […]