We covered Gigadevice GD32V general-purpose microcontroller with a RISC-V “Bumblebee” core last week, and I was informed that Andes Technology had recently introduced AndesCore N22 RISC-V “Bumblebee” IP core capable of supporting either RV32IMAC or RV32EMAC instruction sets.

A web search did not reveal any specific information about what “Bumblebee” RISC-V cores are exactly, or maybe it’s in reference that many can be coupled in parallel. But that’s just a small detail, let’s check out in some details what AndesCore N22 core has to offer. The RISC-V core is designed for entry-level MCUs found in IoT devices and wearables, and is capable of deeply embedded protocol processing for I/O control, storage, networking, AI and AR/VR.

- AndeStar V5 (RV32IMAC) / V5e (RV32EMAC) Instruction Set Architecture (ISA), compliant to RISC-V technology plus Andes extensions architectured for performance and functionality enhancements

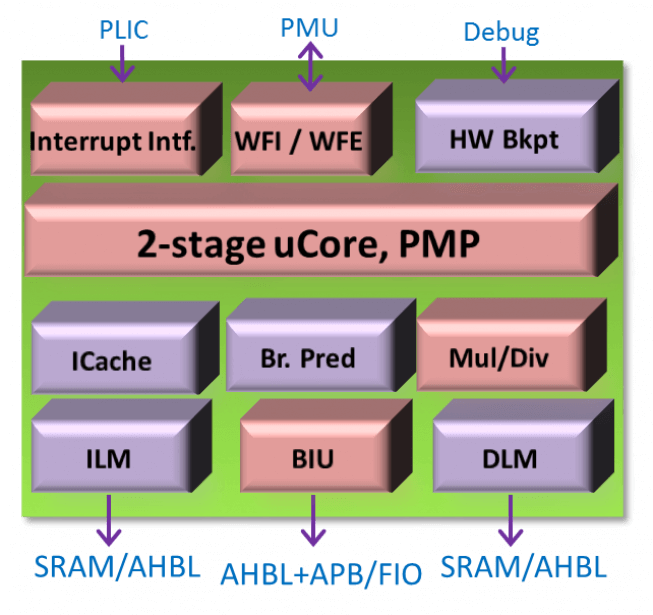

- 32-bit, 2-stage pipeline CPU architecture

- 16/32-bit mixable instruction format for compacting code density

- Branch prediction to speed up control code

- Configurable Multiplier

- Physical Memory Protection (PMP)

- Core-Local Interrupt Controller (CLIC) with selective vectoring and priority preemption

- Flexibly configurable Platform-Level Interrupt Controller (PLIC) for supporting SoC with multiple processors

- Advanced CoDense technology to reduce program code size

- StackSafe hardware to help measuring stack size, and detecting runtime overflow/underflow

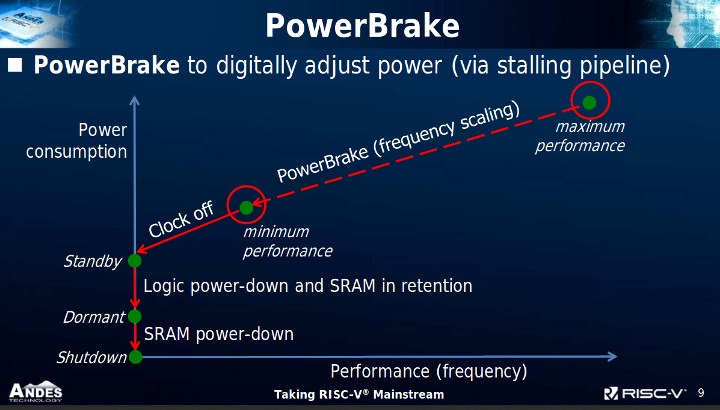

- PowerBrake to digitally adjust power (via stalling pipeline)

- Several configurations to tradeoff between core size and performance requirements

A recent presentation in English gives us more details, and for instance, the claim is made that AndesCore N22 has “excellent PPA (Power, Performance, and Area)”:

- Min. useful configuration: < 15K gates

- Dynamic power: 1.36 uW/MHz @ 28nm

- Performance: 3.95 CoreMark/MHz

- Max. frequency: up to 700 MHz @ worst case

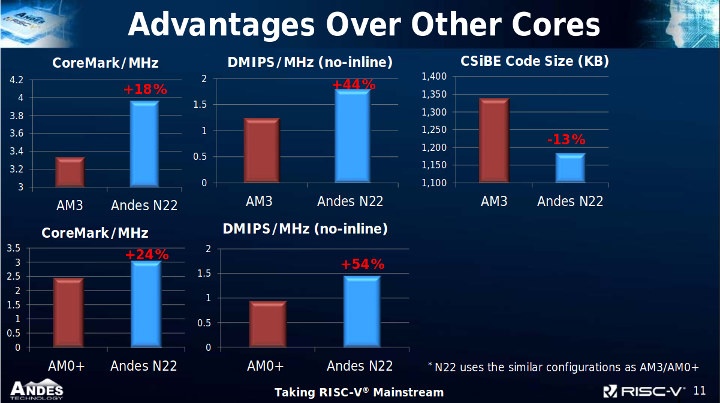

The document also shows the performance, footprint (code size), and efficiency of Andes N22 RISC-V core against Arm Cortex-M3 and M0+ cores in a similar configuration.

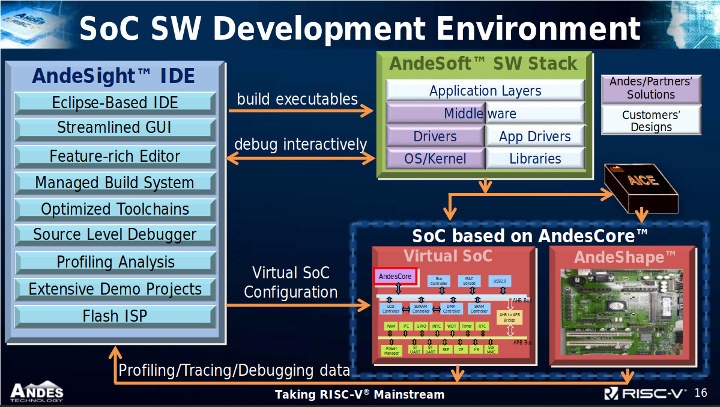

Andes is also providing development tools including the free to download AndeSight Eclipse-based IDE, AndeSoft Software Stack, as well as two AndeShape FPGA based development boards, namely the Arduino compatible Corvette-F1 board and the full-featured ADP-XC7K development kit, and debugging hardware such as AICE-MINI+ and AICE-MICRO.

AndesCore N22 core is officially supported by GNU and LLVM communities, several optimized libraries such as MCUlib and newlib, and samples programs are available. The new RISC-V MCU core supports the open-source FreeRTOS, and the commercially supported Express Logic ThreadX real-time operating systems. The company also mentions “RISC-V Ready” operating systems such as Zephyr, RT-Thread, μC/OS-II, MyNewt, SylixOS, LiteOS, or AliOS Things, which as I understand it may not be officially supported (yet), but already work with generic RISC-V cores.

You may find more details on the product page, and if your mandarin is up to speed, you may want to watch the video below accompanying the aforelinked presentation.

Thanks to Blu for the tip

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress. We also use affiliate links in articles to earn commissions if you make a purchase after clicking on those links.

Is there any available MCU or product using this at 28nm??

https://github.com/nucleisys/Bumblebee_Core_Doc has some more information about the Nucleisys Bumblebee (in Chinese). Here is the Google Translate version of the introductory section:

“Bumblebee kernel instruction set and CSR introduction

Bumblebee Processor Core, referred to as the Bumblebee kernel, is powered by Coree Technology (Nuclei System Technology) Gigadevice for its general purpose MCU for IoT or other ultra-low power scenarios. A commercial RISC-V processor core customized for the MCU product model GD32VF103.

For an introduction to the hardware features of the Bumblebee kernel, see the Bumblebee Kernel Concise Data Sheet. A detailed introduction to the instruction architecture it supports.

Note: The Bumblebee core used for this MCU is Nuclei System Technology and Taiwan. Co-developed by Andes Technology, licensed by Nuclei System Technology. And technical support and other services.

At present, Nuclei System Technology can authorize the completely low-power consumption of the fully self-controllable N200 series. Commercial processor core IP, as well as multiple families (300/600/900 series) 32-bit architecture and 64-bit architecture for high-performance embedded Processor core IP and provide processor IP customization services to customers.

Note: For more comprehensive information on RISC-V MCU chips, boards and solutions, please visit http://www.riscv-mcu.com“

There’s english ‘user guide’ and ‘datasheet’ documents for the bumblebee core at http://dl.sipeed.com/LONGAN/Nano/DOC/ also. The font/layout is pretty tough to read, though (at least in the built-in firefox pdf reader).

I think the name Bumblebee is probably just the codename used by Nucleisys for their N20x-series of cores (https://www.nucleisys.com/product.php). They called their (earlier?) educational/open-source E20x-series of cores the ‘Hummingbird’ (which was included as an example softcore with the Lichee Tang / Sipeed Tang Premier FPGA boards: https://www.cnx-software.com/2018/09/04/licheetang-anlogic-eg4s20-fpga-board-targets-risc-v-development/). From the series-numbers I suppose the N20x is an enhanced commercialization of the E20x. Perhaps things-that-feed-on-flowers are the ‘genre’ they’re using for codenames, like Intel uses lakes and Apple uses Californian landmarks.