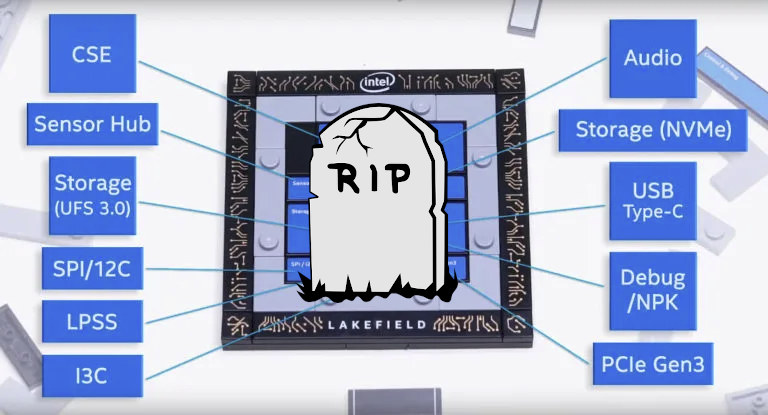

Intel launched Core i3-L13G4 and Core i5-L16G7 penta-core Lakefield Hybrid processors last year with one high-performance Sunny core, and four high-efficiency Atom Tremont cores, in a way that’s similar to what Arm is doing with DynamIQ and before that, big.LITTLE technology. The new processors were found in Lenovo ThinkPad X1 Fold foldable tablet and Samsung Galaxy Book S laptop, both premium products sold for over $2,000. Even some large websites never got hold of a testing sample of those products, and Anandtech has just reported that Intel published a product change notification (PCN) with the title “Select Intel Core Processors with Intel Hybrid Technology, PCN 118334-00, Product Discontinuance, End of Life”. The discontinuance of Lakefield hybrid processors is a shocker considering they were just introduced last year, but I don’t think it will affect many people as I hadn’t heard about any upcoming boards or products based on Intel’s hybrid […]

Intel Launches Core i3/i5 Penta-Core Lakefield Hybrid Processors

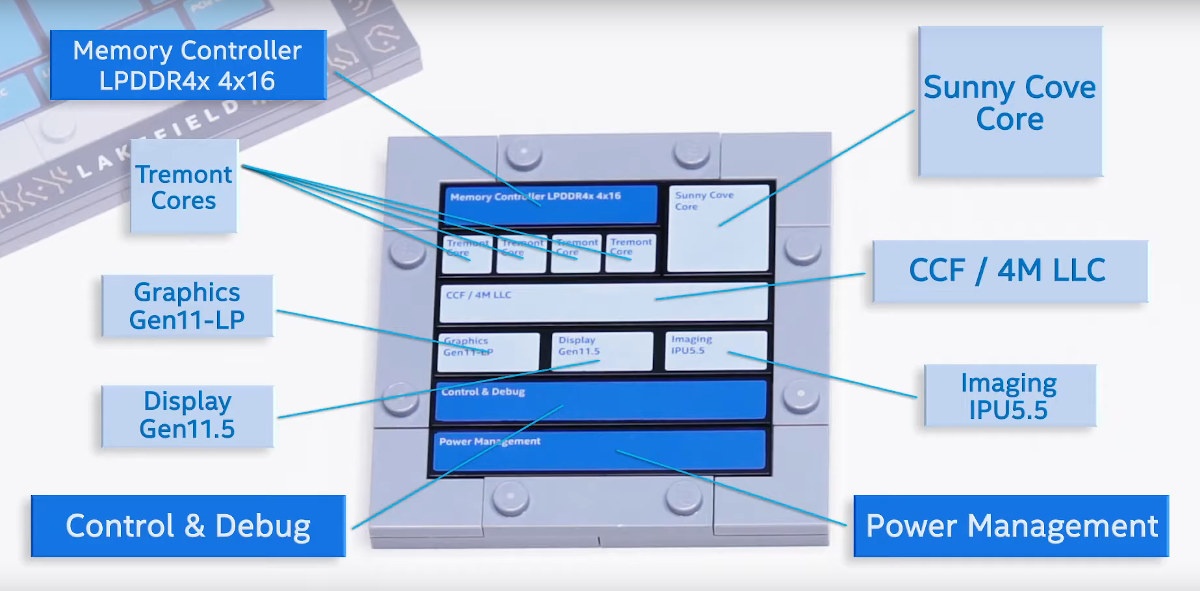

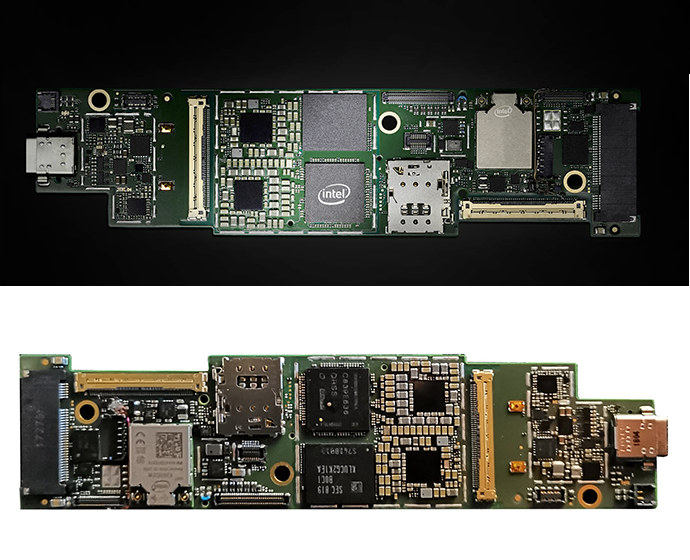

Intel unveiled plans for Lakefield Hybrid processors last year which combined a high-performance Sunny Cove core with four low-power Atom cores using Foveros 3D stacking technology and offering high peak single-thread performance and low power consumption for most tasks in a similar way to Arm’s big.LITTLE or DynamIQ technology. The company has now launched the first two penta-core Lakefield hybrid processors with Core i5-L16G7 and Core i3-L13G4 processors both with a 7W SDP (Scenario Design Power), but no TDP number which makes sense considering the Hybrid nature of the processor. Main features and specifications of the processors: Intel Core i3-L13G4 CPU – 1x high-performance Sunny Cove core @ 800 MHz / 2.8 GHz (Boost), 4x low-power Atom Tremont cores; All-core turbo boost: 1.3 GHz 4 MB Cache GPU – 48EU Intel UHD Graphics Gen11-LP @ 200 / 500 MHz with DX12, OpenGL4.5 API, and up to 4x independent displays Intel […]

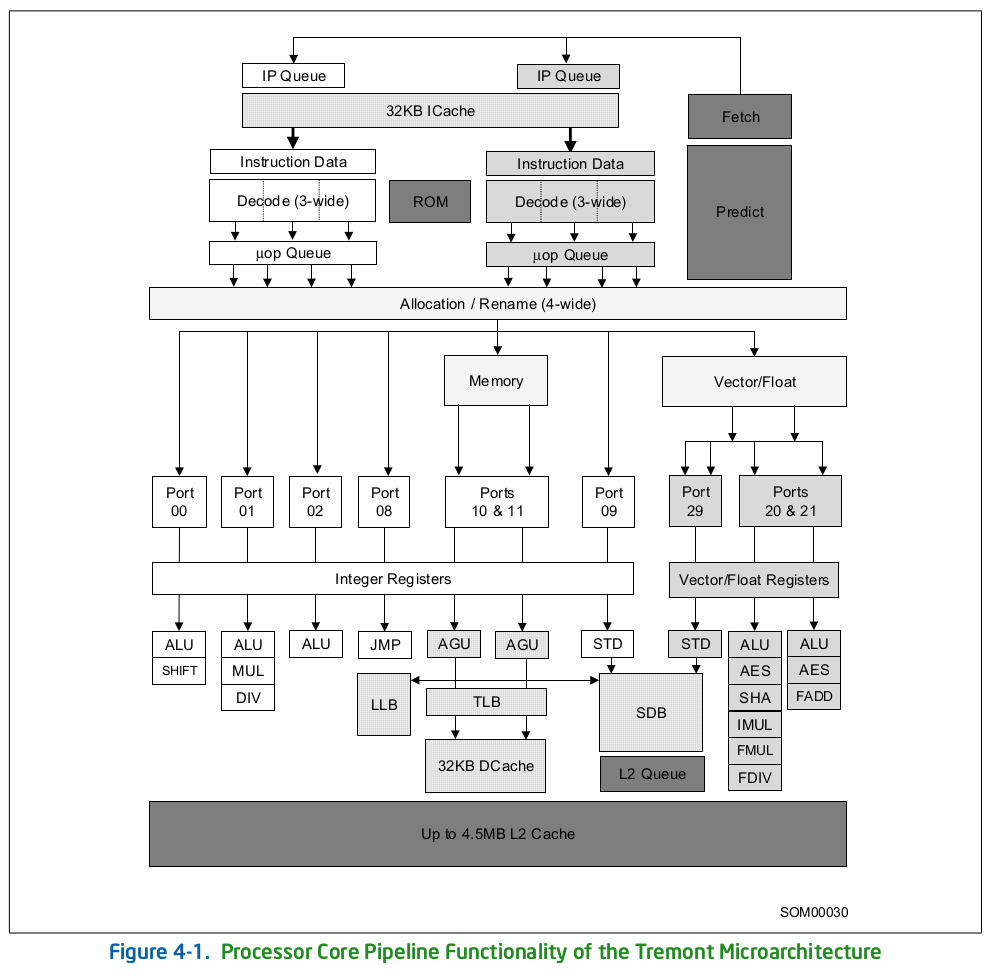

Updated x86/x64 Software Optimization Manual Reveals More Intel Tremont Details

We first found out about Tremont microarchitecture in April 2018 in some Intel documents and Linux mainline source showing it was likely meant to be Goldmont Plus successor. Last year, Intel formally announced Tremont architecture providing some of the details with a block diagram and key features. But this morning, we were informed by email of a new revision of the x86/x64 Software Optimization Manual (PDF) with even further details about Tremont architecture. If you want to know all the details, jump to 4.1 Tremont Architecture section of the document, but here are some of the highlights / improvements over Golmond Plus microarchitecture: Enhanced branch prediction unit. Increased capacity with improved path-based conditional and indirect prediction. New committed Return Stack Buffer. Clustered 6-wide out-of-order front-end fetch and decode pipeline. Banked ICache with dual 16B reads. Two 3-wide decode clusters enabling up to 6 instructions per cycle. Deeper back-end out-of-order windows. […]

Intel Unveils Tremont Low-power x86 Architecture, Lakefield Hybrid Processor

Intel Tremont microarchitecture was first leaked in April 2018 as a successor to Goldmont Plus used in Gemini Lake processors among others. But Intel has now made it official and revealed details about Tremont architecture at Linley Fall Processor Conference in Santa Clara, California. The new architecture is said to deliver significant IPC (instructions per cycle) gains compared with Intel’s prior low-power x86 architectures. Tremont-based processors will target client devices, IoT products, 5G networking, efficient datacenter servers, etc… Tremont Architecture Some of the highlights of Tremont architecture include: Intel Core class branch prediction with long history,32 bytes based, L1 predictor (no penalty) and large L2 predictor Out of order fetch – 32KB instruction cache, 32 bytes/cycle, up to 8 outstanding misses 6-wide out of order instruction decode Dual 3-wide clusters Wide decode without the area of a uop cache Optional single cluster mode based on product targets 4 wide allocation […]