ClockworkPi DevTerm retro-looking modular portable Linux computer has gotten a 64-bit RISC-V module based on Allwinner D1 1GHz SoC and offers an alternative to existing Arm-based modules such as Raspberry Pi CM3, or alternatives powered by Allwinner H6 or Rockchip RK3399 SoC’s. The new DevTerm Kit R-01 modular & portable terminal has exactly the same specifications with a 6.8-inch IPS screen, a keyboard with 67 keys, and a battery module, all connected to ClockworkPi v3.14 carrier board, but replaces the Arm modules with the R-01 module equipped with the Allwinner D1 processor and 1GB of RAM. DevTerm Kit R-01 kit items: SoM – R-01 Core module with Allwinner D1 single-core 64-bit RISC-V RV64IMAFDCVU processor @ 1.0GHz without GPU, and 1GB DDR3 Carrier board – ClockworkPi v3.14 mainboard Storage – 32GB MicroSD card preloaded with clockworkOS Display – 6.86-inch IPS screen module Audio – Dual speaker Keyboard – Clockwork 65% keyboard […]

Renesas introduces RZ/Five Linux-capable 64-bit RISC-V microprocessor family

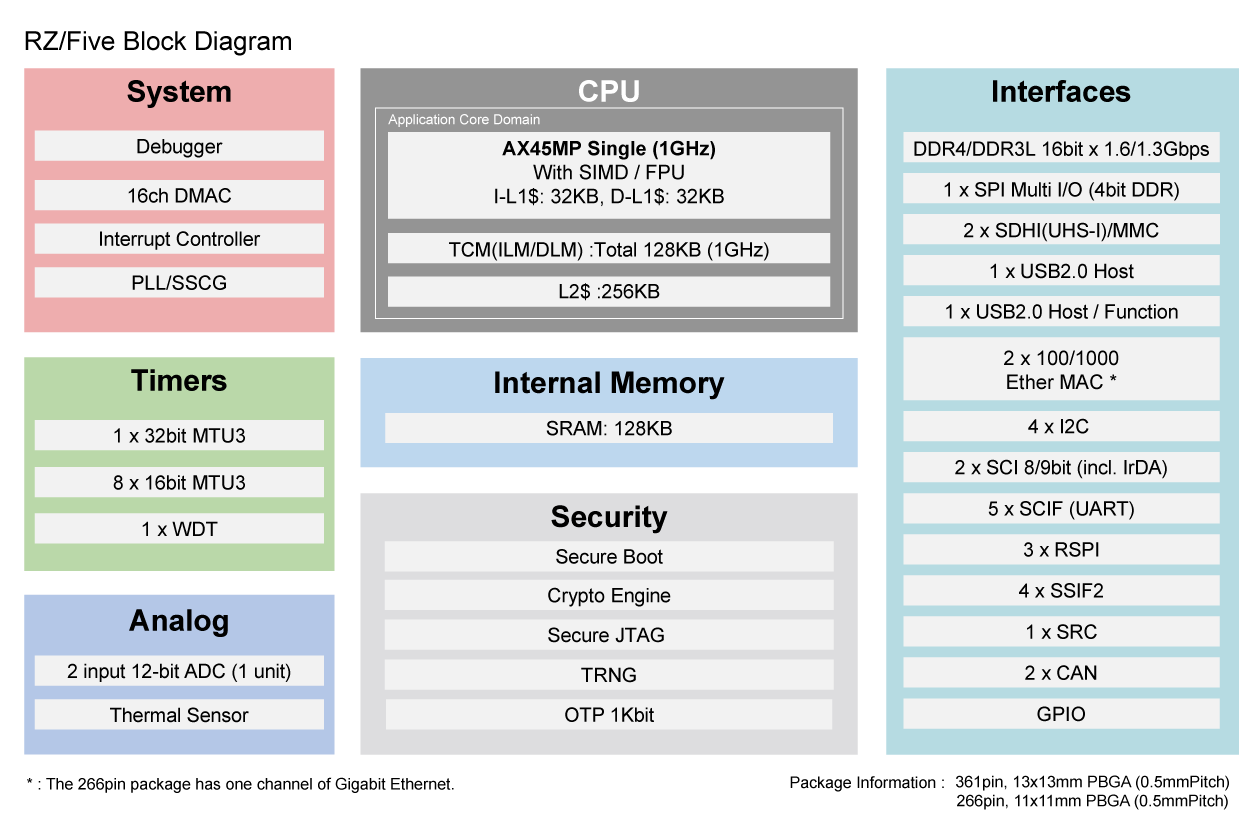

Renesas has launched its first RISC-V processor family with the RZ/Five general-purpose microprocessors based on an Andes AX45MP 64-Bit RISC-V CPU core, and with long-term Linux support via the industrial-grade CIP Linux that offers maintenance for over 10 years. The RISC-V processor is pin-to-pin compatible with the Arm Cortex-A55/M33–based RZ/G2UL processor family, and while being a general-purpose family, the RZ/Five chips are specifically well-suited to IoT endpoint devices such as gateways for solar inverters or home security systems. Renesas RZ/Five key features and specifications: CPU – Single-core 64-bit RISC-V AX45MP core @ up to 1.0 GHz Internal Memory – 128KB SRAM with ECC Memory I/F – 16-bit DDR4-1600 or DDR3L-1333 memory interfaces with in-line ECC; up to 4GB RAM Storage I/F – 2x SD/eMMC interfaces, SPI flash interface Networking – 2x Gigabit Ethernet MAC USB – 2x USB 2.0 Audio – 4-channel serial sound interface (SSI) Serial – 2x CAN/CAN-FD […]

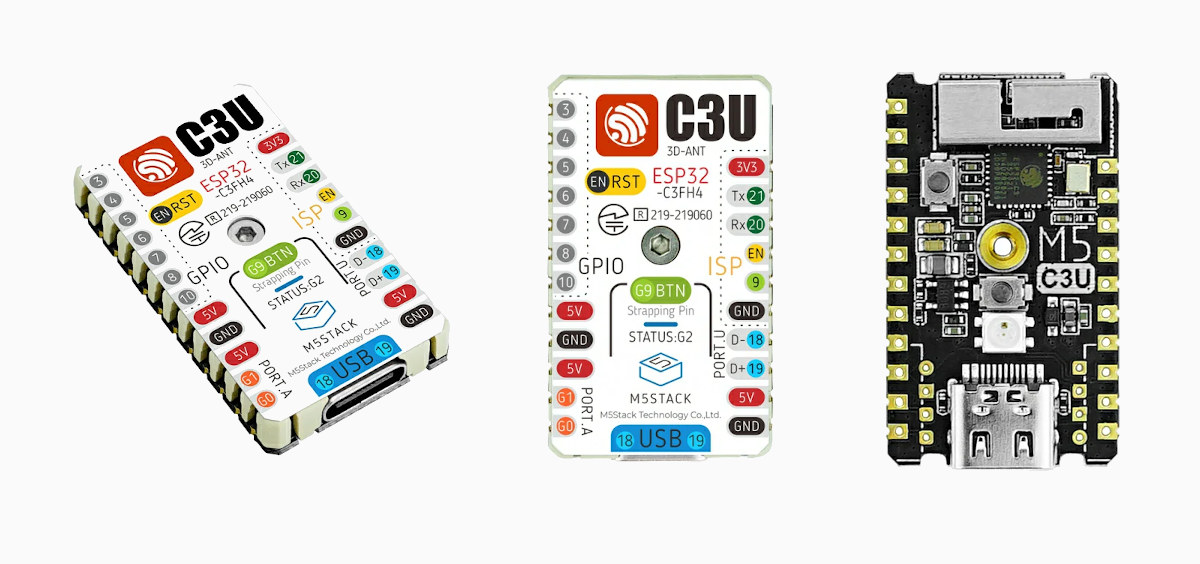

M5Stamp C3U IoT module relies on ESP32-C3’s own USB interface for firmware programming

M5Stamp C3U is an update of the M5Stamp C3 RISC-V IoT module with heat-resistant cover, support for WiFi 4 and Bluetooth 5.0, that does without CH9102 USB to TTL chip, relying instead on the internal USB interface of ESP32-C3 processor to handle serial programming of the firmware, and gaining on extra GPIO pin in the process. While several ESP32 processors come with a built-in USB interface, many boards still use an external USB to TTL chip such as CH340 or CP2102 to handle the serial interface used for debugging and flashing the firmware likely because of limitations when using ESP32-C3’s USB serial/JTAG controller console, but M5Stack probably considered those to be workable, and the small cost-saving beneficial. M5Stamp C3U specifications: WiSoC – ESP32-C3FH4 32-bit single-core RISC-V processor @ up to 160 MHz, with 384KB ROM, 400KB SRAM, 8KB RTC SRAM, 4MB embedded flash, WiFi and Bluetooth Connectivity 2.4 GHz WiFi […]

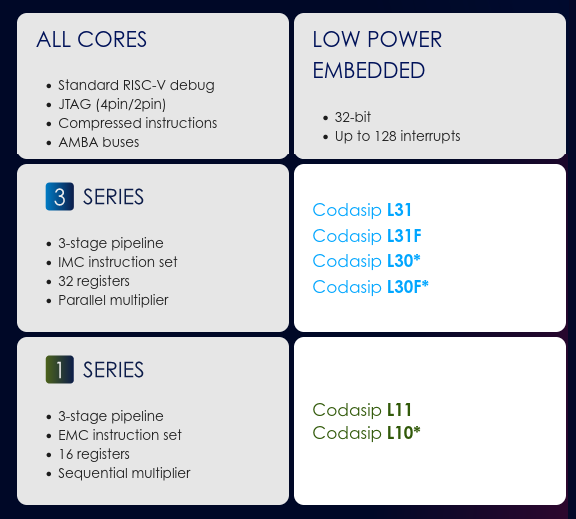

Codasip L31 and L11 RISC-V cores for AI/ML support TFLite Micro, customizations

Codasip has announced the L31 and L11 low-power embedded RISC-V processor cores optimized for customization of AI/ML IoT edge applications with power and size constraints. The company further explains the new L31/L11 RISC-V cores can run Google’s TensorFlow Lite for Microcontrollers (TFLite Micro) and can be optimized for specific applications through Codasip Studio RISC-V design tools. As I understand it, this can be done by the customers themselves thanks to a full architecture license as stated by Codasip CTO, Zdeněk Přikryl: Licensing the CodAL description of a RISC-V core gives Codasip customers a full architecture license enabling both the ISA and microarchitecture to be customized. The new L11/31 cores make it even easier to add features our customers were asking for, such as edge AI, into the smallest, lowest power embedded processor designs. The ability to customize the cores is important for AI and ML applications since the data types, […]

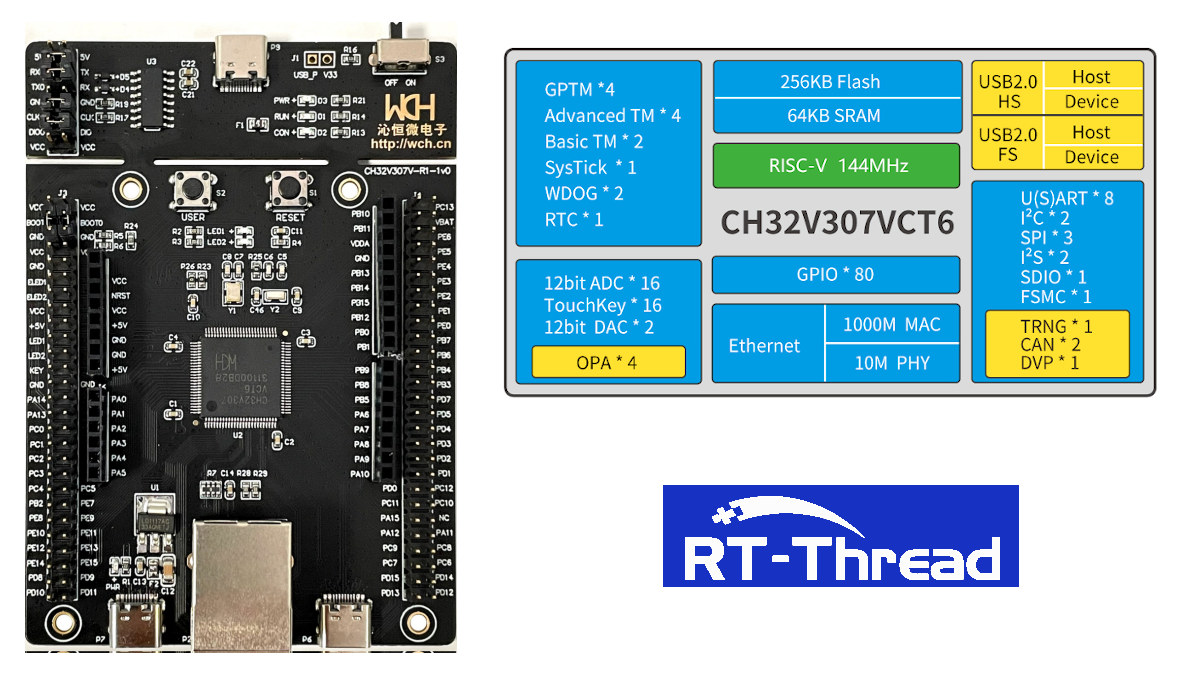

RISC-V design challenge – Get a free board, RISC-V chips, and cash prizes

A little while ago, I wrote about WCH CH32V307 32-bit RISC-V MCU that was found in a board with eight UART ports that could be controlled over Ethernet or USB, and the company has released some source code to use the board while inviting the community to submit pull requests to the project. But now WCH, RT-Thread, LCSC, and EasyEDA have joined hands to launch the RISC-V design challenge where the companies will provide a free board or two RISC-V chips to selected participants, as well as cash prizes with up to $1000 offered to the best projects. The companies have prepared 300 boards and 200 chips for this contest. All you need to do to get a chance to get either one CH32V307V-EVT-R1 development board or two CH32V307 RISC-V microcontrollers is to enter your contact and project details in this Google form by April 30, 2022. The conditions are […]

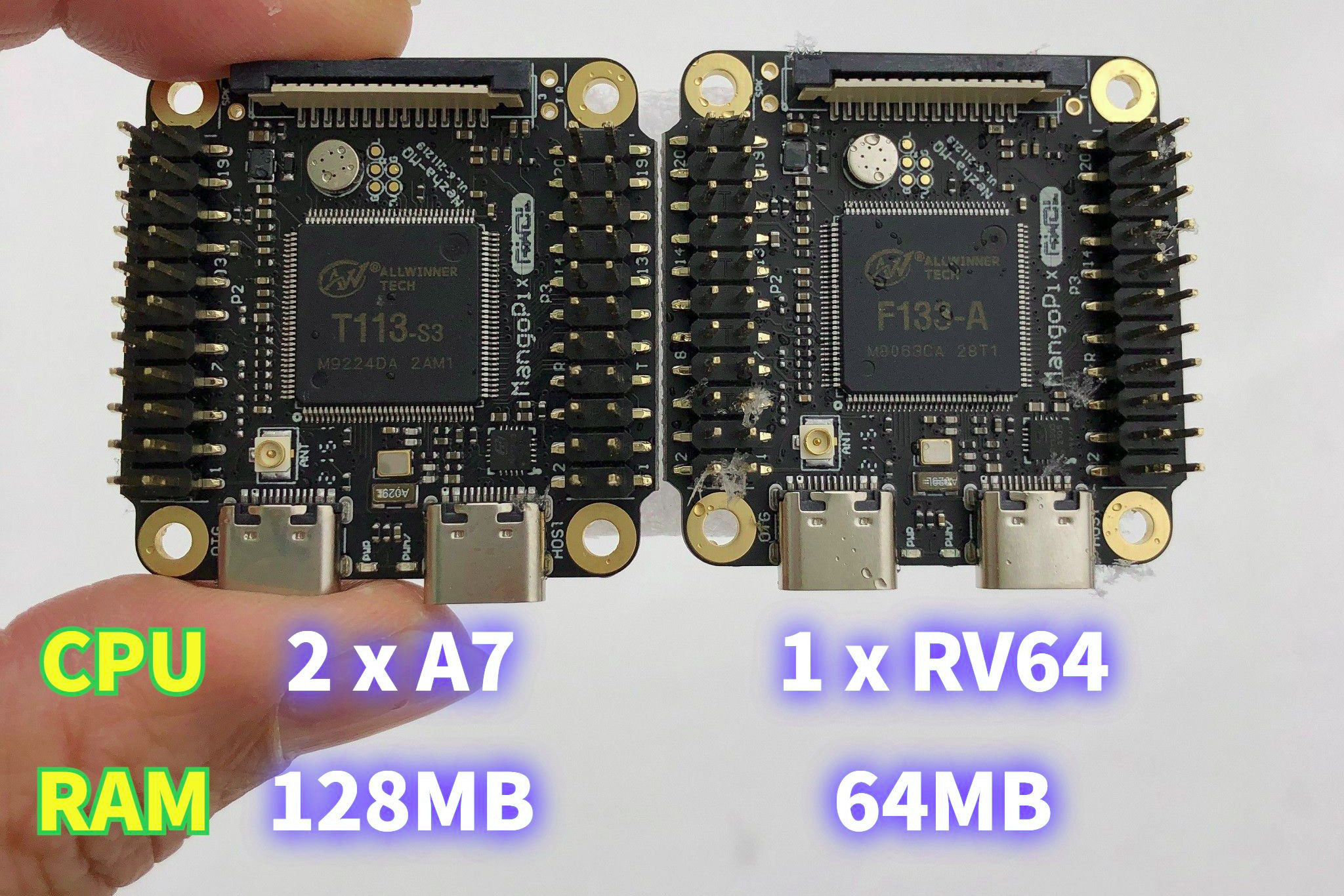

RISC-V or Arm? This tiny 4x4cm Linux board with WiFi offers both options

Last fall, we wrote about Allwinner D1s/F133-A RISC-V processor and the upcoming MangoPi MQ1, a tiny 4x4cm board based on the processor. The board is not for sale, but we have more details, and the company is also working on an Arm version equipped with Allwinner T113-S3 dual-core Cortex-A7 processor that is pin-to-pin compatible with F133-A SoC. The Allwinner F133-A board will finally be called MangoPi Nezha-MQ, or MangoPi MQ for shorts, and come with 64MB on-chip RAM while the Allwinner T113-S3 board, with 128MB on-chip RAM, will be named MangoPi MQ-Dual. Both are fitted with a Realtek RTL8189-based Wi-Fi module, offer display and camera interfaces, two USB-C interfaces, and headers for GPIOs. MangoPi MQ RISC-V or Arm Linux board MangoPi MQ/MQ-Dual specifications: SoC (one or the other) MangoPi MQ – Allwinner D1s/F133-A 64-bit RISC-V processor @ 1 GHz with 64 MB DDR2 MangoPi MQ-Dual – Allwinner T113-S3 32-bit dual-core […]

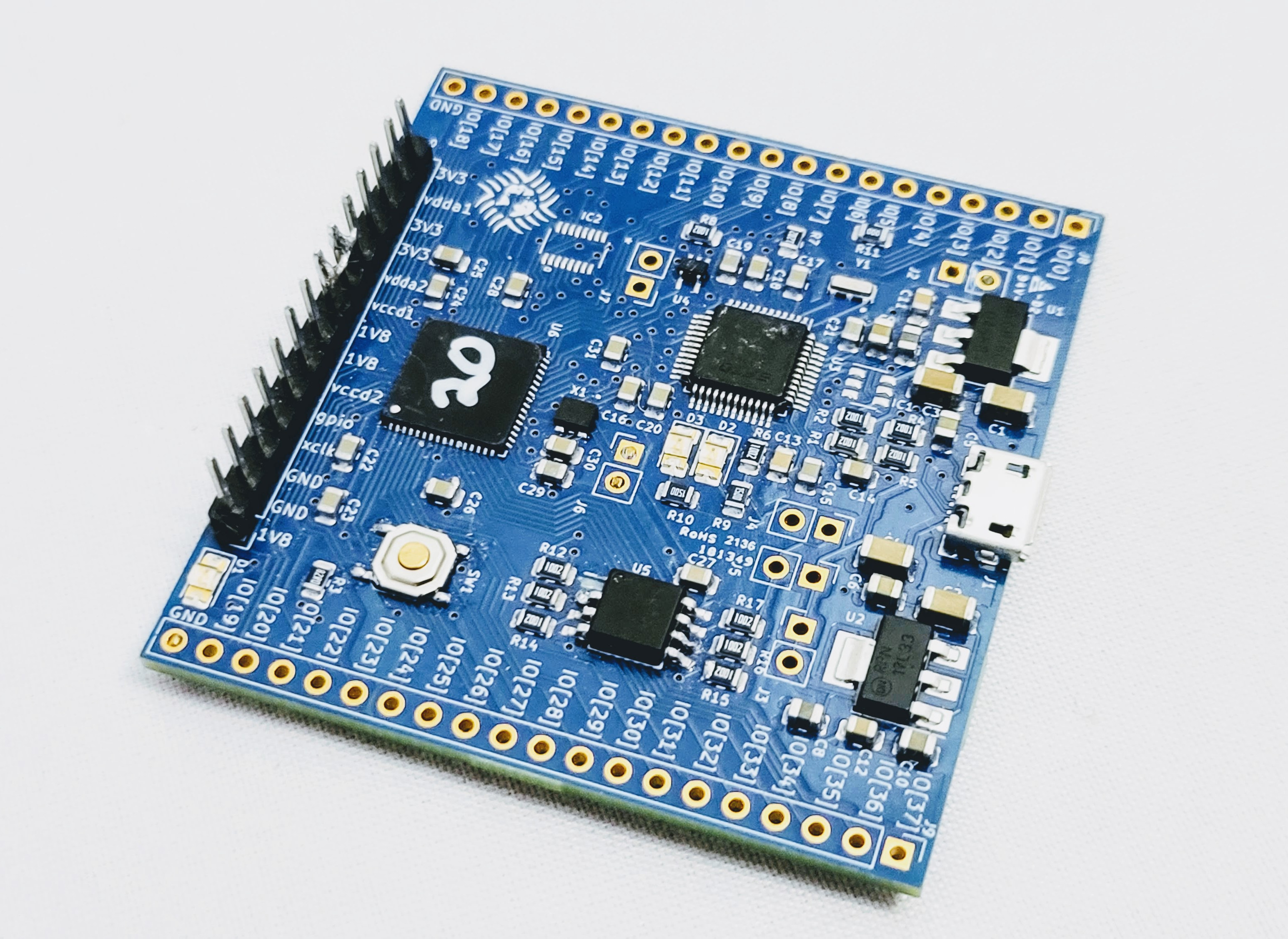

CLEAR is an open-source FPGA ASIC provided by Efabless’ chipIgnite

Open-source SoC designs are available to run on FPGA hardware, but few make it to silicon due to the costs involved. That’s why a couple of years ago the Google SkyWater PDK (process design kit) was released together with an offer to manufacture up to 100 pieces for free to selected designs in collaboration with Efabless. Efabless chipIgnite is an evolution of that offer with $9,750 being enough funds to manufacture 100 QFN or 300 WCSP parts, or alternatively 1,000 parts for $20 each ($20,000). Based on the company’s Caravel template SoC and the openFPGA generator framework, CLEAR open-source FPGA ASIC design is meant to promote and demonstrate the chipIgnite “paid IC creation” solution. You can participate by joining a group buying campaign on GroupGets to get a development board based on CLEAR for $74.99 plus shipping. CLEAR open-source FPGA ASIC features: FPGA – Small 8×8 (64) CLB eFPGA CPU […]

Intel to invest $1 billion in foundry innovation, becomes RISC-V International member

Intel has just announced a $1 billion fund to support companies bringing innovations and new technologies to the foundry ecosystem. The company says the fund will prioritize investments in “capabilities that accelerate foundry customers’ time to market – spanning intellectual property (IP), software tools, innovative chip architectures, and advanced packaging technologies.” What’s interesting is that it does not only cover x86 architecture but also Arm and RISC-V, with a focus on the latter, as Intel has just become a Premier member of RISC-V International, and partnered with several companies offering RISC-V solutions including Andes Technology, Esperanto Technologies, SiFive, and Ventana Micro Systems. Intel’s Open Chiplet Platform Part of the investment will go to the Open Chiplet Platform offering a modular approach to chip design through chiplets with each block/chiplet customized for a particular function. This will allow designers to select the best IP and process technologies for a particular SoC. […]