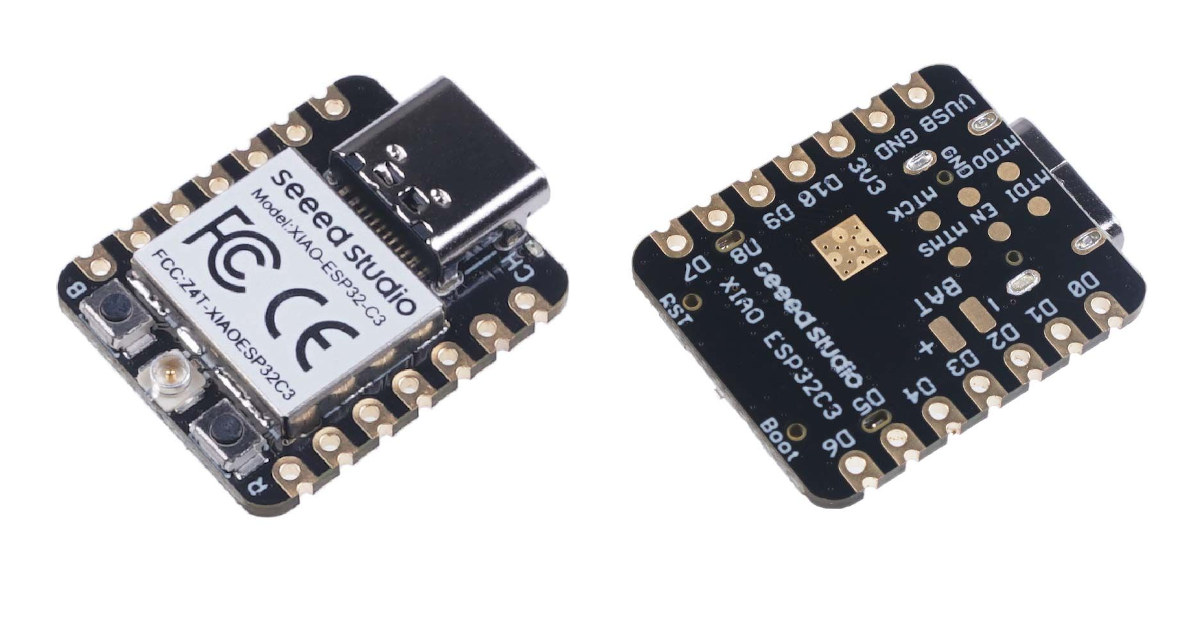

Seeed Studio’s XIAO family of tiny MCU boards expands with the XIAO ESP32C3 board equipped with ESP32-C3 WiFi and Bluetooth LE (BLE) microcontroller, support for LiPo batteries, and following the same 21 x 17.5mm form factor. If I’m counting right, this is the fifth member following the original XIAO based on Microchip SAMD21G18 Cortex-M0+ MCU, XIAO RP2040, and the nRF52840-based XIAO BLE and XIAO BLE Sense boards which I tested with Edge Impulse. XIAO ESP32C3 specifications: Wireless MCU – Espressif Systems ESP32-C3 single-core RISC-V microcontroller @ 160 MHz with 400KB SRAM, 384KB ROM, 4MB flash Wi-Fi 4 & Bluetooth LE 5.0 connectivity Antenna – External u.FL antenna USB – USB Type-C port for power and programming Expansion I/Os 2x 7-pin headers with 1x UART, 1x I2C, 1x SPI, 11x GPIO (PWM), 4x ADC, I2S 3.3V I/O voltage (not 5V tolerant) Debugging – JTAG pads Misc – Reset button, Boot button, […]

ROMA Linux laptop to feature quad-core RISC-V SoC, support Web3, NFT, cryptocurrencies, etc…

ROMA is an upcoming Linux laptop equipped with an unnamed quad-core RISC-V processor with GPU and NPU, up to 16GB RAM, 256GB storage, primarily aimed at software developers, and with Web3 technology integration. The ROMA laptop will be born out of the collaboration between DeepComputing working on engineering and Xcalibyte taking care of system tuning, plus PW (assembly), ECP (security), XC (crypto), Rexeen (voice), and the LatticeX Foundation (PoS blockchain, NFT). ROMA laptop preliminary specifications: SoC – Quad-core RISC-V CPU with GPU for graphics, NPU for AI (12nm chip for the Pro model, 28nm chip for the Standard model) System Memory – 16GB LPDDR4/LPDDR4X RAM Storage – 256GB eMMC flash Security – Arm SC300 security enclave processor Display, keyboard, touchpad I agree that’s a bit light on details. We’re told the laptop will support most Linux operating systems and the company will offer free SoC and SoM upgrades, as well […]

A RISC-V laptop or mini PC with Rockchip RK3588-class performance may be coming soon

Mark Himelstein, Chief Technology Officer, RISC-V International, and Dr. Philipp Tomsich, Chief Technologist & Founder, VRULL GmbH hinted that we may see a RISC-V laptop in 2022 in a presentation entitled “From Technology to Product – Maturing the RISC-V Ecosystem” with one of the slides showing what could be a RISC-V laptop prototype and The Register suspected it might come from the Institute of Software at the Chinese Academy of Sciences (ISCAS) since it was planning to build 2,000 RISC-V laptops by the end of 2022. But there’s at least one more potential RISC-V laptop project coming our way with StarFive asking users to fill out a survey about a laptop, mini PC, or development board/SBC based on a RISC-V SoC with performance comparable to Rockchip RK3588 or MediaTek MT8192 octa-core Cortex-A76/Cortex-A55 processors. The hardware and software specifications of the device will depend on the answers to the survey. First, it’s […]

Imagination unveils IMG RTXM-2200 32-bit RISC-V real-time “Catapult” CPU

Imagination IMG RTXM-2200 32-bit RISC-V real-time CPU core is the first member of the company’s Catapult family comprised of four distinct RISC-V families for dynamic microcontrollers, real-time embedded CPUs, high-performance application CPUs, and functionally safe automotive CPUs. The company says it’s a highly scalable real-time, deterministic, 32-bit embedded CPU, that is feature-rich and flexible in design for mainstream devices, but, excuse the pun, leaves most of the details to your imagination… The new core will mostly be used as a helper core (aka co-processor) in more complex SoCs for 5G modems, cellular base stations, networking solutions for data transfer, packet management, and storage controllers, but may also find its way into smart meters. In all fairness, we do have some limited technical details with L1 cache sizes up to 128KB, I/D TCM sizes up to 128KB, and PMA regions. The real-time core will also include optional features such as single-point […]

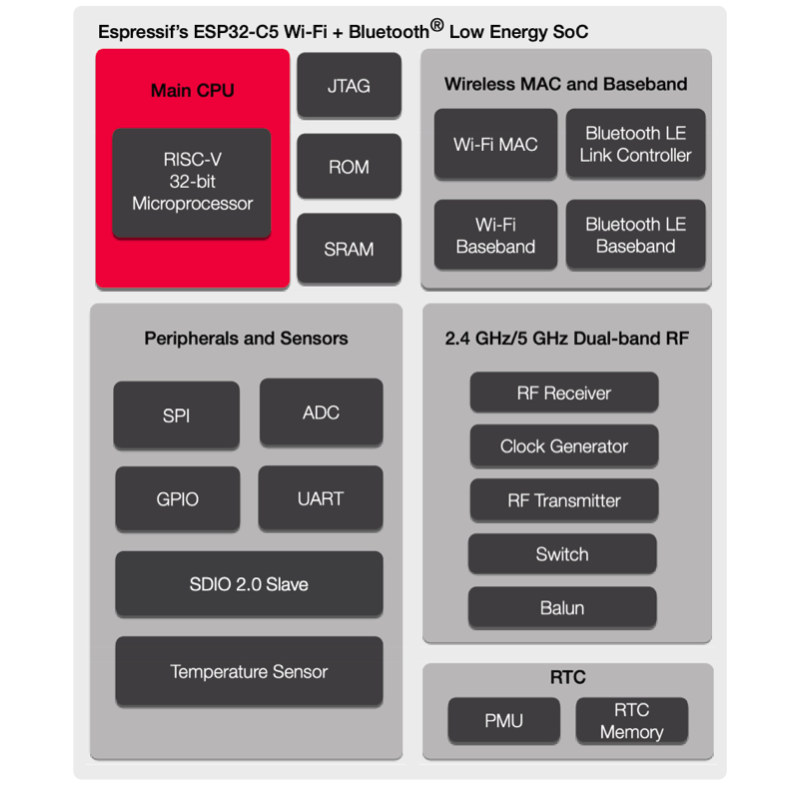

ESP32-C5 RISC-V IoT MCU supports dual-band WiFi 6, Bluetooth 5.0 LE

Espressif Systems ESP32-C5 is an upcoming wireless RISC-V microcontroller for IoT applications that supports dual-band (2.4 & 5.0 GHz) WiFi 6 connectivity as well as Bluetooth 5.0 LE. It is the first dual-band processor from Espressif, as while the Shanghai-based company previously announced the ESP32-C6 WiFi 6 and Bluetooth 5 LE RISC-V SoC last year, it only supports 2.4 GHz frequency. Note it’s not the first dual-band WiFi 6 IoT chip on the market as NXP introduced the IW612 Wi-Fi 6, Bluetooth 5.2, 802.15.4 tri-radio solution last January, but ESP32-C5 should target different use cases. ESP32-C5 preliminary specifications: CPU – Single-core 32-bit RISC-V processor @ up to 240 MHz Memory – 400KB SRAM on-chip Storage – 384KB of ROM on-chip, support for external flash Connectivity Dual-band 802.11ax WiFi 6 in the 2.4GHz and 5 GHz bands, with 802.11b/g/n WiFi 4 standard support for backward compatibility 20MHz bandwidth for the 802.11ax […]

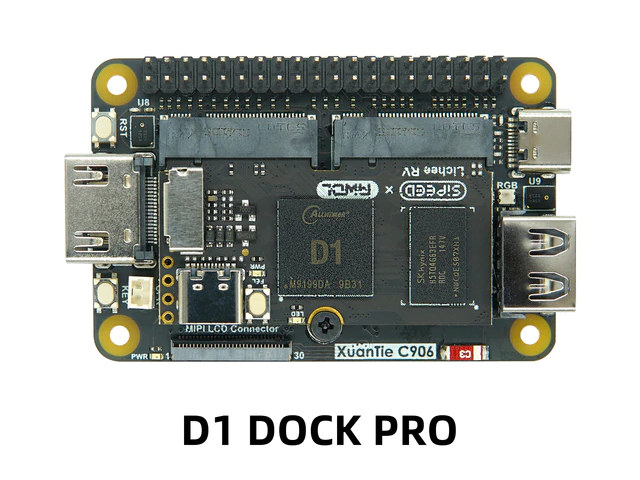

Sipeed Lichee RV Dock Pro RISC-V SBC adds MIPI/RGB LCD connector, dual MIC, and BL702 JTAG+UART debugger

Sipeed has launched the Lichee RV Dock Pro kit for the company’s Lichee RV Allwinner D1 RISC-V module that builds on the earlier Lichee RV Dock carrier board and adds a MIPI/RGB LCD connector, two built-in microphones, as well as an on-board JTAG+UART debugger based on Bouffalo Lab BL702 microcontroller. Lichee RV Dock Pro specifications (preliminary) which changes in bold or strikethrough: Supported system-on-module (SoM) – Lichee RV module with Allwinner D1 RISC-V processor @ 1 GHz, 512MB DDR3, MicroSD card slot, and USB Type-C OTG port Storage – Optional SPI flash Display interfaces HDMI port up to 4Kp30 MIPI LCD/RGB interface for up to 720p30 display Audio – 3W power amplifier, 2x analog microphone, support for 6-mic array via expansion Connectivity – WiFi 4 and Bluetooth 4.2 via Realtek RTL8723 wireless module with ceramic antenna, IPEX antenna connector USB – 1x USB Type-A port adding to the USB-C OTG […]

Think Silicon NEOX RISC-V GPU offers 3D graphics or AI acceleration

Think Silicon NEOX GPU family with models optimized for graphics (NEOX|G) or artificial intelligence (NEOX|A) is based on the RISC-V RV64C ISA instruction set with adaptive NoC, and offers up to 64 cores delivering up to 409.6 GFLOPS at 800MHz with support for FP16, FP32 and optionally FP64 and SIMD instructions. The NEOX GPUs can be integrated into microcontrollers, crossover processors, and even more powerful application processors, and target AI, IoT/Edge, and media processing in consumer and industrial devices. Each shader of the GPU is a programmable 64-bit RISC-V (RV64GC) core running a real-time operating system (RTOS) and the GPU is supported by lightweight graphics and machine learning frameworks. The multi-threaded GPU system can be customized for graphics, machine learning, vision/video processing, and general-purpose compute (GPGPU) workloads. The solution is meant to be integrated into 32-bit SoCs designed for smartwatches, augmented reality (AR) eyewear, video surveillance, and smart display terminals […]

Lichee RV-86 RISC-V Linux 4-inch panel targets home automation, HMI applications

When Sipeed first introduced the Lichee RV module with Allwinner D1 RISC-V SoC last November, they also teased the Lichee RV-86, an “86 Box” with a 4-inch 480×480 touchscreen display, an XR829 WiFi and Bluetooth module, Ethernet (via USB), two microphones, a GPIO header, and support for WAFT (WebAssembly Framework for Things). I’ve just noticed the Lichee RV-86 has been for sale for several months, so it may be interesting to have a closer look, and now there’s also an option to get a 720×720 touchscreen display. Lichee RV-86 specifications: SoM – Sipeed Lichee RV Nezha compute module with Allwinner D1 RISC-V processor @ 1 GHz, 512MB or 1GB DDR3, microSD card slot, and USB Type-C OTG port Display 4-inch 480×480 IPS capacitive touch screen OR 4-inch 720×720 IPS capacitive touch screen It is also possible to connect an 8-inch 1280*800 IPS capacitive touch screen to the board Audio – […]