CSEM and USJC together have developed an ultra-low-power RISC-V chip for electronic gadgets such as wearables. The semiconductor companies, from Switzerland and Japan respectively, have been in the market for a while, developing technologies for low-power chips. Their latest collaboration uses Adaptive Body Biasing (ABB) and Deeply Depleted Channel (DDC) to build an ultra-low-power RISC-V chip with all the required and necessary components. Originating from the labs of CSEM, the Adaptive Body Biasing dwells into the operating efficiency of all the modes of ON, Standby, and OFF. There has been the problem of power leakage in Standby and OFF operating modes, but the Adaptive Body Biasing technology helps design to minimize power leakage when the processor is not operating while keeping the best performance in ON mode. For most of the designs, the processor is in Standby mode waiting for the incoming data or the next event to be offered. […]

The RISC-V Platform Specification aims to ensure RISC-V hardware and software compatibility

The RISC-V platform specification aims to define a set of rules to make sure operating systems like Linux or the Zephyr Project can boot properly on all RISC-V hardware compliant with the specs. If you’ve ever worked with the Arm Linux kernel over ten years ago, you may remember board files, which were replaced by device tree bindings, and eventually, Arm defined several standards culminating with Arm SystemReady certifications allowing compliant Arm platforms to boot off-the-shelf OS images like in the x86 world. While we are probably a long way from a “RISC-V SystemReady” platform certification program, the RISC-V platform specification is currently being worked on to define requirements for two types of platforms with optional extensions: OS-A Platform: This specifies a rich-OS platform for Linux/FreeBSD/Windows…flavors that run on enterprise and embedded class application processors. Current extension: Server Extension M Platform – This specifies an RTOS platform for bare-metal applications […]

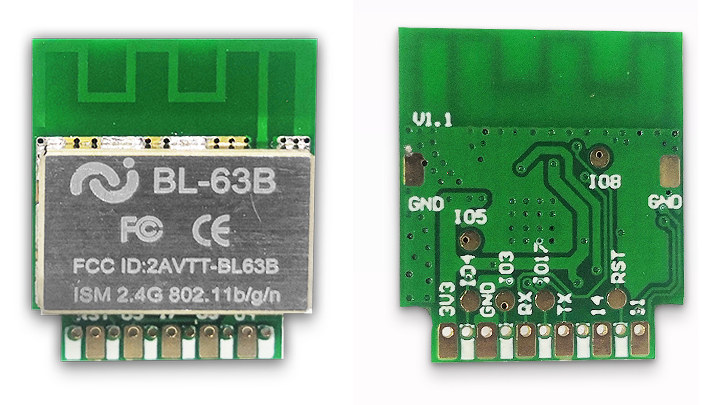

BL-63B – A smaller BL602 IoT module that sells for $1.5

Bouffalo Labs BL602 is a low-cost, low-power RISC-V microcontroller that offers 2.4 GHz WiFi and Bluetooth 5.0 LE connectivity for IoT projects for about the price of ESP8266. We first discovered it last year, together with a development board. Pine64 created its own PineCone board fitted with the $2 PineNut module, and some reverse-engineering work has started on BL602 SDK. But there’s now another smaller BL602 module with “Machine Intelligence” (that’s the company name) BL-63B that sells for $1.5 on Taobao in China, as well as on LCSC Electronics albeit you’d need to purchase 1000 pieces to get that price, and single-unit pricing is currently $2.5. BL-63B WiFI & BLE module specifications: SoC – Bouffalo Labs BL602 32-bit RISC-V processor @ up to 192 Mhz with 276KB RAM, 128KB ROM, 1Kbit eFuse, WiFi and BLE Storage – 2MB flash Wireless 2.4GHz 802.11b/g/n WiFI 4 1×1 SISO up to 65 Mbps […]

XGO Mini Pro robot dog features Kendryte K210 AI processor (Crowdfunding)

[Update: Initially published on July 30th, XGO Mini Pro robot dog is now up on Kickstarter. While it was listed on the Kendryte K510 product page, it is only offered with the earlier Kendryte K210 in the crowdfunding campaign] Kendryte K510 RISC-V AI processor is the successor of Kendryte K210 with much more AI processing power (2.5/3 TOPS) that makes it suitable for robotics projects demanding much lower latency and quasi-real-time inference. One of the first products to be compatible with both Kendryte K510/K210 capabilities is Luwu Intelligence Technology’s XGO Mini Pro, a four-legged robot that looks like a dog with a tiny head providing the “smarts” for the system including face detection, image recognition, object tracking, voice recognition, and so on. We first found the description of the robot on Canaan’s website is rather short with an explanation that when equipped with is equipped with a 9-axis IMU and […]

BeagleV Starlight SBC won’t be mass manufactured, redesigned BeagleV RISC-V SBC expected in Q1 2022

There was lots of excitement when BeagleV Starlight single board computer was announced in January of this year. With a price tag of $119 and up, it promises to be an affordable RISC-V SBC with StarFive JH7100 dual-core SiFive U74 Vision SoC with AI accelerator, H.265/H.264 hardware video decoding, up to 8GB RAM, HDMI output, Gigabit Ethernet, and so on. Several beta testers even received BeagleV Startlight prototypes, providing instructions for buildroot, boot Linux, or even a video review with Fedora. The first version lacked a GPU, and the initial schedule planned for a new revision with an Imagination GPU to be manufactured in September. But there have been some changes, as BeagleV Starlight SBC will not go into mass production, but not all is lost, as the Foundation and Seeed Studio are working on a new BeagleV community board slated to be released in Q1 2022. Drew Fustini made […]

Upcoming events about RISC-V, RT-Thread IoT OS, and Embedded Linux

Three events about open/open-source technologies have been recently announced with namely the RT-Thread IoT OS Tech Conference, the jointly organized Open Source Summit and Embedded Linux Conference 2021, and the 2021 RISC-V Summit. Let’s have a quick look at what each will have to offer with the list in chronological order. RT-Thread IoT OS Global Tech Conference 2021 The first-ever RT-Thread IoT OS Global Tech Conference will take place online on September 16–17,2021, be free to attend, and feature talks about embedded technologies, new projects showcase, community contributors track mostly related to RT-Thread open-source real-time operating system, but also IoT development in general. The agenda has not been published just yet, as the call for speakers is still open until August 8th. People just wanting to attend can register through a Google Docs form. Somehow there’s no landing page on the main page, and instead, they’ve decided to publish information […]

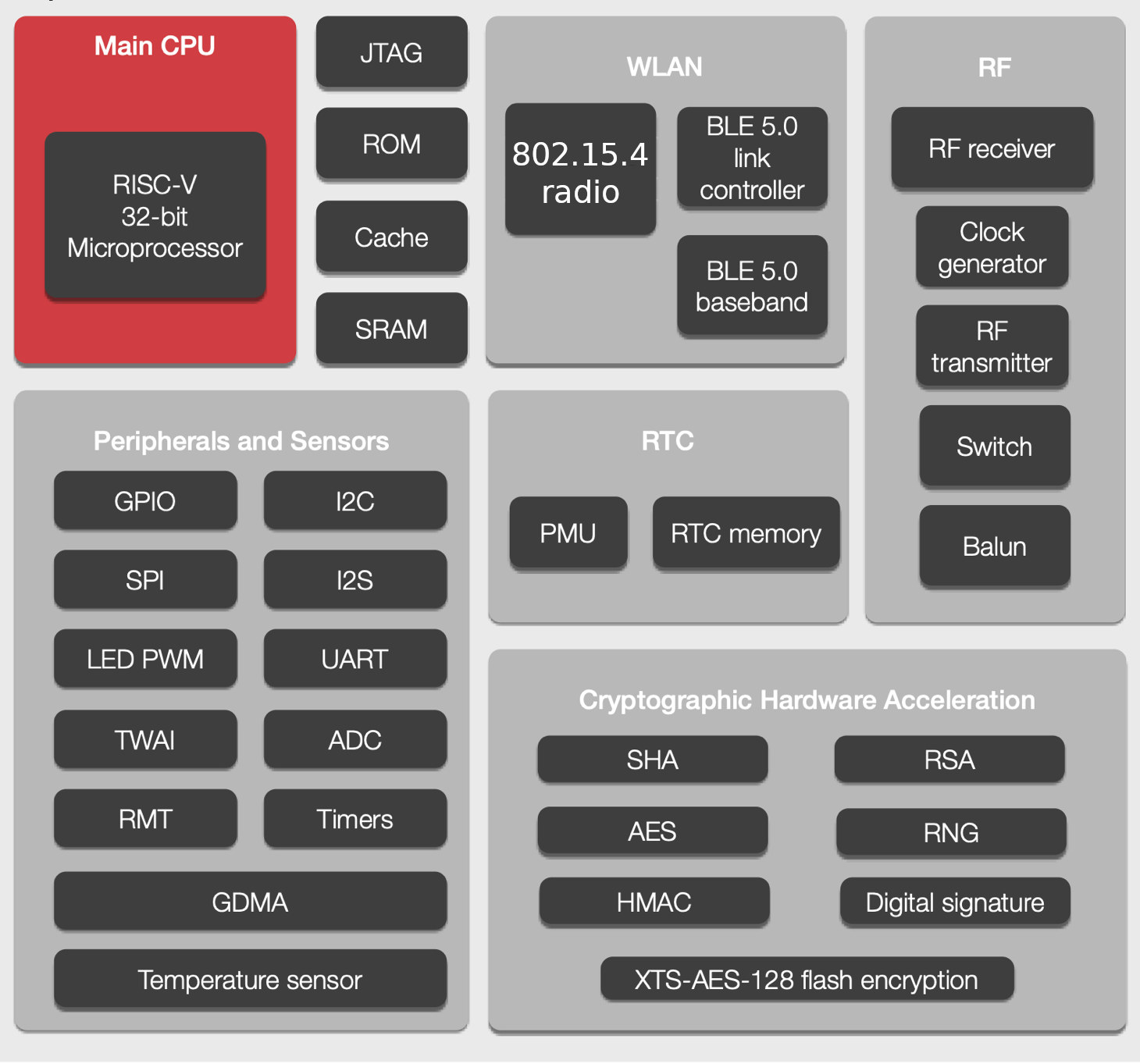

ESP32-H2 Bluetooth LE & 802.15.4 RISC-V SoC shows up in ESP-IDF source code

Espressif Systems is working on yet another RISC-V chip with ESP32-H2 SoC offering Bluetooth LE and 802.15.4 connectivity showing up in the ESP-IDF framework source code. A code comparison shows ESP32-H2 is very similar to ESP32-C3 with a single RISC-V core, albeit clocked at up to 96 MHz, and the first Espressif SoC without WiFi, as the WiFi radio is replaced with an 802.15.4 radio for Thread, Zigbee, etc… that can be used for the development of Home Automation, Smart Lighting, and wireless sensor network applications. While looking at the source code differences between ESP32-C3 and ESP32-H2, the really only major differences were the 802.15.4 radio and lower maximum frequency, and at the current time, it looks like most of the rest is unchanged, so it’s possible they kept the same amount of RAM (400KB), storage, and most of the same peripherals, but it could just well be the code […]

WARP-V: A RISC-V CPU Core Generator Supporting MIPS ISA

If you have been working on open standard RISC-V ISA CPU cores, there is a high chance that you have come across WARP-V. For newbies, WARP-V is a RISC-V CPU core generator written in TL-Verilog (Transaction-Level Verilog) that supports not only RISC-V but also MIPS ISA. WARP-V has been in discussion for a while due to its unparalleled architectural scalability in a small amount of code. The famous proverb “Necessity is the mother of invention” applies to the invention of TL-Verilog and with that this WARP-V CPU core generator. For decades, hundreds of engineers have been working on designing a single CPU core that was more complex in the race to achieve higher single-core performance. But with recent developments in the semiconductor industry, developer and engineer Steve Hoover, with decades of experience in designing CPU cores, has come up with the idea of developing a WARP-V core in just 1.5 […]