Linux 6.4 has just been released by Linus Torvalds on the Linux Kernel Mailing List (LKML): Hmm. Final week of 6.4 is done, and we’ve mainly got some netfilter fixes, some mm reverts, and a few tracing updates. There’s random small changes elsewhere: the usual architecture noise, a number of selftest updates, some filesystem fixes (btrfs, ksmb), etc. Most of the stuff in my mailbox the last week has been about upcoming things for 6.5, and I already have 15 pull requests pending. I appreciate all you proactive people. But that’s for tomorrow. Today we’re all busy build-testing the newest kernel release, and checking that it’s all good. Right? Released around two months ago, Linux 6.3 brought us AMD’s “automatic IBRS” Spectre defense mechanism, additional progress on the Rust front with User-mode Linux support (on x86-64 systems only), the NFS filesystem (both the client and server sides) gained support for […]

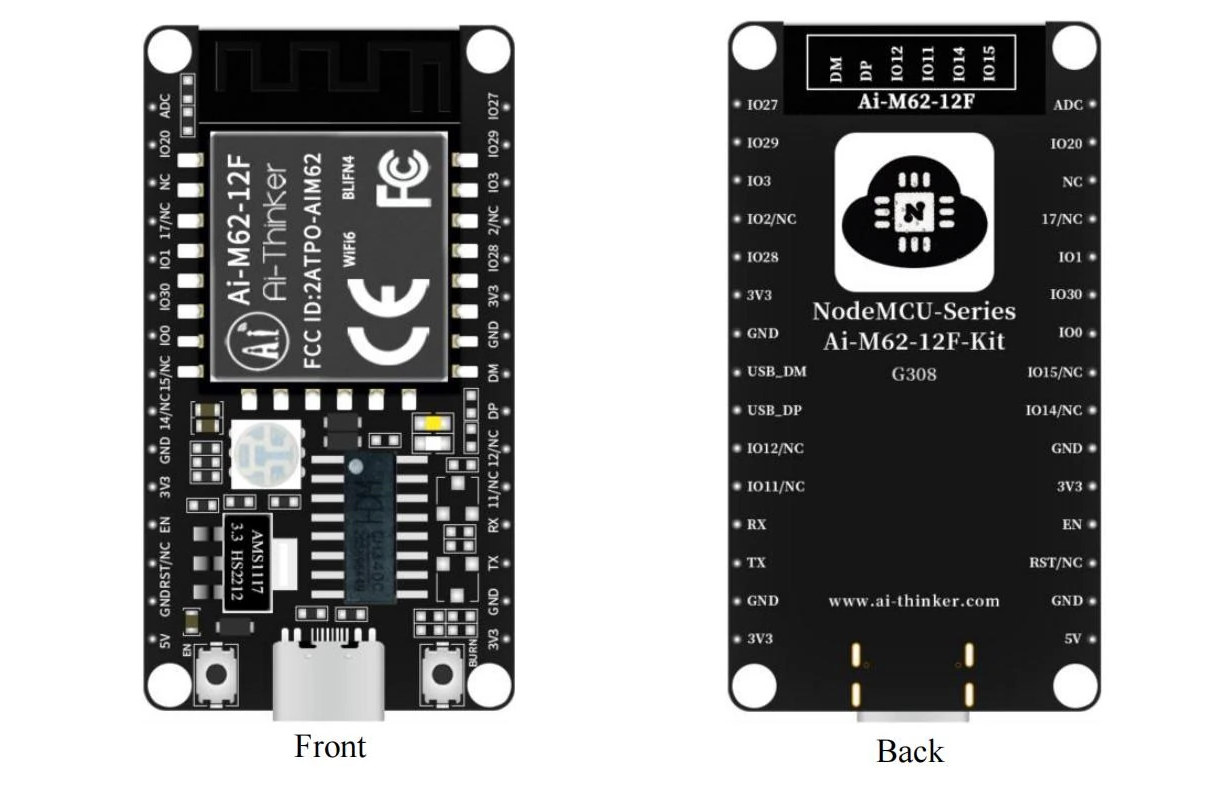

$5 Ai-M62-12F-Kit RISC-V development board features BL616 WiFi 6, BLE 5.2, and Zigbee MCU, plenty of I/Os

Ai Thinker Ai-M62-12F-Kit is a development board based on Bouffalo Lab BL616 RISC-V microcontroller with 2.4 GHz WiFi 6, Bluetooth 5.2 LE, and an 802.15.4 radio (Zigbee/Thread), plus thirty I/O pin for expansion. We had already covered the tiny Sipeed M0S module based on BL616 MCU earlier this year along with its M0S dock board that exposed eight GPIO pins via a 12-pin header, and the “NodeMCU” Ai-M62-12F basically offers the same features but with many more I/Os thanks to two 15-pin headers, as well as an RGB LED and two user-programmable LEDs. Ai-M62-12F-Kit specifications: MCU – Bouffalo Lab BL616 32-bit RISC-V (RV32IMAFCP) microcontroller @ up to 320 MHz (384 MHz overclocked) with 480KB SRAM, 4MB flash, 2.4 GHz WiFi 6, Bluetooth 5.2 dual mode, and 802.15.4 radio (Zigbee) Antenna – PCB antenna USB – 1x USB Type-C port for power and programming I/Os – 2x 15-pin headers with Storage […]

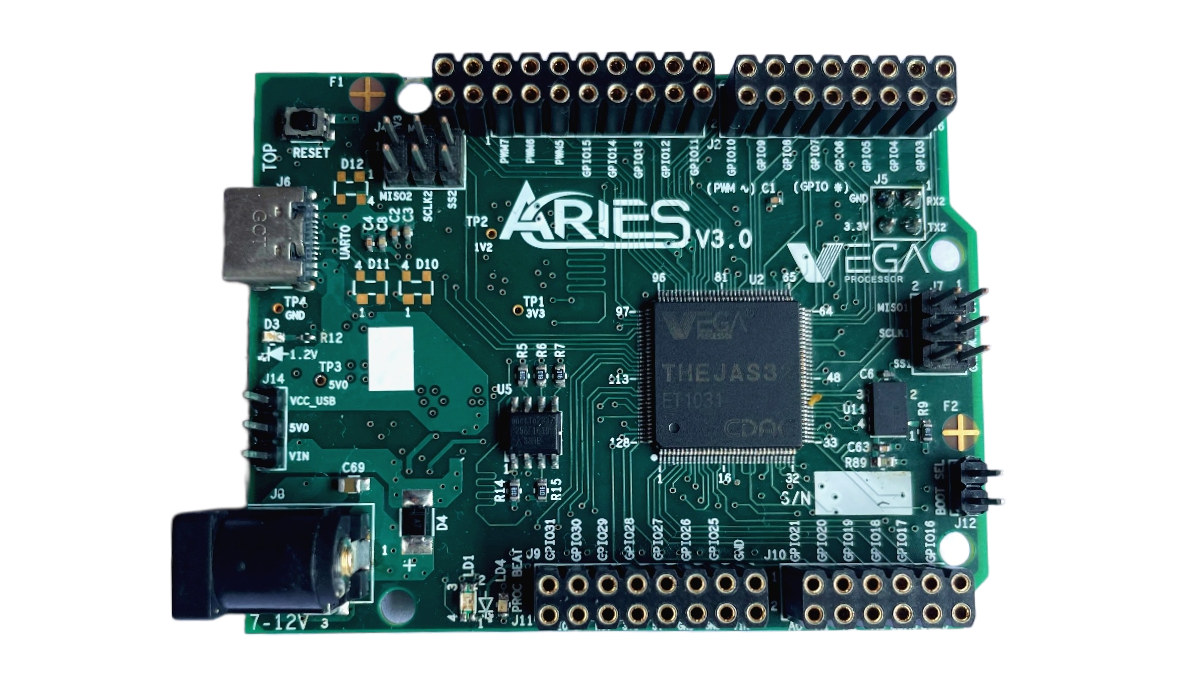

ARIES v3.0 development board features India-made VEGA RISC-V processor

ARIES v3.0 is an Arduino-inspired development board with the made-in-India 100 MHz THEAJS32 ASIC with the VEGA ET1031 RISC-V microprocessor, 256KB of internal SRAM, and various I/Os. Not to be confused by the recent FIVEberry RISC-V SBC made by ARIES Embedded… We first wrote about VEGA RISC-V processors designed in India in February 2022, and at the time, the government worked on five RISC-V processor designs ranging from a single-core 32-bit RISC-V microcontroller-class processor to a Linux-capable quad-core 64-bit out-of-order processor, with the entry-level THEJAS32 and THEJAS64 SoCs based on respectively VEGA ET1031 and VEGA AS1061 cores running on an ARTY A7 FPGA board. But good progress has been made since then, and they have tapped out the THEJAS32 processor and manufactured some development boards such as the ARIES v3.0. ARIES v3.0 development board specifications: MCU – THEJAS32 VEGA ET1031 32-bit 3-stage in-order RISC-V ( RV32IM) microcontroller @ 100 MHz […]

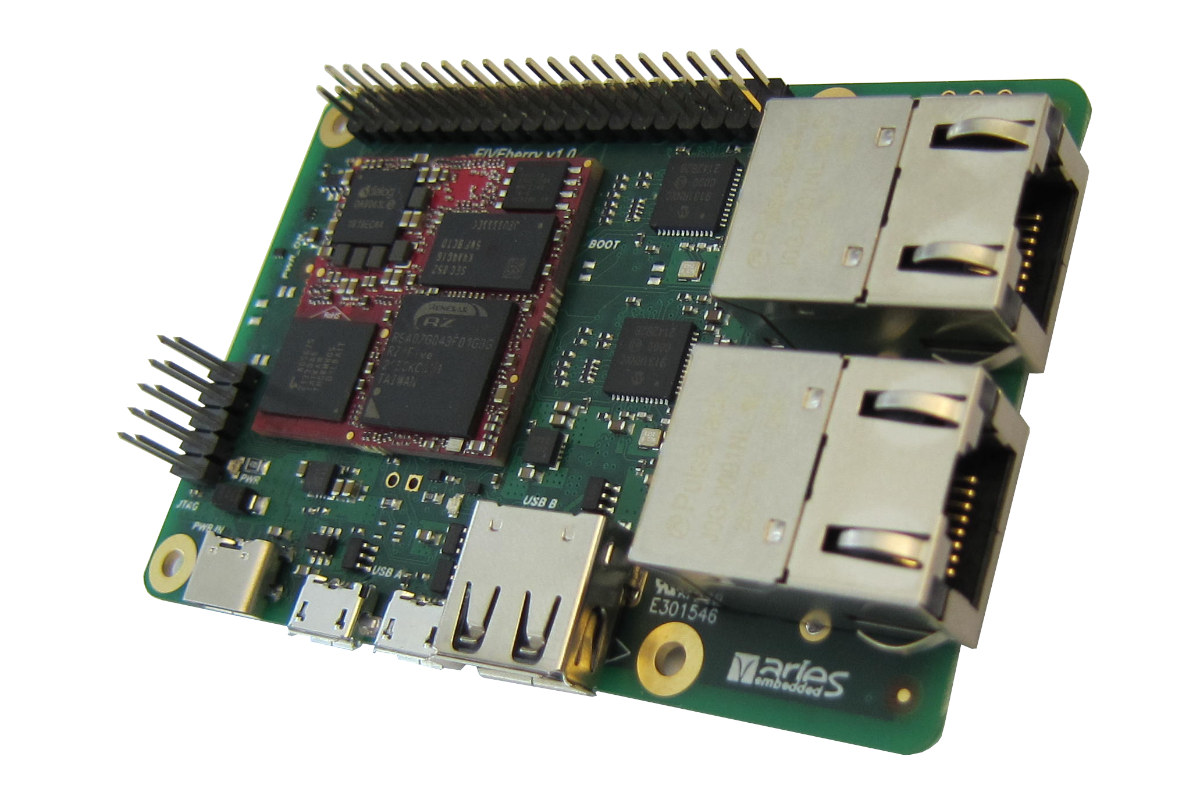

ARIES FIVEberry – A Community RISC-V SBC powered by Renesas RZ/Five processor

ARIES Embedded has unveiled the FIVEberry 64-bit RISC-V community board for fast prototyping fitted with an OSM-compatible MSRZFive system-in-package (SiP) powered by a 1GHz Renesas RZ/Five microprocessor. The board is equipped with a module with 512 DDR4, a 128MBit SPI NOR flash, a microSD card on the bottom of the board, two Gigabit Ethernet ports, two USB 2.0 ports, a micro USB port for serial console, and a JTAG header for further debugging, as well as a 40-pin GPIO header for expansion. FIVEberry specifications: SoM – ARIES Embedded MSRZFive-A0A system-on-module SoC – Renesas RZ/Five R9A07G043F01GBG single-core RISC-V AX45MP processor @ to 1.0 GHz System Memory – 512MB DDR4 RAM Storage – 128Mbit SPI NOR flash 332 contacts as per OSM Size-S specifications Storage – MicroSD card slot Networking – 2x Gigabit Ethernet ports USB – 1x USB 2.0 host port, 1x micro USB 2.0 OTG port Expansion – 40-pin GPIO […]

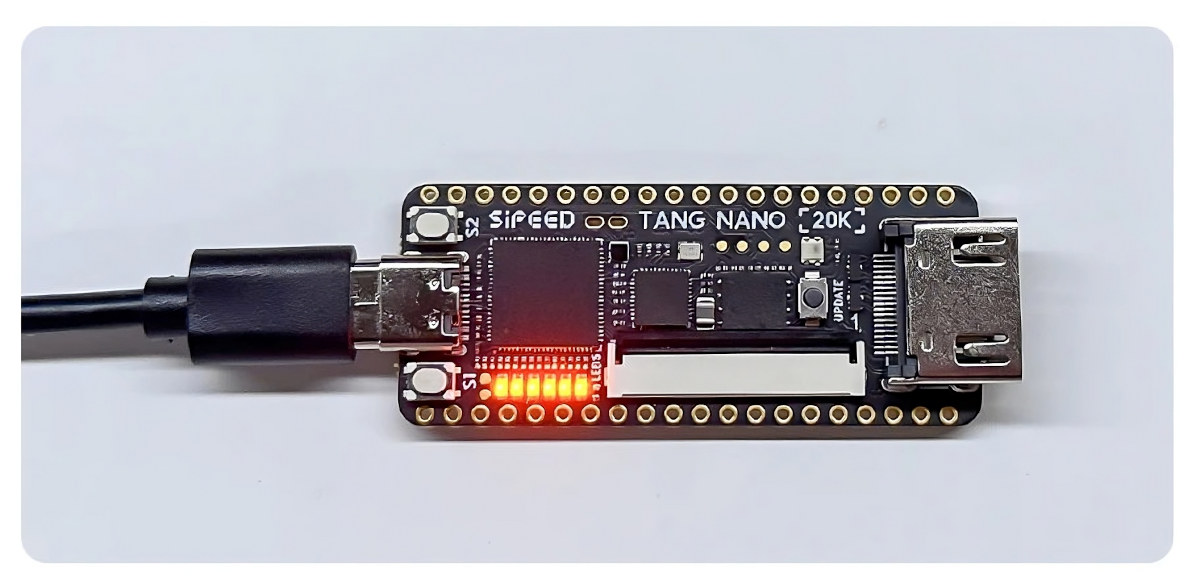

$25 Sipeed Tang Nano 20K FPGA board can simulate a RISC-V core, run Linux, retro games

The Sipeed Tang Nano 20K is a low-cost FPGA development board based on Gowin GW2AR-18 FPGA with 20,736 logic cells and 64Mbit RAM, which coupled with 64MBit QSPI flash provides enough resources to simulate a 32-bit RISC-V core booting Linux or playing retro games in an emulator. The FPGA board comes with a USB-C port for power and to load the FPGA bitstream through a BL616 microcontroller that also acts as a USB to serial chip, an HDMI port and an RGB LCD interface for video output, two user buttons, and two rows GPIOs to connect peripherals such as gamepads (through adapters). Sipeed Tang Nano 20K specifications: FPGA – Gowin GW2A-LV18QN88C8I7 with 20,736 logic units (LUT4) 15,552 flip-flops (FF) RAM 41,472 shadow SRAM (S-SRAM) 828K block SRAM (B-SRAM) Numbers of B-SRAM – 46 64Mbit 32-bit SDR SDRAM 48x 18×18 multipliers 2x PLLs 8x I/O Bank Onboard debugger – Bouffalo Labs […]

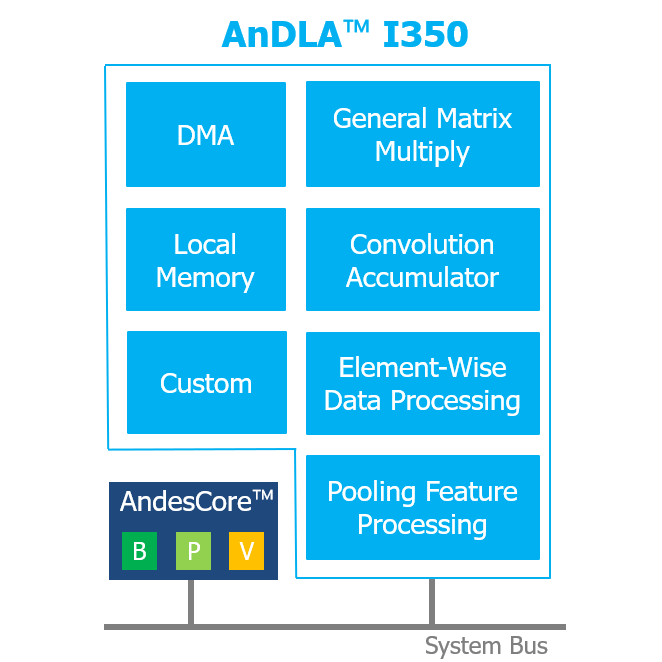

AndesAIRE AnDLA I350 AI/ML IP block is configurable from 64 GOPS to 8TOPS for Edge AI SoCs

Andes Technology has just announced the AndesAIRE product line, where AndesAIRE stands for Andes AI Runs Everywhere, comprised of the AndesAIRE AnDLA I350 (Andes Deep Learning Accelerator) AI/ML hardware accelerator intellectual property (IP) and the AndesAIRE NN SDK with neural network software tools and runtimes. AndesAIRE AnDLA I350 AnDLA I350 specifications: Configurable MACs from 32 to 4096 (INT8) Maximum performance – 8 TOPS at 1GHz Configurable local memory – 16KB to 4MB Multi-dimension DMA Four 64-bit AXI bus interfaces NN type – CNN inference NN models Image and Video: AlexNet, VGG-16/19, MobileNet-v1/v2/v3, ResNet-8/50, Tiny YOLO v1/v2, YOLO v1/v2/v3/v4/v5, SSD MobileNet v1/v2, Inception v2, EfficientNet-lite, MobileFaceNet, BlazeNet Speech/Voice and audio: LSTM, RNN, GRU Operators: Conv2d, depthwise convolution, pointwise convolution, transpose convolution, dilated convolution, element-wise (add, sub, mul), fully-connected, activation (ReLU, leaky ReLU, sigmoid, Tanh, ReLU6, SiLU), pooling (max, ave), upsample, concatenation, batch normalization, channel padding Operator fusion NHWC data format The IP […]

Lichee Pi 4A RISC-V SBC takes on Raspberry Pi 4 with TH1520 processor

Lichee Pi 4A is a single board computer (SBC) powered by Alibaba T-Head TH1520 quad-core RISC-V Xuantie C910 processor @ 2.0 GHz with an Imagination GPU and a 4 TOPS NPU for AI that can compete against the Raspberry Pi 4 in terms of performance and features. We previously mentioned the Lichee Pi 4A (LPi4A) in our article about the Sipeed LM4A RISC-V system-on-module, but at the time we only had some benchmarks for the board and no photos and specifications about the SBC. Sipeed has now released photos, published detailed specifications, and is taking orders for the board. So let’s have a closer look. Lichee Pi 4A specifications against the ones for Raspberry Pi 4. The TH1520 used to be advertised at up to 2.5 GHz, but it seems to have now come down to 2.0 GHz. Software support will include Debian, OpenWrt, and Android which should then […]

Linux 6.3 release – Notable changes, Arm, RISC-V and MIPS architectures

Linux Torvalds has just announced the release of Linux 6.3 on the Linux Kernel Mailing List (LKML): It’s been a calm release this time around, and the last week was really no different. So here we are, right on schedule, with the 6.3 release out and ready for your enjoyment. That doesn’t mean that something nasty couldn’t have been lurking all these weeks, of course, but let’s just take things at face value and hope it all means that everything is fine, and it really was a nice controlled release cycle. It happens. This also obviously means the merge window for 6.4 will open tomorrow. I already have two dozen pull requests waiting for me to start doing my pulls, and I appreciate it. I expect I’ll have even more when I wake up tomorrow. But in the meantime, let’s enjoy (and test) the 6.3 release. As always, the shortlog […]